エイアールエム リミテッドにより出願された特許

41 - 50 / 85

通信チャネルを介して送られるメッセージ間の調停を行うデータ処理装置および方法

【課題】通信チャネルを介して送られるメッセージ間の調停を行うデータ処理装置および方法を得る。

【解決手段】データ処理装置は各々が受取要素に発せられるメッセージを要求するプロセスを実行する複数の処理要素と、これらの処理要素間で共有されそれを介してメッセージが送られる通信チャネルとを有する。調停回路が通信チャネルを介して送られる多数のメッセージ間の調停を行う調停プロセスを実施する。各処理要素はそこで実行中のプロセスに対する進捗データを発し、進捗データはプロセスに対する待ち時間含意を示す。調停制御回路が各処理要素からの進捗データに応答して、優先順位付けデータを発生するために進捗データが示す各プロセスの待ち時間含意を考慮した優先順位付けプロセスを実施する。優先順位付けデータは調停プロセスを制御するために調停回路に出力される。

(もっと読む)

複雑な非線形データの転送制御システム

【課題】複数のデータ発信元と複数のデータ宛先との間でデータ転送を制御するダイレクト・メモリ・アクセス・コントローラを提供する。

【解決手段】複数のデータ発信元および複数のデータ宛先は、複数のチャネルを介してダイレクト・メモリ・アクセス・コントローラと交信し、ダイレクト・メモリ・アクセス・コントローラは、更にメモリおよびプロセッサと交信する。メモリは、複数のチャネルの各々およびプロセッサについて2組の制御データを記憶する。ダイレクト・メモリ・アクセス・コントローラは、前記複数のチャネルの1つ又は前記プロセッサから受信するデータ転送要求に応答して、前記メモリ中に記憶された前記対応する制御データの1組にアクセスし、前記ダイレクト・メモリ・アクセスは、前記アクセスされる制御データに依存して要求される前記データ転送の少なくとも一部を実行する。

(もっと読む)

機密データを処理する処理装置のハイバーネイション

【課題】機密データを処理するデータ処理装置を提供する。

【解決手段】データ処理装置は、処理回路の現在の状態を保持する、少なくともそのいくつかが直列に配置された複数の状態保持セルを含む処理回路、暗号化回路およびハイバーネイト信号入力を含む。データ処理装置は、ハイバーネイト信号入力に受信したハイバーネイト信号に応答して、データ処理装置がパワー・アップされた動作モードから、少なくとも処理回路がパワー・ダウンされる低電力モードへの切り替えを実行する。データ処理装置は、処理回路をパワー・ダウンする前に、処理回路の状態を複数の保持セルから出力し、暗号化回路を使用して出力状態を暗号化し、暗号化された状態を記憶装置に保存する。

(もっと読む)

データ処理装置におけるプロセッサの性能管理

【課題】プロセッサの性能を管理するためのデータ処理装置および方法を提供する。

【解決手段】本方法は必要なプロセッサ性能レベルの指示を受け取るステップと、変調期間を決定するステップと、必要なプロセッサ性能レベルに応じて複数の所定の性能レベルを選択するステップとを含む。各選択された所定のプロセッサ性能レベルについて、所定のプロセッサ性能レベルでプロセッサが動作すべき変調期間の比率を決定するために決定操作が実行され、変調期間中に決定操作により決定された比率に示されるように、選択された所定のプロセッサ性能レベル間でプロセッサを切り替えるために変調操作が実行される。変調期間中に、必要なプロセッサ性能レベルに合致する平均性能レベルが達成可能であり、プロセッサが単に必要なプロセッサ性能レベルより上の所定のレベルで動作した場合に発生する不要なエネルギー消費が回避される。

(もっと読む)

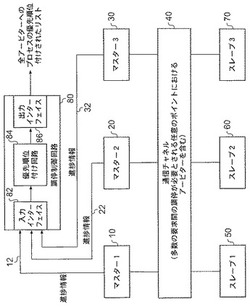

マスタとスレーブとの間でのデータ転送のためのデータ処理装置および方法

【課題】マスタとスレーブとの間でのデータ転送のためのデータ処理装置を提供する。

【解決手段】バスを介して少なくとも1つの受信側と通信するように動作可能な少なくとも1つのイニシエータを備えるデータ処理装置であり、少なくとも1つのイニシエータがバスにデータを送信するための出力ポートとバスからのデータを受信するための入力ポートとを備え、さらにイニシエータ・クロック信号生成器と、イニシエータ出力イネーブル信号生成器と、イニシエータ入力イネーブル信号生成器とを備え、イニシエータ出力イネーブル信号生成器およびイニシエータ入力イネーブル信号生成器が互いに異なる信号を出力するように構成される、データ処理装置。

(もっと読む)

複数の命令セットを用いるデータ処理

【課題】Javaバイトコードに対するハードウエアエグゼキュータを用いてサポートネイティブ命令とJavaバイトコードの双方の実行をサポートする。双方がハードウエアによってサポートされていない場合はJavaバイトコードに対するソフトウエア命令インタープリタを用いてその双方の実行をサポートする。

【解決手段】Javaバイトコードに対する処理を実行するソフトウエア命令インタープリタ内のネイティブ命令のシーケンスは、イネーブルされたハードウエアエグゼキュータが存在していることを検出されたかどうかによって作用が異なるシーケンス終了命令内で終了する。このハードウエアエグゼキュータの存在が検出されると、次のJavaバイトコードが試行される。アクティブなハードウエアエグゼキュータが存在しない場合、次のJavaバイトコードは直接、ソフトウエア命令インタープリタに渡される。

(もっと読む)

乱数発生器

【課題】真にランダムな出力値を生成するのは困難であるがその1つの手段を提供する。

【解決手段】双安定回路(30)であって、0または1を出力する2つの安定状態を有し、また0と1の間の浮動値を出力する平衡準安定状態を有し、スイッチ・オンすると前記準安定状態から前記安定状態の一方に転換し、前記状態は双安定回路(30)のポートの電圧レベルに依存する双安定回路(30)と、双安定回路(30)の前記ポートの電圧レベルを制御するための電圧レベル制御回路(80)と、スイッチ・オンの後で双安定回路(30)が前記準安定状態から前記安定状態の一方に切り換わるのに要する切換え時間を測定するための時間測定回路(50)と、ランダム出力値を出力するシーケンスを実行する制御論理とを含む、真にランダムな出力値を生成する回路(5)。

(もっと読む)

データ処理装置の共有メモリへの書込みアクセス要求の処理

共有メモリへの書込みアクセスを処理するためにデータ処理装置と方法を提供する。データ処理装置は、共有メモリ内のデータへのアクセスを要求するデータ処理操作を実行するための複数の演算処理装置を有し、各演算処理装置は、該演算処理装置によるアクセスのためにデータのサブセットを格納することができる、それに関連付けられたキャッシュを有する。各演算処理装置によりアクセスされるデータが最新であることを保障するために、キャッシュ・コヒーレンシー・プロトコルを用いたキャッシュ・コヒーレンシー論理が提供される。各演算処理装置は、共有メモリ内に格納するためのデータ値を出力する際に、書込みアクセス要求を発行し、その書込みアクセス要求が、関連付けられたキャッシュ及び共有メモリの両方の更新を要求する種類のものである場合に、コヒーレンシー操作が、キャッシュ・コヒーレンシー論理内で開始される。次に、キャッシュ内のデータがコヒーレントを保つことを保障するために、書込みアクセス要求を発行する演算処理装置に関連付けられたキャッシュを含む、複数の演算処理装置に関連付けられた全てのキャッシュに関してコヒーレンシー操作を行う。更に、キャッシュ・コヒーレンシー論理は、書込みアクセス要求の対象となる各データ値に関して、共有メモリに更新要求を発行することができる。このような方法は、特に、複雑度を増すことなく、又、発行元の演算処理装置とそれに関連付けられたキャッシュのアクセスタイミングに影響を与えることなく、書込みアクセス要求の正確な動作を保障するための簡単で効率的な機構を提供する。  (もっと読む)

(もっと読む)

データ処理装置およびトレース信号発生方法

【課題】トレース信号を生成するためのデータ処理装置および方法を提供すること。

【解決手段】データ処理装置は、その動作をトレースしようとする構成要素と、動作を示す構成要素からの入力信号を受信し、トレース受信装置への出力として高優先度および低優先度トレース信号を入力信号から生成するトレース生成ユニットとを含んでいる。トレース生成ユニットは、トレース受信装置からの抑制信号の発行に対して、低優先度トレース信号の発生を抑制し、トレース受信装置がオーバフローするのを防ぐ。さらに、複数のトレースモジュールがデータ処理装置内に設けられた場合には、本発明の実施例では、ファンネル論理によって、複数のトレースモジュールによって生成された個々のトレースストリームを集約した最大帯域幅よりも狭い帯域幅をもつ単一のトレースストリームと組み合わせて、複数のトレースモジュールによってトレース信号を生成できるように構成する。

(もっと読む)

メモリ・アクセス安全性管理

データ処理装置とアクセス要求を発生する方法とが提供される。バスマスターの外部から受け取った信号に応じて、データ処理装置の安全ドメインまたは非安全ドメインのどちらかで動作可能なバスマスターが提供される。バスマスターの通常動作時には固定されている信号が発生される。バスマスター装置が安全ドメインで動作している時に、デフォールトのメモリマップまたは安全に定義されたメモリ領域記述子のどちらかに依存して、安全または非安全アクセスのどちらかであることを示すバスマスター・コアにより発生されたアクセス要求と関係するドメイン指定信号を発生するよう動作する制御論理が提供される。従って、安全ドメインで動作しているバスマスターは、それ自体が安全及び非安全動作間を切り替え可能であることなしに、安全及び非安全アクセスの両方を発生可能である。  (もっと読む)

(もっと読む)

41 - 50 / 85

[ Back to top ]