マイクロン テクノロジー, インク.により出願された特許

71 - 80 / 444

集積回路の製造において複数の導電線を形成する方法、導電線アレイを形成する方法、および集積回路

集積回路の製造において導電線対を形成する方法は、基板上に受けられるダマシン材料にトレンチを形成することを含み、導電性材料34a/35aが、そのダマシン材料を覆ってそしてトレンチ内へ蒸着されてそのトレンチを過充填する。その導電性材料は、少なくともダマシン材料へと戻すように除去されて、そのトレンチ内に残っている導電性材料の少なくともいくらかが残される。エッチングがトレンチ内で導電性材料を通って縦方向に処理されて、トレンチ内に少なくとも第1および第2の導電線の長さの大部分に沿って横断面図において互いにミラー像となる第1および第2の導電線が形成される。他の装いが考えられる。  (もっと読む)

(もっと読む)

マルチポートメモリデバイスおよび方法

マルチポートメモリデバイスの実施形態は、複数のポートと、いくつかが各ポートにネイティブでいくつかが各ポートに非ネイティブである複数のメモリバンクを含んでよい。そのメモリデバイスは、メモリバンクをポートにマッピングすることを示す構成データを記憶する構成レジスタを含んでよい。その構成データに応答して、例えば、ステアリングロジックは、ポートの各々をネイティブメモリバンクの一つまたは全てに、あるいは非ネイティブメモリバンクの一つまたは全てに結合してよい。  (もっと読む)

(もっと読む)

相変化材料の形成方法ならびに相変化メモリ回路の形成方法

ゲルマニウム及びテルルを有する相変化材料を形成する方法で、かかる方法は、基板上にゲルマニウム含有材料を堆積することを含む。かかる材料は、元素形態のゲルマニウムを含む。気体テルル含有前駆体が、ゲルマニウム含有材料に流れ込み、テルルが気体前駆体から除去されて、前記ゲルマニウム含有材料内で元素形態のゲルマニウムと反応して、前記基板上に相変化材料のゲルマニウム・テルル含有化合物を形成する。その他の実施態様も開示される。 (もっと読む)

いくつかのコマンドを処理するためのメモリコントローラ、メモリシステム、ソリッドステートドライブ、および方法

本開示は、メモリコントローラのための方法および装置を含む。1つ以上の実施形態において、メモリコントローラは、複数のバックエンドチャネルと、複数のバックエンドチャネルに通信可能に結合されるコマンドキューと、を含む。コマンドキューは、ホストから受信されるホストコマンドを保持するように構成される。回路は、コマンドキュー内のいくつかのホストコマンドに少なくとも応答していくつかのバックエンドコマンドを生成し、いくつかのバックエンドコマンドを複数のバックエンドチャネルのうちのいくつかに分配するように構成される。 (もっと読む)

酸化ストロンチウムルテニウム界面

酸化ストロンチウムルテニウムは、ルテニウム伝導体と酸化ストロンチウムチタン誘電体との間に有効な界面を提供する。酸化ストロンチウムルテニウムの形成は、酸化ストロンチウムを形成するための原子層堆積の使用と、その後の酸化ストロンチウムルテニウムを形成するための酸化ストロンチウムの焼鈍とを含む。酸化ストロンチウムの第1の原子層堆積は水を酸素源として使用して行われ、続いて、その後の酸化ストロンチウムの原子層堆積がオゾンを酸素源として使用して行われる。 (もっと読む)

半導体処理

半導体処理用のデバイス、方法、及びシステムがここで述べられている。半導体処理の幾つかの方法の実施形態は、構造体上にシリコン層を形成することと、シリコン層を通って構造体内に開口部を形成することと、抵抗可変材料がシリコン層上に形成されないように抵抗可変材料を開口部内に選択的に形成することとを含むことができる。 (もっと読む)

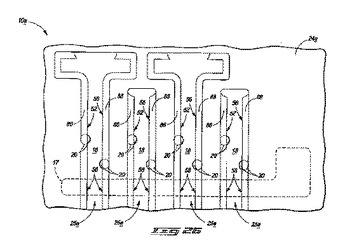

基板上にパターンを形成する方法

基板上にパターンを形成する方法は、基板上での間隔を置いた第一フィーチャの形成を含む。前記間隔を置いた第一フィーチャは対向する側壁を備える。前記間隔を置いた第一フィーチャの前記対向する側壁上に材料を形成する。前記対向する側壁のそれぞれで受けられる、このような材料の部分の組成は、前記対向する側壁のそれぞれの組成とは異なる。前記材料のこのような部分と前記間隔を置いた第一フィーチャの少なくとも一方を緻密化(高密度化)して、前記少なくとも一方を、前記少なくとも一方の他方から離して横方向に移動し、前記対向する側壁のそれぞれと前記材料のこのような部分との間に空隙空間を形成する。  (もっと読む)

(もっと読む)

コンフィギュラブルな帯域幅メモリ・デバイスおよび方法

たとえばメモリ・ダイのスタックおよび装着された論理ダイを含むようなメモリ・デバイス、および方法が記載されている。記載されている方法およびデバイスは、メモリ・ダイのスタックのうち選択された部分に帯域幅を構成することを提供する。付加的な装置、システム、および方法が開示されている。 (もっと読む)

マスクを使用せずに導電性ビアに対して裏面位置合わせを行うことによる半導体構成部品の製造方法

半導体構成部品(90)を製造する方法が、回路面(54)と、裏面(56)と、導電性ビア(58)とを有する半導体基板(52)を提供するステップと、導電性ビア(58)の端子部分(76)を露出するために、基板(52)の一部分を裏面(56)から除去するステップと、端子部分(76)を封入するポリマー層(78)を裏面(56)に堆積するステップと、次いで、ポリマー層(78)および端子部分(76)の端部を平坦化して、ポリマー層(78)に埋め込まれた自己整合導体を形成するステップとを含む。導電性ビア(58)に電気的に接触させて、端子接点(86)や裏面再分配導体(88)等の追加の裏面要素を形成することもできる。半導体構成部品(90)は、半導体基板(52)と、導電性ビア(58)と、およびポリマー層(78)に埋め込まれた裏面導体とを有する。積重ね半導体構成部品(96)が、電気的に互いに通じる位置の整合した導電性ビア(58)を有する複数の構成部品(90-1、90-2、90-3)を有する。  (もっと読む)

(もっと読む)

共に結合された2つ以上の基板から形成された電子デバイス、電子デバイスを備える電子システム、及び、電子デバイスの製造方法

電子デバイスは、第1の基板及び第2の基板を備える。第1の基板は、第1の基板の少なくとも一部を介して相互に少なくとも実質的に平行な複数の導電性トレースを含む回路を備える。複数のボンドパッドは、第1の基板の表面上に配置されるとともに、複数の導電性トレースの少なくとも2つの上に延在する幅を持つ。複数のビアは、少なくともいくつかの導電性トレースの隣接部から複数のボンドパッドまで延在する。第2の基板は、第1の基板に結合されるとともに、複数の導電性バンプを有する第1の基板上の複数のボンドパッドに接続される回路を備える。更に、メモリデバイスと、電子デバイス及びメモリデバイスを形成する関連方法とが開示され、同様に電子システムも開示されている。 (もっと読む)

71 - 80 / 444

[ Back to top ]