マイクロン テクノロジー, インク.により出願された特許

41 - 50 / 444

サイリスタベースメモリセル、デバイス及びそれらを含むシステム、そしてそれらを形成する方法

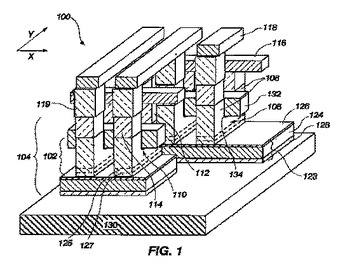

半導体デバイスは、複数のサイリスタベースメモリセルを含み、各々は、4F2のセルサイズを有し、そしてそれらの形成方法が提供される。前記複数のサイリスタベースメモリセルの各々は、垂直に重なる代替ドープされた領域を有するサイリスタ、と制御ゲートを含む。前記制御ゲートは、前記サイリスタの1つ又はそれ以上と電気的に結合されてもよく、そして電圧源に実施可能な接続がなされてもよい。前記複数のサイリスタベースメモリセルは、カソード又はデータ線として機能する伝導ストラップ上のアレイ内に形成されてもよい。システムは、相補型金属酸化膜半導体(CMOS)デバイスのような1つ又はそれ以上のメモリアクセスデバイス又は従来の論理デバイスを有する半導体デバイスを集積することによって形成されてもよい。  (もっと読む)

(もっと読む)

浮遊ボディセル、浮遊ボディセルを含むデバイス、ならびに浮遊ボディセルの形成方法。

バックゲート上に配置される浮遊ボディセルのアレイと、バックゲートから間隔の開いた浮遊ボディセルのソース領域およびドレイン領域と、を含む浮遊ボディセル構造。浮遊ボディセルは、ピラーの間に伸長するチャネル領域を有する大量の半導電性材料を各々含み、ピラーは、U形状トレンチなどの間隙によって分離されうる。アレイの浮遊ボディセルは、別のゲートに電気的に結合され、別のゲートは、大量の半導電性材料の側壁上に配置されてもよいし、大量の半導電性材料の間隙内に配置されてもよい。浮遊ボディセルデバイスを形成する方法も開示される。  (もっと読む)

(もっと読む)

セミコンダクタ・メタル・オン・インシュレータ構造、斯かる構造の形成方法、及び斯かる構造を含む半導体装置

セミコンダクタ・メタル・オン・インシュレータ(SMOI)構造を製造する方法は、第1の半導体基板上に絶縁体材料を含むアクセプターウェーハを形成することと、第2の半導体基板上に導電材料及びアモルファスシリコン材料を含むドナーウェーハを形成することと、アクセプターウェーハの絶縁体材料にドナーウェーハのアモルファスシリコン材料を結合させることとを含む。斯かる方法から形成されるSMOI構造はまた、斯かるSMOI構造を含む半導体装置としても開示される。 (もっと読む)

N極性を有する発光ダイオードおよび関連する製造方法

N極性を有する発光ダイオード(「LED」)および関連する製造方法が本明細書に開示される。一実施形態では、基板材料を有する基板上に発光ダイオードを形成するための方法は、基板の表面上に基板材料の窒化産物を形成することなく、基板の表面に少なくとも近接して、窒素リッチな環境を形成することを含む。本方法はまた、窒素リッチな環境を有する基板の表面上に、窒素極性を有するLED構造を形成することを含む。 (もっと読む)

メムキャパシタ・デバイス、電解効果トランジスタ・デバイス、不揮発性メモリ・アレイ、および、プログラミング方法

メムキャパシタ・デバイスが、相対する導電性電極の対を有する。これら相対する導電性電極の対の間に、誘電体内に移動性ドーパントを含む半導体材料と、移動性ドーパント・バリア誘電材料とが受け入れられる。これら半導体材料とバリア誘電材料とは、少なくとも1つの異なる原子元により少なくとも特徴付けられる互いに異なる組成である。半導体材料およびバリア誘電材料のうちの一方は、これらのうちの他方よりも、電極の対のうちの一方のより近くに位置する。半導体材料およびバリア誘電材料のうちの他方は、これらのうちの一方よりも、電極の対のうちの他方のより近くに位置する。電解効果トランジスタ、メモリ・アレイ、方法を含めて、他の実現例も開示する。 (もっと読む)

クロスポイントメモリセル、不揮発性メモリアレイ、メモリセルの読み出し方法、メモリセルのプログラミング方法、メモリセルへの書き込み方法およびメモリセルからの読み出し方法、ならびにコンピュータシステム。

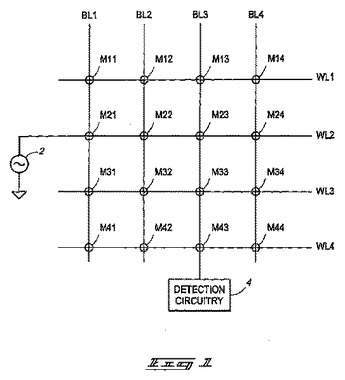

クロスポイントメモリセル、不揮発性メモリアレイ、メモリセルを読み出す方法、メモリセルをプログラミングする方法、メモリセルへの書き込み方法およびメモリセルからの読み出し方法が記述される。一実施形態においては、クロスポイントメモリセルは、第一の方向に伸長するワード線と、第一の方向とは異なる第二の方向に伸長するビット線とを含み、ビット線およびワード線は、お互いに物理的に接触することなく交差する。クロスポイントメモリセルは、そのように交差する位置でワード線およびビット線の間に形成されるキャパシタを含む。キャパシタは、ワード線からビット線へと流れる直流電流およびビット線からワード線へと流れる直流電流を妨げるように構成された誘電体材料を含む。  (もっと読む)

(もっと読む)

固体照明デバイスおよび関連する製造方法。

本明細書において、固体照明デバイスおよび関連する製造方法を開示する。一実施形態において、固体照明デバイスは、N型窒化ガリウム(GaN)材料、N型GaN材料から離間したP型GaN材料、ならびに直接N型GaN材料およびP型GaN材料の直接間にある窒化インジウムガリウム(InGaN)材料を備える発光ダイオードを含む。N型GaN材料、InGaN材料、およびP型GaN材料のうちの少なくとも1つは、非平面を有する。 (もっと読む)

相変化メモリアレイのための方法

相変化メモリアレイを操作する方法を開示する。方法は、相変化メモリアレイに書き込まれるパターンを決定することと、パターンに従って、2つまたはそれ以上の適切なリセットシーケンスを相変化メモリアレイ上で実行し、相変化メモリアレイにパターンを書き込むことと、を含む。別の方法は、相変化メモリアレイ上でセットシーケンスを実行することと、相変化メモリアレイの適切な読み出しを実施し、セットシーケンスの実行から得られるパターンを取得することと、を含む。 (もっと読む)

適応型コンテンツ・インスペクション

適応型コンテンツ・インスペクションを含む方法及び装置が提供される。一実施形態では、コンテンツ・インスペクション・プロセッサは、入力データに関して情報を識別するとともに、その情報をホストコントローラに提供してもよい。ホストコントローラは、検索条件または他のパラメータを適応させるとともに、適応させたパラメータをコンテンツ・インスペクション・プロセッサに提供してもよい。他の実施形態は、リザルトデータがコンテンツ・インスペクション・プロセッサにフィードバックされるように、統合型フィードバックを有するコンテンツ・インスペクション・プロセッサを含んでもよい。リザルトデータは、コンテンツ・インスペクション・プロセッサに提供される前に処理されてもよい。 (もっと読む)

パターン認識プロセッサにおける消費電力を低減させるための方法及び装置

パターン認識プロセッサ(14)の消費電力を低減するための装置及び方法が提供される。電力制御回路(98)は、パターン検索中にブロック(96)の選択的アクティブ化及び非アクティブ化を可能にするために、プログラムされたステートマシンのブロック(96)に結合されてもよい。ブロック(96)は、パターン検索がもはやそのブロック(96)でアクティブではない場合は、非アクティブ化され、パターン検索で必要なときに、アクティブ化されてもよい。更に、ブロック(96)は、検索対象のデータストリーム(12)の識別子に基づいて非アクティブ化されてもよい。プログラムされたステートマシンに使用されない余剰ブロック(96)は、メモリ周期中にリフレッシュされないように無効にされてもよい。 (もっと読む)

41 - 50 / 444

[ Back to top ]