Fターム[2C162AH82]の内容

電磁気プリンタ及び光プリンタ (19,948) | 共通の構成(電極、駆動素子関係) (948) | 駆動素子 (416) | 配置、レイアウト (112) | IC長手方向が記録素子列に並行 (52)

Fターム[2C162AH82]に分類される特許

1 - 20 / 52

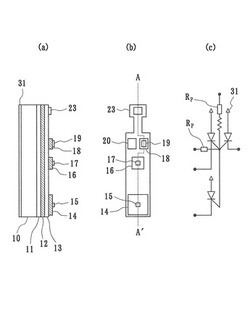

自己走査型発光素子アレイ

【課題】転送速度を改善しながら正常な転送を実現できる自己走査型発光素子アレイを提供する。

【解決手段】シフト部/発光部の島とゲート負荷抵抗の島とを分離せずに一体化する。ゲート負荷抵抗用の電極が無くなるので、ゲート負荷抵抗の電極23とp型ゲート層13との間に存在した接触抵抗が無くなる。その結果、ゲート抵抗が小さくなり、転送速度が増大する。

(もっと読む)

プリンタヘッド

【課題】 デバイス性能の改善が可能なプリンタヘッドを提供する。

【解決手段】 絶縁基板と、前記絶縁基板上において、ライン状に配置された複数の陽極と、前記陽極上に配置された有機発光層と、前記有機発光層上に配置された陰極と、を備えた有機EL素子と、前記有機EL素子を駆動するための駆動回路と、を備え、前記駆動回路は、前記絶縁基板上に配置され、前記有機EL素子を挟んで対向配置された第1駆動回路及び第2駆動回路を有することを特徴とするプリンタヘッド。

(もっと読む)

露光ヘッド、画像形成装置

【課題】発光チップと結像光学系との間に遮光部材を配設した露光ヘッドにおいて、遮光部材のクロストーク抑制機能を効果的に発揮させつつ、遮光部材との接触に起因したボンディングワイヤーの損傷を抑制可能とする技術を提供する。

【解決手段】第2の方向の一方側から発光チップに接続されて、第1発光素子および第2の発光素子に駆動信号を供給するボンディングワイヤーを備え、第1の発光素子が発光した光は開口を通過して結像光学系に入射し、開口の第2の方向の一方側のエッジから第1の発光素子までの第2の方向への距離L1と、開口の第2の方向の他方側のエッジから第1の発光素子までの第2の方向への距離L2とが、関係式L2>L1を満たす。

(もっと読む)

露光ヘッド、画像形成装置

【課題】発光チップと結像光学系との間に遮光部材を配設した露光ヘッドにおいて、遮光部材のクロストーク抑制機能を効果的に発揮させつつ、遮光部材との接触に起因したボンディングワイヤーの損傷を抑制可能とする技術を提供する。

【解決手段】遮光部材は、第1の遮光板と第2の遮光板とを有する遮光部材を備え、第1の遮光板は第1の発光素子から第1の結像光学系に向かう第1の開口を備え、第2の遮光板は第1の開口を挟んでボンディングワイヤーに対向し、基板から第2の遮光板までの距離t1と、基板から第1の遮光板までの距離t2とが、関係式t1>t2を満たす。

(もっと読む)

露光ヘッド、画像形成装置

【課題】制御回路が実装されたFPCを発光素子が配設されたヘッド基板に接続した構成において、FPCとヘッド基板との接続部分の破損を抑制する。

【解決手段】発光素子が配設されたヘッド基板と、ヘッド基板を支持する支持部材と、ヘッド基板に接続されたフレキシブルプリント基板と、フレキシブルプリント基板に配設されて、発光素子の発光を制御する制御回路と、フレキシブルプリント基板を支持部材に固定する固定部材と、を備える。

(もっと読む)

光プリントヘッドおよび画像形成装置

【課題】パワーMOSトランジスタの搭載を不要とし、光プリントヘッドの小型化、低コスト化を図る発光素子アレイ、駆動装置、画像形成装置を提供する。

【解決手段】本発明の光プリントヘッドは、第1端子と、第2端子と、前記第1端子と前記第2端子との間の導通を制御するための制御端子とを各々有し、前記第1端子と前記第2端子との間に電流が流れることにより発光する複数の発光素子と、前記複数の発光素子の各々に対応して設けられ、前記発光素子の前記第1端子と前記第2端子との間に電流を流すことにより発光させる駆動回路と、前記複数の発光素子の各々に対応して設けられ、前記発光素子の前記制御端子と一端が接続され、双方向に電圧降下を発生させる双方向電圧降下発生回路と、複数の前記双方向電圧降下発生回路の他端を共通に接続する共通母線と、前記共通母線に対して、前記発光素子の制御端子に与える制御信号を出力するバッファ回路とを備えたことを特徴とするものである。

(もっと読む)

発光装置および電子機器

【課題】発光装置を小型化する。

【解決手段】可撓性の基板12Aは、第1部分21と第2部分22と第3部分23とに区分される。第1部分21には複数の発光素子32が形成され、第2部分22には各発光素子32を駆動する回路部34が形成される。基板12Aは、第2部分22および第3部分23が第1部分21に対して同じ方向に折り曲げられた状態で筐体40Aに支持される。第1部分21の背面側には、第1部分21を平面状に維持するための固定部材60Aが配置される。

(もっと読む)

発光サイリスタ、発光素子アレイ、発光装置および画像形成装置

【課題】 ベース層のキャリア濃度および厚み寸法を大きく設定することなく、発光強度に対する電流増幅率βの影響を抑制することのできる発光サイリスタ、発光素子アレイ、発光装置および画像形成装置を提供することである。

【解決手段】 発光サイリスタは、基板上に第1半導体層、第1半導体層と反対導電型の第2半導体層、第1半導体層と同じ導電型の第3半導体層、および第1半導体層と反対導電型の第4半導体層がこの順に積層されており、第3半導体層のバンドギャップは、第2半導体層のバンドギャップと略同一、かつ、第1および第4半導体層のバンドギャップより狭幅であり、第3半導体層は、基板側の第1領域と基板と反対側の第2領域とからなり、かつ、第1領域の不純物濃度は1×1016(cm−3)未満である。

(もっと読む)

駆動回路、光プリントヘッド及び画像形成装置

【課題】良好な印刷品位を得ると共に、チップ面積を削減する。

【解決手段】LED駆動回路を構成する駆動トランジスタのX軸方向(LEDアレイ方向)への配列幅は、駆動電流出力端子PDの配列ピッチP1の略2倍に設定されると共に、主駆動トランジスタであるPMOS122−1,122−2の形状が略L字状になっており、2個の駆動電流出力端子PD1,PD2の駆動に係わる2個の駆動部123−1,123−2が回転対称に配置され、全体として矩形形状をなすように構成されている。そのため、複数のLED駆動回路間での駆動電流のばらつきが改善され、LEDを備えたプリンタにおいては、良好な印刷品位を得ることができる。その上、駆動トランジスタのY軸方向(X軸に対して直交する方向)への占有サイズを減少させることができ、チップ面積を削減できる。

(もっと読む)

ラインヘッドおよび画像形成装置

【課題】幅が狭く、高精度な露光処理を実現することができるラインヘッドを提供すること、また、高品位な画像を得ることができる画像形成装置を提供すること。

【解決手段】ラインヘッド13は、第1の基板71と、第1の基板71に配設された発光素子72と、第1の基板71から引き出されるように設けられたフレキシブルプリント基板である配線ユニット9と、配線ユニット9に配設され、発光素子72を駆動する駆動回路822の少なくとも一部を構成する半導体素子であるドライバIC85と、第1の基板71を放熱する第1の放熱部材である支持部材6と、支持部材6とは別体として形成され、ドライバIC85を放熱する第2の放熱部材である放熱部材70とを有する。

(もっと読む)

ラインヘッドおよび画像形成装置

【課題】組み立て性に優れ、幅が狭く、画像形成装置を小型で安価なものとすることができるラインヘッドを提供すること、また、小型で安価な画像形成装置を提供すること。

【解決手段】ラインヘッド13は、支持部材6が、発光基板ユニット7の第1の基板71が搭載される基板搭載部61と、回路基板ユニット8の第2の基板81を介して対向するように基板搭載部61から延びる1対の脚部62とを有し、発光基板ユニット7と回路基板ユニット8とを電気的に接続する配線ユニット9は、フレキシブルプリント基板であり、第1の基板71および第2の基板81の互いの幅方向での端部同士を接続するように設けられているとともに、第2の基板82の一端部側から他端部側へ向けて折り返されている。

(もっと読む)

半導体複合装置、光プリントヘッド、及び画像形成装置

【課題】小型化及び材料コストの低減を図ることができる半導体複合装置を提供する。

【解決手段】半導体複合装置は、基板と、内部に一つだけ半導体素子を有する半導体薄膜であって、基板上に設けられた10μm以下の厚さでシート状のLEDエピタキシャルフィルム103と、集積回路及び第1の端子領域を有し、基板上に設けられた10μm以下の厚さでシート状の集積回路薄膜104と、LEDエピタキシャルフィルム103の半導体素子上から基板の表面を経由して集積回路薄膜104の第1の端子領域上に至る領域に設けられ、LEDエピタキシャルフィルム103の半導体素子と集積回路薄膜104の第1の端子領域とを電気的に接続する薄膜の個別配線層105と、個別配線層105下の個別配線層のコンタクト領域以外の部分に設けられた層間絶縁膜とを有する。

(もっと読む)

半導体装置、光プリントヘッド、及び画像形成装置

【課題】小型化及び材料コストの低減を図ることができる半導体装置を提供する。

【解決手段】半導体装置は、端子領域を備えた基板101と、内部に一つだけ半導体素子を有する半導体薄膜であって、基板101上に複数枚設けられた10μm以下の厚さのシート状のエピフィルム191と、エピフィルム191の半導体素子上から基板101の端子領域上に至る領域に設けられ、半導体素子と基板101上の端子領域とを電気的に接続する薄膜の個別配線層107aと、個別配線層107a下の個別配線層のコンタクト領域以外の部分に設けられた層間絶縁膜とを有する。

(もっと読む)

半導体集積回路及び電子回路装置

【課題】半導体集積回路に応力が加わった場合において、その応力による半導体集積回路内のMOSトランジスタの電気的特性の変動を抑える。

【解決手段】出力MOSトランジスタ1Tのゲート電極13Aは、半導体基板10の長辺方向D1(即ち長辺に平行な方向)に沿って延びている。このゲート電極13Aの両側には、ソース領域、ドレイン領域(共に不図示)が配置され、それらの間にチャネル領域(不図示)が形成されている。また、各制御回路1Lに含まれる各制御MOSトランジスタ(不図示)についても、ゲート電極13Bを半導体基板10の長辺方向D1に沿って延びるように構成してもよい。

(もっと読む)

発光サイリスタ、発光素子アレイ、画像形成装置、ならびに同一基板上に発光サイリスタおよび半導体抵抗素子を形成する方法

【課題】 680nm〜770nm程度の波長の光を出射可能であって、発光の制御性を向上することができる発光サイリスタ、この発光サイリスタを備える発光素子アレイ、ならびに画像形成装置を提供する。

【解決手段】 NPNP構造を有する第1〜第4半導体層3〜6を有する発光サイリスタ1の第3半導体層5が、一方の導電型のAlGaAsだけによって形成されるのではなく、一方の導電型のAlGaAsによって形成される第1および第2領域15,16の間に、一方の導電型のInGaPによって形成される第3領域17を有し、この第3領域17にゲート電極11が接続されるので、酸化しにくいInGaPとゲート電極11とを安定してオーミック接触させることができる。したがって、ゲート電極11と第3半導体層5との接続部位における電圧−電流特性が線形性を有し、発光の制御性が向上する。

(もっと読む)

駆動装置、LEDアレイ、LEDヘッド、及びこれらを備えた画像形成装置

【課題】、発光素子の配列方向とは垂直方向の小型化を図ることで、駆動装置、LEDアレイ、LEDヘッド、及びこれらを備える画像形成装置の小型化を図ることを目的とする。

【解決手段】このLEDアレイは、等間隔に配列されたN個(N:4の倍数)のLED素子を4個の群に分割して時分割駆動させるLEDアレイにおいて、LED素子の配列方向における任意の方向から(1+n×4)番目(n:整数)、(2+n×4)番目、(3+n×4)番目、(N−n×4)番目にある各LED素子群と、配線材を介して接続されたカソード端子パッドK21〜K24を備え、これらカソード端子パッドK21〜K24が、配列されたLED素子に沿って配列された電極パッドアレイを形成することを特徴とする。

(もっと読む)

ラインヘッドおよびこれを用いた画像形成装置

【課題】発光源が2次元状に配列されて駆動回路と接続されている場合の結線処理を円滑に行うと共に、画像形成を合理的に行えるラインヘッドおよび画像形成装置の提供。

【解決手段】発光素子を感光体の軸方向(X方向)および感光体の回動方向(Y方向)にそれぞれ複数配して発光素子グループBを形成し、当該発光素子グループをY方向にR、S、Tの複数行設けて発光源を2次元状に配列する。Ca〜Ccは各発光素子を駆動する駆動回路で、CaはGaの区域、CbはGbの区域、CcはGcの区域の発光素子グループと結線される。各駆動回路は、Y方向に3行形成された発光素子行の2行または1行と接続される。

(もっと読む)

露光ヘッド、露光ヘッドの制御方法、画像形成装置

【課題】発光素子に接続される配線の自由度を向上させる技術を提供する。

【解決手段】結像光学系LSと、結像光学系LSにより結像される光を発光する第1の発光素子Ea1〜Ea4、Eb1〜Eb4と、結像光学系LSにより結像される光を発光する第2の発光素子Ec5〜Ec8、Ed5〜Ed8と、第1の発光素子Ea1〜Ea4、Eb1〜Eb4に配線WLを介して接続される第1のTFT回路TCa1〜TCa4、TCb1〜TCb4と、第2の発光素子Ec5〜Ec8、Ed5〜Ed8に配線WLを介して接続される第2のTFT回路TCc5〜TCc8、TCd5〜TCd8とを備え、第1のTFT回路TCa1〜TCa4、TCb1〜TCb4と第2のTFT回路TCc5〜TCc8、TCd5〜TCd8との間に、第1の発光素子Ea1〜Ea4、Eb1〜Eb4および第2の発光素子Ec5〜Ec8、Ed5〜Ed8が配設されてる。

(もっと読む)

発光装置、光プリントヘッドおよび画像形成装置

【課題】発光サイリスタのゲート端子電位を過剰に低下させることなく、無効なゲート電流を削減して発光出力の増加を図る。

【解決手段】発光サイリスタd1を駆動するバッファ回路101に、PMOSトランジスタ112、113を設ける。サイリスタd1を発光させる場合、PMOSトランジスタ112はオフ、PMOSトランジスタ113はオンとなって、発光サイリスタd1のゲート端子Gの電位はPMOSトランジスタの閾値電圧Vtに略等しい電位になる。これにより、オン状態にあるサイリスタd1のアノード端子から供給される駆動電流は、NPNトランジスタ62のコレクタやPNPトランジスタ61のコレクタ側に流れる電流Ik2、Ik1となって、ゲート端子からバッファ回路101を介してグランドへ至る電流Igは生じない。

(もっと読む)

ラインヘッドおよび該ラインヘッドを用いた画像形成装置

【課題】発光素子グループに接続される配線を幅方向の両側に引き出すことを可能として、発光素子に接続される配線の自由度を向上する技術を提供する。

【解決手段】ヘッド基板と、第1発光素子を有する第1発光素子群と、第2発光素子を有する第2発光素子群と、ヘッド基板に配設され、第1発光素子と電気的に接続される第1配線と、ヘッド基板に配設され、第2発光素子と電気的に接続される第2配線と、ヘッド基板の一方側に配設され、第1配線と電気的に接続される第1接続部と、ヘッド基板の他方側に配設され、第2配線と電気的に接続される第2接続部とを備えている。

(もっと読む)

1 - 20 / 52

[ Back to top ]