Fターム[2C162AH85]の内容

電磁気プリンタ及び光プリンタ (19,948) | 共通の構成(電極、駆動素子関係) (948) | 駆動素子 (416) | 記録素子との接続方法 (98) | パターン上に直接接続 (31)

Fターム[2C162AH85]に分類される特許

1 - 20 / 31

露光ヘッド、画像形成装置

【課題】発光素子とこれを駆動する駆動部を同一の基板に設けた構成において、当該基板を支持する透明基板の電気配線と駆動部との電気的な短絡を防止する。

【解決手段】配線が配された光透過性の第1の基板と、発光素子を有するとともに当該発光素子を第1の基板に向けた状態で第1の基板に支持される第2の基板と、第2の基板に配されて発光素子を駆動する駆動部と、第1の基板の配線と第2の基板の駆動部との間に配される絶縁部材と、を備える。

(もっと読む)

露光ヘッド、画像形成装置

【課題】発光素子と駆動回路を同一の基板に設けた構成において、配線スペースを確保しつつ露光ヘッドのスリム化を可能とする技術を提供する。

【解決手段】有機ELを光透過性の封止部材で封止するとともに、有機ELの一方側に配された第1の端子および他方側に配された第2の端子を有する第1の基板と、第1の端子あるいは第2の端子と有機ELの間で第1の基板に配されて、有機ELを駆動して発光させる駆動部と、第1の端子に接続される第3の端子および第2の端子に接続される第4の端子を有して第1の基板を支持するとともに、有機ELが発光して封止部材を通過した光が透過する第2の基板と、第2の基板の法線方向から見て第3の端子あるいは第4の端子と有機ELの間で第2の基板に配される配線と、を備える。

(もっと読む)

発光ダイオードプリントヘッドの交互的マトリクス駆動方法とシステム

【課題】解像度を高くしても、高い印刷速度を持続させるヘッドの駆動方法。

【解決手段】線形アレイに配置される複数のチップと、各チップ上の、各々第1及び第2のチャネルへ接続される個々の複数の第1及び第2のマトリクスドライバと、各チップ毎の第1の発光ダイオード(LED)グループとを含むプリントヘッド。第1のLEDグループは各々、個々の第1のマトリクスドライバへ接続される第1の数のLEDを有する第2のLEDグループと、個々の第2のマトリクスドライバへ接続される第1の数のLEDを有する第3のLEDグループとを含む。各第1のLEDグループにおけるLEDはスタッガード配列で配置され、かつ個々の複数の第1及び第2のマトリクスドライバは各々第2及び第3のLEDグループ内のLEDを順次起動するためのものである。

(もっと読む)

露光ヘッド、画像形成装置

【課題】発光素子を十分な光量で発光させて、良好な露光を実現可能とする技術を提供する。

【解決手段】第1の方向に第1のピッチで配設された発光素子と、発光素子に対して第1の方向に直交もしくは略直交する第2の方向の一方側で、第1のピッチより広い第2のピッチで第1の方向に配設されて、発光素子を発光させる駆動回路と、を備える。

(もっと読む)

露光ヘッド、画像形成装置

【課題】制御回路が実装されたFPCを発光素子が配設されたヘッド基板に接続した構成において、FPCとヘッド基板との接続部分の破損を抑制する。

【解決手段】発光素子が配設されたヘッド基板と、ヘッド基板を支持する支持部材と、ヘッド基板に接続されたフレキシブルプリント基板と、フレキシブルプリント基板に配設されて、発光素子の発光を制御する制御回路と、フレキシブルプリント基板を支持部材に固定する固定部材と、を備える。

(もっと読む)

発光装置および電子機器

【課題】素子群の両側に配置された駆動回路の特性がばらつくことを抑制する。

【解決手段】X方向に沿って配列する複数の発光素子14からなる素子群Gと、素子群Gから見てX方向の負側に配置されて素子群Gに属する2以上の第1発光素子14aの各々を駆動する複数の第1駆動回路20aと、素子群Gから見てX方向の正側に配置されて素子群Gに属する2以上の第2発光素子14bの各々を駆動する複数の第2駆動回路20bと、を備え、各第1駆動回路20aに含まれるトランジスタの半導体層のX方向における位置は、各第2駆動回路20bに含まれるトランジスタの半導体層のX方向における位置と同じである。

(もっと読む)

半導体装置、光プリントヘッド、及び画像形成装置

【課題】小型化及び材料コストの低減を図ることができる半導体装置を提供する。

【解決手段】半導体装置は、端子領域を備えた基板101と、内部に一つだけ半導体素子を有する半導体薄膜であって、基板101上に複数枚設けられた10μm以下の厚さのシート状のエピフィルム191と、エピフィルム191の半導体素子上から基板101の端子領域上に至る領域に設けられ、半導体素子と基板101上の端子領域とを電気的に接続する薄膜の個別配線層107aと、個別配線層107a下の個別配線層のコンタクト領域以外の部分に設けられた層間絶縁膜とを有する。

(もっと読む)

半導体集積回路及び電子回路装置

【課題】半導体集積回路に応力が加わった場合において、その応力による半導体集積回路内のMOSトランジスタの電気的特性の変動を抑える。

【解決手段】出力MOSトランジスタ1Tのゲート電極13Aは、半導体基板10の長辺方向D1(即ち長辺に平行な方向)に沿って延びている。このゲート電極13Aの両側には、ソース領域、ドレイン領域(共に不図示)が配置され、それらの間にチャネル領域(不図示)が形成されている。また、各制御回路1Lに含まれる各制御MOSトランジスタ(不図示)についても、ゲート電極13Bを半導体基板10の長辺方向D1に沿って延びるように構成してもよい。

(もっと読む)

露光ヘッド、露光ヘッドの制御方法、画像形成装置

【課題】発光素子に接続される配線の自由度を向上させる技術を提供する。

【解決手段】結像光学系LSと、結像光学系LSにより結像される光を発光する第1の発光素子Ea1〜Ea4、Eb1〜Eb4と、結像光学系LSにより結像される光を発光する第2の発光素子Ec5〜Ec8、Ed5〜Ed8と、第1の発光素子Ea1〜Ea4、Eb1〜Eb4に配線WLを介して接続される第1のTFT回路TCa1〜TCa4、TCb1〜TCb4と、第2の発光素子Ec5〜Ec8、Ed5〜Ed8に配線WLを介して接続される第2のTFT回路TCc5〜TCc8、TCd5〜TCd8とを備え、第1のTFT回路TCa1〜TCa4、TCb1〜TCb4と第2のTFT回路TCc5〜TCc8、TCd5〜TCd8との間に、第1の発光素子Ea1〜Ea4、Eb1〜Eb4および第2の発光素子Ec5〜Ec8、Ed5〜Ed8が配設されてる。

(もっと読む)

発光装置、光プリントヘッドおよび画像形成装置

【課題】発光サイリスタのゲート端子電位を過剰に低下させることなく、無効なゲート電流を削減して発光出力の増加を図る。

【解決手段】発光サイリスタd1を駆動するバッファ回路101に、PMOSトランジスタ112、113を設ける。サイリスタd1を発光させる場合、PMOSトランジスタ112はオフ、PMOSトランジスタ113はオンとなって、発光サイリスタd1のゲート端子Gの電位はPMOSトランジスタの閾値電圧Vtに略等しい電位になる。これにより、オン状態にあるサイリスタd1のアノード端子から供給される駆動電流は、NPNトランジスタ62のコレクタやPNPトランジスタ61のコレクタ側に流れる電流Ik2、Ik1となって、ゲート端子からバッファ回路101を介してグランドへ至る電流Igは生じない。

(もっと読む)

発光装置および画像形成装置

【課題】高輝度でかつ高解像度のラインヘッドを提供する。

【解決手段】画素回路Pにおいて、保持トランジスタ61、OLED素子64、および駆動トランジスタ62がY方向に沿って形成されているので、画素回路PのピッチWを狭くできる。さらに、OLED素子64は千鳥状に配列されているので、長さQをピッチWより長くすることができる。OLED素子64の発光輝度はその面積に依存するので、高輝度かつ高解像度のヘッド部を提供できる。

(もっと読む)

露光装置および画像形成装置

【課題】各露光装置相互間における発光素子の位置合わせを高精度に行う。

【解決手段】列状に配列された複数のLEDが配置されたLED回路基板62の第1面側から、LED回路基板62を加熱する面状ヒータ65が備えられている。

(もっと読む)

電気光学装置、検査方法および電子機器

【課題】複数の集積回路をカスケード接続する信号線の欠陥を容易に検出する。

【解決手段】電気光学装置100は、複数の信号線15を含む配線群L1〜LMを介して相互にカスケード接続されたM個の集積回路C1〜CMを具備する。各集積回路Ci(i=1〜M)は、各信号線15に対応した複数のビットで構成されるテストパターンPTを記憶する記憶回路62と、記憶回路62が記憶するテストパターンPTを配線群Li+1から後段に出力する出力回路45と、配線群Liを介して前段からテストパターンPTを取得する入力回路42と、入力回路42が取得したテストパターンPTと記憶回路62が記憶するテストパターンPTとを比較する比較回路64と、比較回路64による比較の結果を電気光学素子22の駆動によって可視的に出力する駆動回路70とを含む。

(もっと読む)

発光装置および画像形成装置

【課題】例えば環境の変化等が生じた場合であっても、光量むらの発生を抑制する。

【解決手段】LPH14は、128個のLEDを搭載したLEDチップを60個並べて構成されたLEDアレイを実装するプリント基板52と、複数のロッドレンズを2列に整列して構成されたロッドレンズアレイ54とを備える。各LEDの発光光量は、LED個別の光量むらに基づいて設定されたLED補正データと、ロッドレンズのピッチむらに基づいて設定されたレンズ補正データとを用いて補正される。温度変化によってプリント基板52およびロッドレンズアレイ54が伸縮することで生じる位置ずれを考慮し、温度に応じてレンズ補正データを変更する。具体的には、レンズ補正基準データに対し、温度に応じてデータの間引きあるいは追加し、レンズ補正データの作成を行う。

(もっと読む)

電気光学装置および電子機器

【課題】複数のICチップの各々に電位を供給する各配線の交差を削減する。

【解決手段】電気光学素子を駆動する複数のICチップCの各々は、当該ICチップC内で相互に導通する電源端子RAnおよびRBnと、電源端子RAnおよびRBnの外側に配置されて当該ICチップC内で相互に導通する電源端子RA1およびRB1とを含む。ICチップCkの電源端子RBnとICチップCk+1の電源端子RAnとは電源中継線63を介して接続され、ICチップCkの電源端子RB1とICチップCk+1の電源端子RA1とは電源中継線63を介して接続される。ICチップCkの電源端子RA1およびRAnには電源回路34から電源電位VPが供給される。

(もっと読む)

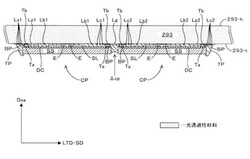

ラインヘッド及び該ラインヘッドを用いた画像形成装置

【課題】高解像度で、しかも小型のラインヘッドおよび該ラインヘッドを装備する画像形成装置を提供する。

【解決手段】複数の発光素子グループ295が2次元配置されるとともに、各発光素子グループ295から射出される光ビームを拡大光学系のマイクロレンズ(結像レンズ)MLにより感光体ドラム表面(被走査面)上に結像している。このため、基板293における発光素子グループ295の配設間隔が広がり、比較的広い隙間領域ARが形成される。そして、各隙間領域ARに駆動回路D295や配線WLが配置されている。したがって、解像度を高めるために発光素子2951の数を増大させたとしても、基板サイズを増大させることなく、該基板293上に十分な駆動回路スペースや配線スペースを確保することができる。

(もっと読む)

発光素子駆動装置及びそれを用いた画像形成装置

【課題】複数の発光素子を光源として有する画像形成装置において、印字速度、印刷速度の更なる高速化を達成する

【解決手段】TFT回路62がガラス基板50に形成され、ソースドライバ61からのソースドライバ信号線がTFT回路62の下縁L側から接続され、ゲートコントローラからの発光制御信号線とプログラム制御信号線が、TFT回路62の上縁U側から接続される。このため、信号線間の容量成分が減少し、素子駆動のプログラム時間が短縮される。

(もっと読む)

半導体複合装置、及びこれらを用いたプリントヘッド並びに画像形成装置。

【課題】LEDチップには上述の様なワイヤボンド用の領域を設ける必要があった為、LEDチップの小型化に伴う材料コストの削減を実行することが極めて困難であった。

【解決手段】第1の基板102上に、所定の回路領域103と、半導体薄膜105を形成し、当該半導体薄膜105は、導電層104と、個別電極108と、導電層115とによって、3端子素子構造を形成することとしている。半導体薄膜105をこの様な構成とすることで、LEDチップを小型化することができると共に、材料コストを削減することができる。

(もっと読む)

有機ELプリントヘッド

【課題】組み立て作業性が良く、製造コストを廉価にすることができ、しかも全体の小型化も可能な有機ELプリントヘッドを提供する。

【解決手段】複数の有機EL発光部31が列状に並ぶようにして基板本体30上に設けられている有機ELプリントヘッド基板3と、各有機EL発光部31において発生した光を目的領域上に集束させるためのレンズアレイ4と、を備えている、有機ELプリントヘッドA1であって、レンズアレイ4は、有機ELプリントヘッド基板3に直接組み付けられていることにより、これらレンズアレイ4と有機ELプリントヘッド基板3とが一体化されている。

(もっと読む)

有機ELプリントヘッド

【課題】複数の有機EL発光部間の隙間に起因して記録媒体に露光不足領域が筋状に発生することを適切に防止または抑制し、記録画像の質を高めることが可能な有機ELプリントヘッドを提供する。

【解決手段】主走査方向xに列状に並ぶようにして複数の有機EL発光部31が基板本体30上に設けられている有機ELプリントヘッド基板3と、主走査方向xに列状に並び、かつ各有機EL発光部31において発生した光を目的領域に集束させるための複数のレンズとを備えている、有機ELプリントヘッドであって、複数の有機EL発光部31と上記複数のレンズとの間には、各有機EL発光部31から進行してきた光を、少なくとも主走査方向に拡散させる光拡散手段6が設けられている。

(もっと読む)

1 - 20 / 31

[ Back to top ]