Fターム[2G003AG18]の内容

個々の半導体装置の試験 (15,871) | 接触部、信号の印加 (5,296) | 素子の選択 (22)

Fターム[2G003AG18]に分類される特許

1 - 20 / 22

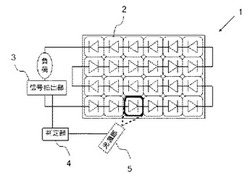

太陽電池の検査方法及び装置

【課題】太陽電池が実際に設置された環境において太陽電池全体としての電流を制約するセルを特定する方法を提供する。

【解決手段】所定の周波数の電流によって駆動される半導体発光素子を光源5とする光でセル2を順次に照射し、太陽電池1の出力電流のその周波数の成分を検出する。出力電流が最小のセルを照射した時にはその周波数の成分が大きく検出されるので、太陽電池全体としての電流を制約するセルを特定することができる。また、照射光を半導体レーザとして、離れた場所からセルを正確に照射できるようにする。

(もっと読む)

太陽電池の欠陥不良検出方法及び装置

【課題】太陽電池の生産工程においてセルをラミネートする前に太陽電池の異常、特にはんだ付け不良を発見する方法及び装置であって、セルよりも小さな単位で異常を発見できるものを提供すること。

【解決手段】セルを分割した評価領域を評価するために、評価領域を含むセルに照射される光の照射量を他のセルよりも小さくし、評価領域に照射される光の照射量を変化させて太陽電池の特性値を測定する。特性値の変化に基づいて評価を行う。評価領域を変更して評価を行うことで、評価結果の異なる部分が異常であると判定することもできる。また、この評価をはんだ付けの後、セルをラミネートする前に行い、半田付け不良を発見して修復することを容易にすることができる。

(もっと読む)

評価装置及び評価方法

【課題】太陽電池セルにおける一部の箇所の電気特性を簡易な構成で評価できる評価装置及び評価方法を得ること。

【解決手段】評価装置は、太陽電池セルの電気特性を評価するための評価装置であって、互いに絶縁されており、前記太陽電池セルにおける異なる接続箇所と電流計測回路とをそれぞれ接続する複数の第1の接続端子と、前記太陽電池セルと電圧計測回路とを接続する第2の接続端子と、前記太陽電池セルにおける接続箇所を切り替えるように、前記複数の第1の接続端子から少なくとも2つの第1の接続端子を選択し、前記少なくとも2つの第1の接続端子を介して前記電流計測回路を前記太陽電池セルに直列に接続させる切替機構とを備えている。

(もっと読む)

太陽光発電パネルの診断装置、遮音壁、建造物用窓ガラス設備、乗物用窓ガラス設備及び太陽光発電パネルの保守管理システム

【課題】太陽光発電パネルの発電状態を自動的に診断して外部の人間に容易に認識させることができる太陽光発電パネルの診断装置を提供する。

【解決手段】一の太陽光発電パネル10の起電力と他の太陽光発電パネル10の起電力との相対的な比較値が許容範囲であるか否かを判定するための判定式と、判定式で用いられる設定係数等を記憶する記憶部31と、判定式と設定係数等に基づき、一の太陽光発電パネル10の起電力と他の太陽光発電パネル10の起電力との相対的な比較値が許容範囲であるか否かを判定し、その比較値が許容範囲外である場合に、判定で起電力の小さい方の太陽光発電パネル10の異常を検出する判定検出部32と、その異常の検出に応じて異常が検出された太陽光発電パネル10の異常を告知する告知手段とを備える太陽光発電パネルの診断装置。

(もっと読む)

半導体試験装置

【課題】電圧印加電流測定時において、測定手法を変更することなく、従来の測定に加えて、1つのDCモジュールでの連続的な電流波形も測定することが可能な半導体試験装置を実現する。

【解決手段】被試験対象デバイスに電源電圧を供給すると共に被試験対象デバイスに流れる電流に応じた変換信号を出力するDCモジュールを複数有し、各DCモジュールからの変換信号をマルチプレクサを切り替えて選択し、選択した変換信号をA/D変換器に与え、このA/D変換器を用いて電流を測定する半導体試験装置において、複数のDCモジュールからの変換信号がそれぞれ入力され、複数のDCモジュールのうちいずれか1つのDCモジュールからの変換信号を全ての出力端子に分配して出力する接続状態、または、複数のDCモジュールからのそれぞれの変換信号を各出力端子からそれぞれ出力する接続状態をとるスイッチ部を備える。

(もっと読む)

太陽電池セル測定用試料台

【課題】太陽電池セル内の各部の電位分布を測定することを可能にする太陽電池セル測定用試料台を提供する。

【解決手段】プローブバー17に配置された複数の電圧測定プローブ172のそれぞれに電圧出力端子を独立に電気的に接続する。これにより、各電圧出力端子のうちの任意の端子に電圧計のテストリード等を接続しておき、電圧測定プローブ172を測定対象の太陽電池セル50に押し当てた状態で太陽電池セル50に光を照射すれば、各電圧出力端子に対応する電圧測定プローブ172における太陽電池セル50との接触点の電位を測定することができ、太陽電池セル内の各部の電位分布を調べることができ、1枚の太陽電池セル内の各部の電気特性を評価することができる。

(もっと読む)

半導体装置及び半導体装置の評価方法

【課題】大規模な被測定トランジスタの特性を高精度に測定する半導体装置及びそれを用いた評価方法を提供する。

【解決手段】n行m列のマトリクス状に配列される被測定トランジスタDUTを有する評価セルC11〜Cnmと、被測定トランジスタにストレス電圧を印加するためのドレインストレス線DVS等と、評価セルを選択するための行選択信号供給用の行選択線X1〜Xnと、列選択信号供給用の列選択線Y1〜Ymと、入力される行選択信号と列選択信号に応じて被測定トランジスタの選択/非選択を表す選択信号を出力する選択回路10と、を備え、選択信号供給回路に入力される選択制御信号等により行選択信号と列選択信号を生成し、評価セル各々に設けられた第1のトランジスタT1〜第9のトランジスタT9を切り替え、被測定トランジスタDUTの測定評価、或いは被測定トランジスタDUTへのストレス電圧印加を行う。

(もっと読む)

半導体装置の試験装置及び試験方法

【課題】 本発明は、複数の半導体装置のうち任意の一つを背面側からコンタクタに対して押圧しながら試験を施すことができる半導体装置の試験装置及び試験方法を提供することを課題とする。

【解決手段】 複数の半導体装置20を支持基板21に整列して保持する。支持基板21を、コンタクタ24に向けて開口した空間を内側に有するステージ22に載置し固定する。押圧ヘッド25は、ステージ22の内側の空間内に配置される。支持基板21は複数の半導体装置20の各々の背面20bをステージ22の空間に向けて露出して保持する凹部を有する。ステージ22は水平方向に移動可能であり、押圧ヘッド25は垂直方向に移動可能である。押圧ヘッド25は、被試験半導体装置を押圧する押圧面25aと、被試験半導体装置を凹部内の所定位置に配置する位置決めガイド25bとを有する。

(もっと読む)

試験装置および診断方法

【課題】試験装置における各チャネルの自己診断を効率よく行う。

【解決手段】被試験デバイスを試験する試験装置であって、被試験デバイスに所定の出力信号を出力する出力回路、および、被試験デバイスの所定の特性を測定する測定回路をそれぞれが有する複数のモジュールと、それぞれのモジュールにおいて、出力回路の出力を測定回路で測定させ、それぞれの測定回路の測定結果に基づいて、それぞれのモジュールを診断する制御部とを備え、それぞれの測定回路は、対応する出力回路の出力を並行して測定し、制御部は、複数のモジュールに対して共通に設けられ、測定回路における測定結果を、モジュール毎に順次読み出す試験装置を提供する。

(もっと読む)

半導体集積回路

【課題】MOSトランジスタ特性のばらつきを精度良く定量的に評価できる半導体集積回路を得る。

【解決手段】MOSユニットUT1において、ゲート電極が共通接続されるPMOSトランジスタPT及びNMOSトランジスタNTを測定対象とし、全てのMOSユニットUT1の共通端子として、トランジスタPTのソース及びドレインにはソース端子SP及びドレイン端子DPが接続されると共に電圧モニタ端子SPM及びDPMがNMOSトランジスタQ1及びQ2を介して接続され、トランジスタNTのソース及びドレインにはソース端子SN及びドレイン端子DNが接続されると共にNMOSトランジスタQ3及びQ4を介して電圧モニタ端子SNM及びDNMに接続される。MOSユニットUT1が選択されると、測定対象のトランジスタPT,NTの一方及びトランジスタQ1〜Q4がオン状態とされる。

(もっと読む)

半導体装置のスクリーニング方法と装置並びにプログラム

【課題】半導体装置のスクリーニングを低コストで実現可能とする。

【解決手段】テスト装置(1)では、プローバ(2)により電気的接続がなされたウエハー(4)の被試験デバイスをテストする。テストの結果、良品判定された被試験デバイスについて、テスト時に観測した電圧値、電流値といった物理量を前記LSIの位置情報と共に、データファイル(3)に格納し、ウエハー(4)のすべての被試験デバイスのテストが完了した後、計算機(5)では記録媒体(7)に格納された判定プログラムに基づき、前記物理量の分布を検査し、その結果、事前に定められた判定基準によって、前記分布から外れている物理量をしめした被試験デバイスを特定し、その位置座標を結果(6)として出力する。

(もっと読む)

半導体集積回路の静止電源電流検査方法および装置

【課題】半導体集積回路の静止電源電流検査において、静止電源電流規格値を従来の製造工程のバラツキを考慮した値に比べて小さく設定することを可能にする。

【解決手段】半導体集積回路の識別情報を取得する工程と、半導体集積回路の静止電源電流値を測定する工程と、静止電源電流値と識別情報を対にして記憶する工程と、記憶された静止電源電流値を用いて静止電源電流規格値を決定する工程と、記憶された静止電源電流値を静止電源電流規格値と比較して半導体集積回路の良否判定を行う工程とを備える。また、検査の実施に先立って静止電源電流規格値の初期値を設定する工程と、測定された静止電源電流値をこの初期値と比較して良否判定を行う初期良否判定工程とを備え、初期良否判定工程で良品と判定された半導体集積回路の静止電源電流値のみを用いて静止電源電流規格値を決定する。

(もっと読む)

電子部品の自動分類機の作動制御方法

【課題】ビンボックスが所定数の電子部品で満たされる度に分類機の稼働と中断が繰り返えされること及びその度に分類機に対するビンボックスの手作業による出し入れから生ずる作業能率の低下を改善することにある。

【解決手段】テスタで性能測定が行われてその結果についてランク付され又は分類番号を取得した電子部品を分類してビンボックス(21)に収納する電子部品の分類機において、電子部品の性能測定結果ランク外のビンボックスを、集中する性能測定結果ランクの電子部品のための予備のビンボックスとして用意し、電子部品の集中するビンボックスが所定数の電子部品で満たされる順に、それらの電子部品に前記予備のビンボックスを割り当てるようにする。

(もっと読む)

集積型半導体レーザ装置のバーイン方法

【課題】複数の半導体レーザ素子のそれぞれの試験時の温度を均一に保持し且つ試験時間を短くすることができる集積型半導体レーザ装置のバーンイン方法を提供すること。

【解決手段】複数の半導体レーザのうち1つおきに配置される半導体レーザの第1グループを所定の温度下で同時に駆動するとともに複数の半導体レーザのうち残りの第2グループを非駆動とする第1の駆動ステップと、複数の半導体レーザのうち第2グループを所定の温度下で同時に駆動するとともに第1グループを非駆動とする第2の駆動ステップと、複数の半導体レーザの特性を測定する測定ステップと、特性の測定結果に基づいて合否を判定する合否判定ステップとを有する。

(もっと読む)

デバイス試験装置およびデバイス試験方法

【目的】本発明は、ソースプログラムに含まれる多項演算を翻訳する演算処理プログラムに関し、コンパイル時に多項演算をハードウェア命令に展開する際に、多項演算の桁数の少ない順にソートした後にハードウェア命令に展開したり、中間結果も含めて演算の演算結果が最小となる組み合わせから順にハードウェア命令に展開し、多項演算を実行するハードウェア命令数を最小限にして実行速度の向上を図ることを目的とする。

【構成】 ソースプログラムに含まれる多項演算中の演算を桁数の小さい順にソートするステップと、小さい順にソートした後の多項演算の先頭から順に演算するハードウェア命令を生成する際に、ハードウェア命令の桁数を超えたときは超えない範囲に分割するステップと、多項演算の先頭から順に演算するハードウェア命令を生成、あるいは分割されたときは分割後の演算についてそれぞれハードウェア命令を生成するステップとを有する。

(もっと読む)

MCMのテスト用治具およびMCMのテスト手法

【課題】 MCMに搭載されるチップがテスト回路を内蔵していなくても、チップ単体テストを行うことのできるテスト用治具およびテスト手法を提供する。

【解決手段】 コンタクトヘッド1Aは、テスト対象のCPUチップ20が接続されるMCM基板10上のパッド11BにMCM基板内配線13により接続されているテスト非対象チップ接続用のMCM基板10上のパッド11A1に1端を接触させる導電性の接触端子2と、MCM外部端子12に接続されているテスト非対象チップ接続用のMCM基板10上のパッド11A2に1端を接触させる導電性の接触端子3と、接触端子2の他端と前接触端子3の他端とを電気的に接続する配線4とを備える。

(もっと読む)

バーンイン装置

【課題】単一の恒温槽を用いて同時に異なる種類の試験を行う。

【解決手段】恒温槽装置1、制御装置2、複数のテストユニット3よりバーンイン装置を構成する。テストユニット3は、断熱ケース31、断熱ケース31の内部空間に収容されたドライバボード32、バーンインボード4を装着するための複数のコネクタを備えたスロットを備えたマザーボード33を備えている。外部コネクタ35を介して恒温槽装置1から電源が供給されと共に制御装置2との入出力が可能な形態で、各テストユニット3は、恒温槽装置1のチェンバー12に収容される。また、各テストユニット3のドライバボード32は、そのドライバボード固有の試験を、制御装置2のテスト開始の指示に応じて、マザーボード33を介して接続したバーンインボード4に対して行い、試験結果を制御装置2に出力する。

(もっと読む)

電気光学装置、その検査方法、駆動装置および電子機器

【課題】 駆動装置の実装後の検査を可能として検査の結果の有効性を向上させる。

【解決手段】 データ線駆動回路200は、各々がデータ線103に接続されるn個の出力端子Toutと、各画素について指定された階調に応じてデータ信号X1ないしXnを生成する信号生成回路25と、各データ線103における電流のリークを検出するための検出用配線30と、各々が出力端子Toutに接続されたn個のスイッチング素子271とを有する。各スイッチング素子271は、モード選択信号Smodによって駆動モードが指定されると、信号生成回路25が生成したデータ信号X1ないしXnを各出力端子Toutに出力する一方、モード選択信号Smodによって検出モードが指定されると、総ての出力端子Toutを検出用配線30に導通させる。

(もっと読む)

半導体チップの故障解析方法

【課題】良品チップを無駄にすることなく、複数の半導体チップのウエハ上の故障分布状況を解析することができる半導体チップの故障解析方法を得ること。

【解決手段】良品チップ2と不良品チップ3が識別されたウエハ1をダイシングカットし、ダイシングカットされたウエハから良品チップを抜き取る第1のステップと、残った不良品チップのウエハ上の位置を判別し、該不良品チップのウエハ上の位置を示す第1の位置情報(a,b)を記憶するとともに、前記不良品チップをピックアップして解析ステージ上10に移送する第2のステップと、解析ステージ上の各不良品チップを故障解析することにより各不良品チップ内での故障位置を示す第2の位置情報を作成し、作成した第2の位置情報および前記記憶された第1の位置情報に基づきウエハマップ4上に不良品チップおよび不良品チップ内での故障位置を識別表示する第3のステップと、を含む。

(もっと読む)

半導体装置検査ボード

【課題】異なる種類の半導体装置を柔軟に組み合わせて同時検査を実施できるようにし、汎用検査装置を用いた検査作業の効率向上、検査時間の短縮ならびに検査コストの低減を実現する。

【解決手段】検査ボードを、汎用検査ボード14と、実装用検査ボード12,13に分割し、実装用検査ボード12,13を、汎用検査ボード14上の任意の位置に装着することを可能(任意位置における着脱自在)とする。半導体装置の種類毎に実装用検査ボード12,13を予め作成しておけば、半導体検査装置11のもつ能力を越えないという条件の下で、適切な実装用検査ボード12,13を、汎用検査ボード14に適宜、装着するだけで、各種の半導体装置についての同時検査を実施できるようになる。

(もっと読む)

1 - 20 / 22

[ Back to top ]