Fターム[2G017AB08]の内容

Fターム[2G017AB08]に分類される特許

1 - 20 / 36

磁気センサ

【課題】磁気を検出するホールセンサと、前記ホールセンサの駆動や信号処理を行うためのICをリードフレームのダイパッド上に別々にダイボンドにより配置し、かつ1つのパッケージ内に封入されている磁気センサにおいて、急激な磁束密度の変化によりリードフレームに発生する渦電流の影響を抑え、電流センサに必要な高速応答性を備えた磁気センサを提供すること。

【解決手段】磁気を検出するホールセンサと、前記ホールセンサの駆動や信号処理を行うためのICをリードフレームのダイパッド上に別々にダイボンドにより配置し、かつ1つのパッケージ内に封入されている磁気センサにおいて、前記リードフレームのダイパッドが互いに電気的に絶縁された2つ以上の複数の金属片から構成されているようにする。

(もっと読む)

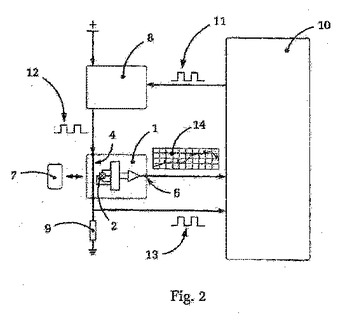

電流検出用センサ

【課題】電源を不要とし、環状コアの磁気回路についての非対称性を容易に補正可能で、かつ検出する電流について大きなダイナミックレンジを確保する。

【解決手段】分離位置Aを挟んでコア部2aに巻回された第1コイル3およびコア部2bに巻回された第2コイル4と、分離位置Bを挟んでコア部2aに巻回された第3コイル5およびコア部2bに巻回された第4コイル6とを備え、各コイル3,5は順極性で直列接続されて第1直列回路21を構成し、各コイル4,6は順極性で直列接続されて第2直列回路22を構成し、第1直列回路21にはコイル3,5に発生する誘起電圧のバランス調整用の第1抵抗回路7が接続され、第2直列回路22にはコイル4,6に発生する誘起電圧のバランス調整用の第2抵抗回路8が接続され、各直列回路21,22は順極性の状態で直列接続されて、各直列回路21,22の両端間にそれぞれ発生する誘起電圧の差動電圧を出力する。

(もっと読む)

磁気センサ

【課題】感磁部と磁気感度および抵抗の調整を可能とするトリミング部とを備えた磁気センサを提供すること。

【解決手段】磁気センサは、基板26に設けられた化合物半導体からなる十字形状パターンの感磁部21を備え、入力端子21a,21bと出力端子21c,21dの少なくとも一方の端子21a,21dに、化合物半導体を有するトリミング部23a,23bが接続電極24を介して直列接続されている。ウェハプロービングを行いながら、接続電極24を介して感磁部21に直列接続された入力端子側のトリミング部23aを、レーザートリミングすることにより、定電圧駆動における磁気感度の調整を可能とし、同様に出力端子側のトリミング部23bをトリミングすることにより出力抵抗の調整を可能にした。

(もっと読む)

磁界検知装置

【課題】 地磁気などの磁気を検知する3軸のセンサを用い、磁気ベクトルの正確な回転動作と角速度を計算できる磁界検知装置を提供する。

【解決手段】 磁気ベクトルを検知する3つの磁気センサからの検知出力に基づいて、磁気ベクトルの座標点を演算する。演算された座標点データを所定数含む第1の演算データ群N1−1を用いて、座標点データが移動している移動平面を求める。次に、複数の最新座標点データを含む最新データ群Na−1の平均値と移動平面との誤差を求め、その誤差が小さいときは、最新データ群Na−1を含むデータ数の多い第1の演算データ群N1−2を使用して移動平面を求める。前記誤差が小さいときは、最新データ群Na−1を含む少数のデータから成る第2の演算データ群N2−1を使用して移動平面を演算する。

(もっと読む)

電磁デバイス

【課題】基板に磁石が及ぼす磁界により発生する誘導起電力の影響を抑える。

【解決手段】基板3と、基板3に対向して配置され基板3に対向する面内にS極とN極が存在する磁石2を含み、基板3には、電気部品4と、電気部品4にそれぞれ接続されて、基板3上で引き出されている複数の電気配線5a,5bを有する。磁石2と基板3は互いに相対的に移動または回転可能である。複数の電気配線5a,5bは、電気部品4から見て引き出し方向に位置する部分であって、磁石2と基板3とが互いに相対的に移動または回転する際に、磁石2から受ける磁力によって誘電起電力が発生させられる部分5Xと、電気部品4から見て引き出し方向と反対側に位置する部分であって、誘導起電力と反対の極性の誘導起電力が発生させられる部分5Yとを含む。

(もっと読む)

半導体磁気センサ及びそれを用いた磁性体検出装置

【課題】ノイズの影響が低減され、かつ、増幅歪みの少ない半導体磁気センサ及びそれを用いた磁性体検出装置を提供すること。

【解決手段】直列接続された第1の半導体磁気抵抗素子11及び第2の半導体磁気抵抗素子12と、第1の半導体磁気抵抗素子11及び第2の半導体磁気抵抗素子12の接続ノードにゲート電極が接続された電界効果トランジスタ10とを備えている。電界効果トランジスタ10のゲート電極の幅を第1の半導体磁気抵抗素子11及び第2の半導体磁気抵抗素子12の各中心点を結んだ直線に投影した時の長さが、第1の半導体磁気抵抗素子11及び第2の半導体磁気抵抗素子12の各中心点の直線距離の略偶数倍であるように構成されている。

(もっと読む)

磁気センサ

【課題】簡易な構成にして、 MHz帯域の微弱磁界を検出することの可能な磁気センサを提供する。

【解決手段】微弱な高周波磁界を検出する検出コイル(2)と、検出コイルに誘導される誘導電流をインピーダンス変換して電圧信号として出力するトランスインピーダンスアンプ(3)とを具備し、検出コイルは、寄生容量が所定値より小さい巻数である。

(もっと読む)

磁気センサ装置

【課題】磁気センサ装置内部の各構成素子が発するノイズや外来ノイズによる磁界強度の検出または解除のばらつきを抑制し、高精度な磁気読み取りを可能にする。

【解決手段】比較器の出力端子がそれぞれ入力端子に接続される第一のD型フリップフロップおよび第二のD型フリップフロップと、第一のD型フリップフロップと第二のD型フリップフロップの出力端子がそれぞれ第一、第二の入力端子に接続されるXOR回路と、第二のD型フリップフロップの出力端子と第三のD型フリップフロップの出力端子がそれぞれ第一、第二の入力端子A、Bに接続され、XOR回路の出力がセレクト端子に接続され、XOR回路の出力に応じてAかBの入力を選択的に出力するセレクタ回路と、セレクタ回路の出力端子が入力端子に接続される第三のD型フリップフロップと、を備える。

(もっと読む)

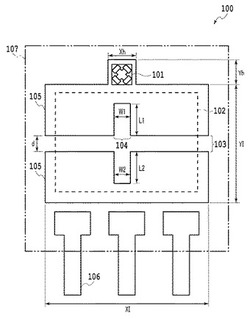

磁気センサの周波数応答を高める方法および装置

集積回路パッケージ・デバイスを設けるための方法および装置。集積回路パッケージ・デバイスは、導電性リードフレームと、このリードフレーム上に配置された磁気センサ・エレメントとを備えている。リードフレームは、磁気センサ周囲において渦電流の流れを低減するスロット構成を含む。このスロット構成は、第2スロットに対して概略的に垂直な第1スロットを含み、第1スロットはセンサ・エレメントの下を貫通する。 (もっと読む)

磁気センサ回路

【課題】磁気検出レベルが電源の内部抵抗の抵抗値に依存しにくい低消費電力の磁気センサ回路を提供する。

【解決手段】比較回路21は、主にホール素子25及び増幅回路26が給電されることによって電源電圧VDDが電圧降下した状況でのサンプル後に生成された磁気に基づいた電圧Vh2と、その状況でのサンプル後の基準電圧Vrefと、を比較する。これらの電圧は、両方とも、内部抵抗33によって電圧降下した電源電圧VDDに基づいて生成される。よって、磁気検出レベルBdetが内部抵抗33の抵抗値Rvddに依存しにくくなる。また、例えば、サンプル期間では比較回路21が動作しないようにでき、比較期間ではホール素子25及び増幅回路26が動作しないようにできるので、その分、磁気センサ回路の消費電力が低くなる。

(もっと読む)

磁気センサ

【課題】出力電圧の測定精度を高めることで、検出精度を向上させる磁気センサを提供する。

【解決手段】外部磁界の方向を検出するための磁気センサ1は、それぞれが少なくとも1つの磁気抵抗効果素子からなる4つの抵抗素子部11−14によって構成され、外部磁界の方向に応じて出力が変化するようになっているブリッジ回路10と、ブリッジ回路10の各出力端子A,Cにそれぞれ接続された2つの抵抗体21,22と、を有し、各抵抗素子部11−14の抵抗値が磁気抵抗変化により最小値となった時のブリッジ回路10の抵抗値に対する、各抵抗体21,22の抵抗値の比が2以上である。

(もっと読む)

磁気センサの部品配置構造

【課題】磁気検出部材とバイアス磁界発生源の磁石との間に実装バラツキが存在していても、バイアス磁界のバラツキを低く抑えることができる磁気センサの部品配置構造を提供する。

【解決手段】磁気センサは、複数の検出素子8a〜8dを持つ磁気検出素子チップ2と、この磁気検出素子チップ2にバイアス磁界を印加する磁石3とを備える。そして、磁石3の発磁面幅Waを検出素子8のパターン幅Wbよりも大きく設定し、磁石3の発磁面長さK1を、検出素子8のパターン間隔K2よりも小さく設定する。

(もっと読む)

磁気検出装置及び磁気検出装置のテスト方法

【課題】 特に、出力のオフセットが許容所定内であるか否かを簡単に検出することが出来る磁気検出装置及び磁気検出装置のテスト方法を提供することを目的とする。

【解決手段】 複数の磁気検出素子を接続して成るブリッジ回路には、一方の直列回路の入力端子Vdd側に設けられた出力部a1とグランド端子GND側に設けられた出力部a2の間、及び他方の直列回路の入力端子Vdd側に設けられた出力部a3とグランド端子GND側に設けられた出力部a4との間に、第1,第2の抵抗部25,26が接続されている。各第1,第2の抵抗部25,26にテスト用抵抗部33,34を並列接続する。続いて、出力テストを行い、Low信号が出力されれば良品、High信号が出力されれば不良品とする。出力テスト終了後、前記テスト用抵抗部33,34を回路的に切り離して製品化する。

(もっと読む)

磁気センサ

【課題】

耐ノイズ特性及び製造上のばらつきの低減化が図れる磁気センサを提供する。

【解決手段】

磁気センサ(100)は、磁電変換素子(110)、定電流回路(120)、クランプ(130)及び増幅部(140)を有する。磁電変換素子(110)は一対の入力端子(110a,110b)及び一対の出力端子(110c,110d)を有する。定電流回路(120)は一対のPMOSトランジスタ(PMOS1,PMOS2)で構成し、入力端子(110a)にPMOSトランジスタPMOS1のドレイン側から定電流(id1)を供給する。クランプ回路(130)は、入力端子(110b)から流出する定電流(id1a)を吸い込む。クランプ回路(130)の入力部及び増幅部(140)の入力段はそれぞれPMOSトランジスタの差動増幅器で構成する。

(もっと読む)

診断可能なホールセンサ

本発明はホールプローブ(2)を用いて磁界強度を検出するための測定装置並びにホールセンサ装置(1)の機能診断のための方法に関している。前記測定装置は、少なくとも1つのホールプローブ(2)を備えたセンサ装置(1)を含んでいる。本発明は、前記ホールプローブ(2)からガルバニック絶縁された電気的な診断用導体(4)によって特徴付けられる。本発明によればセンサ装置(1)ないしホールセンサ(2)の永続的でかつ包括的な診断を行うことのできる、ホールセンサ装置(1)とその機能診断のための方法が得られる。特にホールセンサ(2)は定量的な機能性や欠陥のみでなく、適正な較正に関しても定量的な検査が可能である。場合によってはセンサ(2)の即応的な補正も行うことができる。これにより特に温度ドリフトやセンサ(2)の機械的な緊張に基づく測定エラーが除去できるようになる。  (もっと読む)

(もっと読む)

ブリッジにおけるGMRセンサの整合

磁気抵抗(MR)検出デバイスは、ブリッジ回路を形成するように電気的に接続されたMR素子と、ブリッジ回路MR素子の改善された整合のための1つまたは複数の非機能的(または「ダミー」)MR素子とを含む。  (もっと読む)

(もっと読む)

検出回路

【課題】簡易な構成で検出精度を向上させる。

【解決手段】検出回路は、センサの駆動を制御するためのデジタル制御信号を所定周波数のクロックに基づいて更新して出力する制御信号更新回路と、制御信号更新回路から出力されるデジタル制御信号を、前記センサを駆動すべくアナログ制御信号に変換して出力するDAコンバータと、アナログ制御信号に応じて変化するセンサの検出信号の電圧レベルと、所定レベルの基準電圧との比較結果信号を出力する比較回路と、比較回路から出力される比較結果信号と、所定周波数のクロックとに基づいて、検出信号に応じた時間をカウントして出力するカウント回路と、を備える。

(もっと読む)

磁気センサ

【課題】ハーフブリッジに備えられる一対の磁気抵抗素子間の抵抗値のばらつきを抑制した磁気センサを提供する。

【解決手段】磁気センサ10において、共通の基板14上に配置された一対の第1磁気抵抗素子16、第2磁気抵抗素子18が、その第1磁気抵抗素子16の薄膜ヨーク30、32の感磁方向すなわち中心線C1の方向と第2磁気抵抗素子18の薄膜ヨーク30、32の感磁方向すなわち中心線C2の方向とが相互に平行な方向となるように配置されていることから、一対の磁気抵抗素子16、18は基板14上において一面に同時に成膜されたGMR膜のうち同じ方向のGMR膜が一対の磁気抵抗素子16、18のGMR膜34としてそれぞれ用いられるので、一対の第1磁気抵抗素子16の抵抗値R1および第2磁気抵抗素子18の抵抗値R2の間のばらつきがそれぞれ好適に抑制される。

(もっと読む)

磁界検出装置および磁界検出装置の製造方法

【課題】 磁気抵抗効果素子を構成要素とする複数の抵抗部を有するホイーストンブリッジ回路を備えた磁界検出装置において、検知磁界に対する出力の線形性や温度特性を損なうことなく、ホイーストンブリッジ回路を構成する抵抗部の抵抗値を調節することは困難であった。

【解決手段】 磁界検出装置を複数の抵抗部を有するホイーストンブリッジ回路を備えたものとし、抵抗部のうち少なくとも一つの抵抗部を、複数の磁気抵抗効果素子が並列に接続された素子群で構成する。

(もっと読む)

半導体磁気センサ

【課題】 外部から印加された磁界の磁束密度を正確に検出する。

【解決手段】 ホール素子100の一辺の側に形成され、その一辺に設けられた端子C101にドレインが接続され、ホール素子100を駆動するトランジスタMP101と、その一辺の側に形成され、その一辺に設けられた端子C102にドレインが接続されたトランジスタMP102と、その一辺に対向する他辺の側に形成され、その他辺に設けられた端子C103にドレインが接続されたトランジスタMN101と、その他辺の側に形成され、その他辺に設けられた端子C104にドレインが接続されたトランジスタMN102と、を備える。

(もっと読む)

1 - 20 / 36

[ Back to top ]