Fターム[2G132AC01]の内容

Fターム[2G132AC01]に分類される特許

1 - 20 / 36

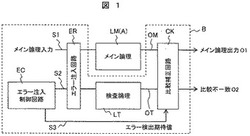

自己診断機能付き装置

【課題】自己診断する論理の範囲を比較回路以外の検査論理、更にはメイン論理に広げ、検査論理、メイン論理に異常がある場合、比較回路が不一致を発生する前に検出し装置の交換ができるようにする。

【解決手段】同じ入力が与えられ、同じ論理演算を実施する第1と第2の論理部、第1と第2の論理部のいずれかにエラー信号を与えるエラー注入回路、第1と第2の論理部の出力を入力し選択した信号を与える選択回路と第1と第2の論理部の出力を比較し、比較不一致信号を与える比較回路とを備えた比較補正回路から構成され、比較補正回路は、第1と第2の論理部のいずれかにエラー信号を与えた時、第1と第2の論理部の出力が不一致にならない場合、または、第1と第2の論理部にエラー信号を与えないときに、第1と第2の論理部の出力が不一致になる場合に異常があると判断する。

(もっと読む)

評価システム

【課題】製品ボードに搭載される製品FPGAの端子数に制限されず、内部信号の観測を可能とし、製品FPGAを製品ボードに搭載された実使用状態で論理検証することが可能な評価システムを提供することを課題とする。

【解決手段】評価システム1は、製品ボード2、評価ボード3、およびそれらを接続するシリアル・インターフェース5を備える。製品ボード2に搭載される製品FPGA6はコアロジック60に入力される外部入力信号を分岐する分岐回路61を備える。評価ボード3は観測FPGA8を備える。観測FPGA8はコアロジック60と論理的に等価な観測コアロジック81および観測コアロジック81の内部信号を取得する内部信号取得回路82を備える。コアロジック60の実動作に供される外部入力信号が評価ボード3に送られ観測コアロジック81がコアロジック60の実動作と等価に動作する。その時の内部信号を取り出し論理検証を行う。

(もっと読む)

半導体集積回路のテスト回路、故障診断回路、テスト装置、テストボード、及びテストプログラム

【課題】期待値を予め準備することなく、またテストパターンの数が制限されることなく半導体集積回路のテストを行う。

【解決手段】PRPG20で、タップ及びシード(設定値)をセットして、ランダムな入力パターンを大量に発生し、基準の半導体集積回路32A、32B、32C、及びテスト対象の半導体集積回路34へ発生した入力パターンを入力する。期待値生成回路22で、基準の半導体集積回路32A、32B、32Cの出力パターンに基づいて期待値パターンを生成し、判定回路24で、期待値生成回路22で生成された期待値パターンとテスト対象の半導体集積回路34の出力パターンとを比較することにより、テスト対象の半導体集積回路34のパス/フェイル判定を行う。フェイル判定の場合には、入力パターン発生時の設定値をメモリ26に記憶する。

(もっと読む)

半導体装置解析システム

【課題】初期の故障解析において、機能不具合を内在する半導体装置に対して確実な不具合の再現を可能とし、半導体装置に内蔵された回路のどの部分に問題があるかを解析する手段を提供する。

【解決手段】良品の半導体装置2と、故障品半導体装置3と、良品の半導体装置2と故障品半導体装置3と実機の基板(ボード)4とが配線16で接続され、クロック制御6と比較回路7とを備えた信号共有分割部を備えた解析装置本体の動作により、実機の基板(ボード)4を良品の半導体装置2で動作させつつ、同じタイミングで、故障品半導体装置3を動作させ、その挙動の差異を検知して故障解析を行う。

(もっと読む)

発光解析装置および発光解析方法

【課題】半導体装置の発光解析により半導体装置の故障箇所を精度よく検出可能な発光解析装置および発光解析方法を提供する。

【解決手段】発光解析システムは、制御部1と、画像取得部2と、画像記憶部3と、座標合わせ部4と、比較部5と、駆動装置6と、発光検出器7と、画像表示部8と、を備えている。終了テストパターンアドレスを変化させながら複数の合成発光積分画像を取得し、終了テストパターンアドレスが小さい順、すなわち開始テストパターンアドレスに近い終了テストパターンアドレスから順に良品および不良品半導体装置の合成発光積分画像の比較を行う。そのため、不良品半導体装置における異常な発光が生じる頻度が小さい場合や、良品半導体装置との発光の差異がタイミングの差異のみである場合でも、合成発光積分画像の差異を検出でき、故障箇所を特定できる。

(もっと読む)

半導体集積装置の故障検出方法

【目的】半導体集積装置に構築されている回路網中に生じている遅延故障箇所を精度良く検出することが可能な半導体集積装置の故障検出方法を提供することを目的とする。

【構成】故障検出の対象となる半導体ICチップ(テストチップ)、及びこの半導体ICチップの良品としての半導体ICチップ(良品チップ)各々に構築されている回路を動作させ、テストチップ及び良品チップ各々に構築されている回路網中の各信号経路から出力された出力結果が互いに一致しているか、或いは不一致であるかを判定する。ここで、不一致であると判定された場合には、この不一致であると判定された信号経路に故障が生じていると判断する。一方、一致していると判定された場合には、テスト周期を短い周期に変更して、再び上記動作を繰り返し実行する。

(もっと読む)

LSI評価ボード装置

【課題】 本発明の課題は、プログラムされたユーザー論理を用いたLSIのプロトタイピングにおいて、評価精度を向上させることを目的とする。

【解決手段】 上記課題は、2つのデバイスで構成されるプロトタイピング環境を実装するLSI評価ボード装置は、有効なバストランザクションの検出に応じて、前記2つのデバイスの動作に係る回路構成のクロック停止を指示する第一指示回路と、前記クロック停止の指示に応じて、前記デバイス間を接続する外部バスに係る回路構成を除く前記2つのデバイスの動作に係る回路構成のクロックの停止を制御するクロック制御回路とを有するLSI評価ボード装置により達成される。

(もっと読む)

劣化診断装置及び劣化診断方法

【課題】処理装置の検査を適切なタイミングで行うことが可能な劣化診断装置を提供する。

【解決手段】劣化診断装置100は、検査対象となる処理装置30を検査する検査手段(例えば、検査装置20及び制御装置10により構成される)と、処理装置30の劣化と相関的に劣化する被検体の劣化である相関劣化を検出する劣化検出手段(劣化検出装置40)とを備える。検査手段(検査装置20及び制御装置10)は、劣化検出手段(劣化検出装置40)により相関劣化が検出された場合に処理装置30を検査する。

(もっと読む)

試験装置および校正方法

【課題】試験装置を簡易に校正する。

【解決手段】被試験デバイスを試験する試験装置であって、被試験デバイスを試験するための試験信号をそれぞれ出力する複数の試験信号出力部と、試験信号に応じて被試験デバイスが出力する応答信号をそれぞれ取得する複数の応答信号取得部と、当該試験装置を校正する場合に、基準となる試験信号出力部が出力した試験信号の電圧レベルに応じた論理信号を複数の応答信号取得部のそれぞれへと出力する基準ドライバ部を備える校正用デバイスを、被試験デバイスの代わりに搭載するデバイス搭載部と、校正用デバイスが搭載された状態で、基準ドライバ部が出力した論理信号を調整対象の応答信号取得部が取得した結果に基づき、調整対象の応答信号取得部が論理信号を取得するタイミングを調整する調整部と、を備える試験装置を提供する。

(もっと読む)

試験装置の制御方法

【課題】 複数の測定ステーションのいずれを用いても正常に点検を実施することができる、試験装置の制御方法を提供する。

【解決手段】 試験装置の制御方法は、複数の被試験デバイスステーションと、同じ項目を測定可能な複数の測定部と、複数の被試験デバイスステーションと複数の測定部との接続組合せを変更可能なマトリクススイッチと、を備える試験装置において、複数の測定部を用いて標準デバイスを測定することによって測定部の点検を行う測定部点検ステップを複数の測定部に対して行う第1ステップと、被試験デバイスステーションに標準サンプルを搭載し標準サンプルが搭載された被試験デバイスステーションと接続された測定部を用いて標準サンプルの点検を行う被試験デバイスステーション点検ステップを複数の被試験デバイスステーションに対して行う第2ステップと、を含む。

(もっと読む)

基板接続検査装置

【課題】接触不良であることを検知することができ、そして、そのような場合でも被測定基板の良否の判定が可能な基板接続検査装置を提供する。

【解決手段】基板接続検査装置1は、プローブ8を配設したプローブ部7、インターフェース基板5、電気的特性を測定するTDR測定器10、パーソナルコンピュータ15を備えている。複数のプローブ8は、プリント基板2に設けられた複数のランドに同時に接触する。TDR測定器にて発生したパルスをプローブからランドに入力させるとともに、反射された反射波を測定する。反射波の反射波形と基準波形とを比較することにより、プローブが接触不良であるか否か等が判定される。

(もっと読む)

回路基板検査装置および回路基板検査方法

【課題】多くの導体パターンや電子部品を有する回路基板を検査する際の検査効率の向上および検査コストの低減を実現する。

【解決手段】定格電圧が所定値以下の電子部品を介して接続された導体パターンで構成される導体パターン群内の各導体パターンの良否を検査する第2検査を実行する検査部5を備え、検査部5は、良品の回路基板100における導体パターン群内の各導体パターン間の抵抗値の測定値が閾値以上であるか否かの判別結果を示す検査用データDi1を生成すると共に、第2検査の実行時に、検査対象の回路基板100における導体パターン群内の各導体パターン間の測定値が閾値以上であると判別しかつその判別結果と検査用データDi1による判別結果とが一致するときに絶縁状態が良好と判定し、測定値が閾値以上ではないと判別しかつその判別結果と第1検査用データによる判別結果とが一致しないときに不良と判定する。

(もっと読む)

ソケット分離型半導体試験装置、ソケット分離型半導体試験方法、循環型半導体試験装置、および循環型半導体試験方法

【課題】半導体試験装置の短期間の経時における変化が発生する場合に対応し、デバイスを正確に測定し、出荷品質を向上させる。

【解決手段】基準デバイスeと複数個の第1測定デバイスfとを順番に測定して前記基準デバイスeの第1テストログを生成した後、前記基準デバイスeと複数個の第2測定デバイスとfを順番に測定して前記基準デバイスeの第2テストログを生成する試験装置cと、前記基準デバイスeの第1テストログと第2テストログとを比較する解析部a4と、前記基準デバイスe、前記複数個の第1測定デバイスf、および前記複数個の第2測定デバイスfのそれぞれに測定環境を提供する測定環境装置bと、前記解析部a4による比較結果の差異に応じて、前記測定環境装置bによって提供される測定環境を調整する測定環境制御部a2とを備えた。

(もっと読む)

半導体試験回路及び検証方法

【課題】少ない工数での検証が可能な半導体試験回路を提供する。

【解決手段】半導体試験回路1に、半導体装置20及び試験装置10に共通のテストパターンを入力する端子P1を設け、互いに共通のアドレスが割り当てられた回路ブロック配置領域を有する半導体装置20及び試験装置10において、同一のアドレスで指定される一方の前記回路ブロック配置領域にのみ回路ブロックを配置する。これにより、あたかも1つのデバイスであるかのように検証を行え、少ない工数での検証が可能になる。

(もっと読む)

単方向プローブに基づいて電子デバイスを多次元的に試験するための方法及び装置

本発明は、電子デバイスを試験する方法及び装置に関し、単方向測定プローブ(46)によって放射磁場を測定する。この方法及び装置は、ZZ’軸に沿った磁場のBz成分の第1の値(Bz1)をプローブ(46)によって測定し、記録した後で、プローブ(46)及び電子デバイスを、同一の距離d0を保持したまま、ZZ’軸に直交するXX’軸を中心に振幅90°未満の角度だけ旋回させることによって互いに対して移動させ、ZZ’軸の各位置(x,y)について、ZZ’軸に沿った磁場のBz成分の第2の値(Bz2)をプローブ(46)によって測定し、記録した後で、第1の値(Bz1)及び第2の値(Bz2)に基づいて、ZZ’軸及びXX’軸に直交するYY’軸に沿った磁場の成分By値を決定し、記録する。  (もっと読む)

(もっと読む)

検証システム、装置及び方法

【課題】サイクル精度レベルシミュレーションの結果とRTLシミュレーションの結果との一致を高速に検証するための検証システム、装置及び方法を提供する。

【解決手段】サイクル精度レベルシミュレーション制御部220はサイクル精度レベルシミュレーションモデル、サイクル精度レベルテストパタン及びRTL記述を取得し、サイクル精度レベルシミュレーション実行部210にサイクル精度レベルシミュレーションを実行させる。そして、検証ピリオド毎にその結果と内部状態とを読み出し、記憶装置300に分けて記憶させる。次に、記憶された内部状態を初期値とし、検証ピリオド毎に生成されたテストパタンを用いて、RTLシミュレーション実行部250がRTLシミュレーションを検証ピリオド毎に並列に実行する。期待値照合部270は、サイクル精度レベルのシミュレーション結果を期待値として、RTLシミュレーションの結果と照合する。

(もっと読む)

電子部品の検査装置

【課題】電子部品に衝撃を加えても電子部品の電気端子と検査装置の電気端子との接触を確実に維持する。

【解決手段】製品固定台17に電子チューナ11を取り付け、電子チューナ11のチューナ端子13と製品固定台17のコンタクトピン86とを接続した状態で、電子チューナ11に打撃を加えることで当該電子チューナ11の耐ショックノイズ特性を検査する検査装置であって、製品固定台17と固定部82が、基台100に立設された一対の支持板111,111の間に配置されており、これら支持板111,111間において、製品固定台17と固定部82とが揺動軸115によって一体的に揺動可能に支持されている。そして、一方の揺動軸115に緩衝シリンダ116が設けられており、電子チューナ11に衝撃が加わると、この緩衝シリンダ116の揺動軸115を中心に製品固定台17が揺動する。

(もっと読む)

プリント基板の不良解析システム

【課題】簡易な試験装置を用いた場合においても、アナログ入出力機能およびデジタル入出力機能を有するプリント基板の不良解析精度を向上できるようにする。

【解決手段】不良プリント基板2のAI端子6をAI/Oケーブル14を介して良品プリント基板3のAO端子9に接続し、不良プリント基板2のAO端子7をAI/Oケーブル15を介して良品プリント基板3のAI端子8に接続し、不良プリント基板2のDI端子10をDI/Oケーブル17を介して良品プリント基板3のDO端子13に接続し、不良プリント基板2のDO端子11をDI/Oケーブル16を介して良品プリント基板3のDI端子12に接続し、故障解析制御部1は、不良プリント基板2および良品プリント基板3に伝送データを送出し、その伝送データに対する不良プリント基板2および良品プリント基板3からの応答に基づいて、不良プリント基板2の故障解析を行う。

(もっと読む)

ノイズ発生回路、半導体集積回路、及び、ノイズ耐性評価方法

【課題】製品版の半導体集積回路がデジタル回路を含むときに、製品版の半導体集積回路で発生するノイズに近いノイズを発生させることができる半導体集積回路を提供する。

【解決手段】LSIは、複数の小エリアに分割され、各小エリアに、ノイズ源(ノイズ発生回路)12を有する。各ノイズ発生回路12は、小エリア内に、クロック信号CLKに従って、ノイズパターンデータNDATAをラッチする複数のFF(フリップフロップ)11を有する。各ノイズ源12は、ノイズイネーブル信号ENによって、独立に動作/非動作が制御可能である。

(もっと読む)

検査故障解析方法及び検査故障解析装置

【課題】正常チップの電源電流が大きい場合にもチップの異常識別を可能にすること。

【解決手段】LSIチップ1を搭載する試料台4と、試料台4を通じてLSIチップ1にテストパタンを供給するテストパタン発生器3と、変調のかかったレーザビーム8を走査しながらLSIチップ1を照射するレーザ変調機能付光学系5と、LSIチップ1からの信号における所定周波数の信号のみを取り出すロックインアンプを通じてLSIチップ1からの信号を取り出し、取り出した信号を走査点に対応させる画像処理を行うIR−OBIRCH制御部6と、IR−OBIRCH制御部6からの画像信号に基づいて画像を表示する表示部7と、を備える。IR−OBIRCH制御部6は、画像信号に基づいて、LSIチップ1における異常電流経路の有無を確認する。

(もっと読む)

1 - 20 / 36

[ Back to top ]