Fターム[2G132AD04]の内容

Fターム[2G132AD04]に分類される特許

1 - 20 / 83

半導体集積回路

電子回路検査装置、電子回路検査方法、回路基板検査装置および回路基板検査方法

半導体特性測定装置

発振回路およびテスト回路

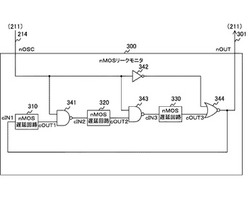

【課題】非導通状態におけるトランジスタから漏出するリーク電流を正確に測定することができるテスト回路を実現する。

【解決手段】遅延回路は、制御トランジスタ、測定対象トランジスタおよびコンデンサを備える。制御トランジスタは、入力端子の電位に応じて導通状態および非導通状態のうちのいずれかに移行することにより出力端子の電位を変化させる。チャネルの極性が前記制御トランジスタと同一の測定対象トランジスタは、電源とアースとの間において制御トランジスタに直列に接続される。コンデンサは、制御トランジスタが導通状態から非導通状態へ移行した場合に測定対象トランジスタから漏出したリーク電流の値に応じて出力端子の電位の変化を遅延させる。反転回路は、出力端子の電位を反転して前記入力端子に帰還させる。

(もっと読む)

半導体装置

【課題】部分的な経年劣化の予兆を早期に発見することができる半導体装置を提供する。

【解決手段】LSI1は、複数のモジュールと、複数の遅延モニタを含む遅延モニタ群15とを備える。各遅延モニタは、複数段のゲート素子を有するリングオシレータを含む。各遅延モニタは、ゲート素子の遅延時間を測定する。CPU#0は、遅延モニタによって測定された遅延時間に基づいて、遅延モニタの近傍のモジュールの経年劣化を判定する。

(もっと読む)

クロック周波数検出装置

【課題】電子装置において、動作クロックの周波数の異常を、動作クロックを選択的に通過させるフィルタ回路を用いることなく、高精度に検出できるようにする。

【解決手段】PLL回路10にて生成された動作クロックを受けて動作する制御装置2において、動作クロックの周波数の異常判定を行う際には、動作モード切換部32が、半導体メモリ12への書込用電圧を生成するF/V変換回路20のF/V変換特性を、動作クロックの周波数変動に対し出力電圧が略一定となる第1特性から、動作クロックの周波数に対応して出力電圧が変化する第2特性に切り換え、電圧検出部34が、その出力電圧を検出し、周波数異常判定部36が、その検出された電圧値に基づき動作クロックの周波数異常を判定する。

(もっと読む)

半導体集積回路のテスト方法とシステムとプログラム

【課題】ロット全体のテスト時間の短縮を図り、良品を不良と誤判定することを回避する方法、システム、プログラムの提供。

【解決手段】同一構成のLSI(被試験デバイス)のロットをテストするにあたり、一のLSIのファンクションテストを実行テストレート1で行い、前記ファンクションテストの結果がパスの場合、次のLSIのファンクションテストを実行テストレート1で行い、フェイルの場合、実行テストレート2で再び前記一のLSIの再テストを行い、再テストがパスした場合、実行テストレート1を現在値に加算テストレートを加算した値に更新して次のLSIのファンクションテストを前記更新した実行テストレート1で行い、前記一のLSIの実行テストレート1、2によるファンクションテストがいずれもフェイルの場合、前記一のLSIを不良と判定する。

(もっと読む)

位相特性推定装置並びにそれを備えた位相補正装置及び信号発生装置並びに位相特性推定方法

【課題】試験対象の周波数範囲全体にわたって位相特性を推定して位相特性の平坦化に資することができる位相特性推定装置並びにそれを備えた位相補正装置及び信号発生装置並びに位相特性推定方法を提供する。

【解決手段】信号発生装置1は、互いに異なる周波数の2つのCWを合成した合成CWを出力する信号出力部10と、合成CWを直交変調して直交変調信号を出力する直交変調器16と、直交変調信号の電力レベルを調整するレベル調整器20と、位相特性を推定する位相特性推定器30とを備え、位相特性推定器30は、合成CWの振幅値に基づいて隣接間位相差を算出する位相差算出部31と、隣接間位相差のデータに基づいて所定の周波数帯域における位相特性を推定する位相特性推定部33とを備える。

(もっと読む)

半導体集積回路及び誤動作防止方法

【課題】実システム動作中に電源状態を監視できる手段を提供する。

【解決手段】半導体集積回路は、発振器14と、電源電圧に応じて発振周波数が変化するリング発振器11と、発振器14の信号に基づいて、所定の判定期間を計測するインターバルタイマ13と、判定期間にリング発振器11が発振する発振周波数を測定する周波数測定用カウンタ12と、発振周波数の上限値と下限値とを保持する不揮発性メモリ15と、カウンタが測定した発振周波数が、不揮発性メモリ15が保持する上限電圧/下限電圧の判定コードの範囲内であるかを判定し、判定結果を出力する電圧判定回路16と、を備える。

(もっと読む)

コンデンサの実装状態判別装置およびコンデンサの実装状態判別方法

【課題】コンデンサの実装・非実装の判別と共に、非実装のときには非実装のコンデンサが実装されるべき位置を判別する。

【解決手段】導体パターン11,12上の測定点P1,P2間のインピーダンスの周波数特性を測定する測定部2と、コンデンサ21〜23が正常に実装された状態での周波数特性に現れる各共振周波数f1〜f3毎に、共振周波数f1〜f3を含む判定範囲fr1〜fr3と共振周波数f1〜f3に対応するコンデンサ21,22,23とを対応付ける基準データD2が記憶された記憶部3と、コンデンサ21〜23の実装状態が未知の導体パターン11,12についての周波数特性を測定部2に測定させ、この周波数特性に現れている共振周波数と基準データD2の各判定範囲fr1〜fr3とを比較して、共振周波数を含まない判定範囲fr1〜fr3に対応付けられたコンデンサが非実装状態であると判別する処理部4とを備えている。

(もっと読む)

定電流方式の発振回路におけるテスト方法

【課題】定電流方式の発振回路におけるインバータの消費電流を測定するテスト方法において、水晶振動子を接続することなく、外部信号を入力してテストしても、安定した正確なテストができるとともに、テスト時間も発振開始時間の影響がなく短縮できるテスト方法を提供する。

【課題の解決手段】水晶振動子を接続するためのXT端子とXTN端子を備え、定電流源6から定電流をインバータ1に入力する定電流方式の発振回路において、インバータ1による消費電流を電流測定器7で測定するテスト方法であって、XT端子とXTN端子の少なくとも一方、例えばXTN端子にプルアップ抵抗9を接続して、信号生成器11からの外部信号をXT端子から入力する。

(もっと読む)

モニタリング装置及びモニタリングシステム

【課題】LSI等の不具合発生時の原因追求を容易化する。

【解決手段】LSI内又はLSIの近傍にモニタリング装置100を配置し、モニタリング装置100内で、周波数カウンタ20が、一定時間でのリングオシレータ10の発振周波数を計測し、計測した発振周波数を示す発振周波数情報を生成し、時刻カウンタ30が、周波数カウンタ20により発振周波数が計測された時刻を示す時刻情報を生成し、出力制御部80が、発振周波数情報と時刻情報とを対応付けて記憶装置90に出力し、記憶装置90が、発振周波数情報と時刻情報をログとして記憶する。これにより、LSIが起動してから不具合発生までの間の発振周波数の推移を観測することで遅延の相対的な変化を確認することができ、LSIの個体差を気にする必要がなく、不具合発生時の原因追求を容易化できる。

(もっと読む)

半導体集積回路

【課題】分周信号を検査するにあたって、その周波数のみならず第1区間長および第2区間長をも検査し、比較対象に用いる信号を生成する高価な検査装置を必要としない自己診断回路を有する半導体集積回路およびその検査方法を提供する。

【解決手段】分周回路の検査を、生成される分周信号の周波数およびデューティー比、すなわち第1区間および第2区間の比率、の2つに対して行う。外部からはデューティー比を定義する2つの期待値を供給する。

(もっと読む)

検査装置

【課題】クロック信号発生手段の不具合の有無を一目で認識することができる検査装置を提供する。

【解決手段】検査基板400のFPGA92は、入力されたクロック信号の周波数、周期、Duty比の各期待値、実施回数をレジスタ部923へ記憶する(S14)。FPGA92は、入力されたクロック信号CLK1,CLK2の周波数、周期、Duty比を算出する(S32)。FPGA92は、算出したクロック信号CLK1,CLK2の周波数、周期、Duty比のそれぞれがレジスタ部923のクロック信号CLK1,CLK2の周波数、周期、Duty比の各期待値を満たすか否か判定して(S33)、判定結果をレジスタ部923の所定の領域へ記憶する(S34)。FPGA92は、満たさなければ(S35:No)、表示部93のLEDを赤色発光させ(S36)、満たせば(S35:Yes)、LEDを青色発光させる(S38)。

(もっと読む)

半導体装置およびその検査方法

【課題】本発明の実施形態は、高周波スイッチ回路の高周波特性の良否を簡便に判定することができる半導体装置およびその検査方法を提供する。

【解決手段】実施形態に係る半導体装置は、複数の高周波端子と、共通高周波端子と、の間の信号経路を、前記高周波端子と前記共通高周波端子との間に直列に設けられた複数のFETにより切り替える高周波スイッチ回路を有する半導体装置であって、前記共通高周波端子に接続された複数のFETを含む半導体スイッチと、前記半導体スイッチを介して前記共通高周波端子に接続された発振回路と、前記発振回路の出力を入力とする検波回路と、前記検波回路の出力端子と、を備える。

(もっと読む)

測定結果管理システム、管理サーバ、及び半導体集積回路装置

【課題】実際に稼動している半導体集積回路装置の実動作に影響を与える要因を解析し、更にその要因を低減することが可能な半導体集積回路装置を提供する。

【解決手段】測定対象である半導体集積回路131と、この半導体集積回路のジッタ又はノイズジッタ、ノイズ等の実動作に影響を与える物理量を測定する測定回路(半導体集積回路装置)130とを同一チップ上に構成する。測定回路の測定結果を解析し、測定対象の半導体集積回路を調整する回路にフィードバックさせる。

(もっと読む)

集積回路およびウェーハを試験する無線周波数技術構造および方法

【課題】集積回路を有するウェーハの無線試験を行うためのウェーハ上に形成された試験回路を含む装置および方法を提供する。

【解決手段】ウェーハ16の外部にある試験ユニット12、および集積回路を含むウェーハ上に製造された少なくとも1つの試験回路14を含む。試験ユニット12は、RF信号を送信し、試験回路14に電力を供給する。試験回路14は、可変リング発振器を含み、集積回路の公称動作周波数での一連のパラメータ試験を実行し、試験結果を分析のために試験ユニット12に送信する。

(もっと読む)

時間デジタル変換回路、及びその校正方法

【課題】高分解能のTDC回路の消費電力を低減することを目的とする。

【解決手段】本発明に係るTDCは、入力信号を遅延する遅延素子11を複数直列に接続するディレイラインと、ディレイラインの最後段の遅延素子の出力の反転信号を出力する反転素子13と、基準クロック、又は反転素子の出力信号のいずれかをディレイラインの初段の遅延素子に提供するマルチプレクサ15と、を有するリング発振器10と、ディレイラインの遅延素子の接続ノード、又は初段の遅延素子の入力ノードに接続され、被測定信号の変化エッジが、遅延素子11の出力する基準クロックを遅延した信号の変化エッジに対して進んでいるか遅れているかを判定する複数の判定回路17と、判定回路17の判定結果をエンコードするエンコーダ回路31と、エンコーダ回路31の出力から、被測定信号の変化エッジの基準クロックに対する位相を算出する演算回路33と、を備える。

(もっと読む)

検査装置および検査方法

【課題】サンプル装置が指定した平均サンプル数で正しく平均化しているかどうかを検査する。

【解決手段】トリガ信号毎に被測定信号の値を指定された平均化期間の間平均化して出力するサンプル装置を検査する検査装置であって、単調増加または減少する第1信号をサンプル装置に供給し、第1信号と異なる種類の曲線で単調増加または減少する第2信号をサンプル装置に供給する信号供給部と、第1信号の予め定められたタイミングおよび第2信号の予め定められたタイミングのそれぞれにおいてトリガ信号をサンプル装置に供給するトリガ供給部と、トリガ信号に応じてサンプル装置が出力する第1信号の平均値および第2信号の平均値に基づいて、サンプル装置が被測定信号を平均化するサンプル数が、平均化期間に応じたサンプル数であるか否かを判定する判定部と、を備える検査装置を提供する。

(もっと読む)

高周波パワーアンプ

【課題】

高周波パワーアンプの試験工程のコストを低減する。

【解決手段】

高周波パワーアンプは,インダクタを有する入力整合回路と,前記入力整合回路を通過した入力信号を増幅する増幅トランジスタと,入力整合回路内のインダクタに第1の試験スイッチにより接続されるキャパシタと,インダクタに第2の試験スイッチを介して第1の基準電圧との間に設けられた負性抵抗用トランジスタと,第2の基準電圧とインダクタとの間に設けられた電流源トランジスタとを含む試験用回路とを有し,試験時に第1,第2の試験スイッチ及び電流源トランジスタが導通してインダクタと試験用回路とで高周波発振器が構成され,通常動作時に第1,第2の試験スイッチ及び前記電流源トランジスタが非導通になる。

(もっと読む)

1 - 20 / 83

[ Back to top ]