Fターム[2G132AD08]の内容

電子回路の試験 (32,879) | 試験項目 (2,469) | 遅延時間、タイミング (406) | リングオシレータを用いるもの (13)

Fターム[2G132AD08]に分類される特許

1 - 13 / 13

半導体集積回路

発振回路およびテスト回路

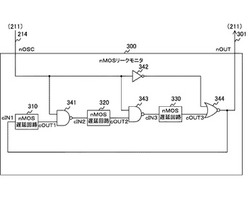

【課題】非導通状態におけるトランジスタから漏出するリーク電流を正確に測定することができるテスト回路を実現する。

【解決手段】遅延回路は、制御トランジスタ、測定対象トランジスタおよびコンデンサを備える。制御トランジスタは、入力端子の電位に応じて導通状態および非導通状態のうちのいずれかに移行することにより出力端子の電位を変化させる。チャネルの極性が前記制御トランジスタと同一の測定対象トランジスタは、電源とアースとの間において制御トランジスタに直列に接続される。コンデンサは、制御トランジスタが導通状態から非導通状態へ移行した場合に測定対象トランジスタから漏出したリーク電流の値に応じて出力端子の電位の変化を遅延させる。反転回路は、出力端子の電位を反転して前記入力端子に帰還させる。

(もっと読む)

電源電圧設定方法及び電源電圧設定プログラム

【課題】チップごとに適正な電源電圧を設定する。

【解決手段】チップのレイアウトデータ20からクリティカルパスのゲート遅延と配線遅延の遅延比を抽出する(ステップS1,S2)。チップのモニタ回路で実測されたゲート遅延及び配線遅延を、その遅延比に基づき合成して第1遅延値を生成し(ステップS3)、モニタ回路のシミュレーションで得られるゲート遅延及び配線遅延を、その遅延比に基づき合成して第2遅延値を生成する(ステップS4,S5)。このようにゲート遅延、配線遅延、クリティカルパスでの遅延比が考慮された第1遅延値及び第2遅延値に基づいて、チップに適用するチップ電源電圧を設定する(ステップS7)。

(もっと読む)

半導体集積回路及び誤動作防止方法

【課題】実システム動作中に電源状態を監視できる手段を提供する。

【解決手段】半導体集積回路は、発振器14と、電源電圧に応じて発振周波数が変化するリング発振器11と、発振器14の信号に基づいて、所定の判定期間を計測するインターバルタイマ13と、判定期間にリング発振器11が発振する発振周波数を測定する周波数測定用カウンタ12と、発振周波数の上限値と下限値とを保持する不揮発性メモリ15と、カウンタが測定した発振周波数が、不揮発性メモリ15が保持する上限電圧/下限電圧の判定コードの範囲内であるかを判定し、判定結果を出力する電圧判定回路16と、を備える。

(もっと読む)

半導体集積回路および電源供給方法

【課題】チップ内でデバイス特性にバラツキがあっても、消費電力を低減させることのできる半導体集積回路および電源供給方法を提供する。

【解決手段】実施形態の半導体集積回路1は、それぞれの領域に半導体デバイスが配置された領域1および領域2を有し、電源供給手段である電源端子T1、T2が、領域1、領域2それぞれに個別に電源を供給する。領域1にはデバイス特性測定回路ROSC1が配置され、領域2にはデバイス特性測定回路ROSC2が配置されている。

(もっと読む)

集積回路およびウェーハを試験する無線周波数技術構造および方法

【課題】集積回路を有するウェーハの無線試験を行うためのウェーハ上に形成された試験回路を含む装置および方法を提供する。

【解決手段】ウェーハ16の外部にある試験ユニット12、および集積回路を含むウェーハ上に製造された少なくとも1つの試験回路14を含む。試験ユニット12は、RF信号を送信し、試験回路14に電力を供給する。試験回路14は、可変リング発振器を含み、集積回路の公称動作周波数での一連のパラメータ試験を実行し、試験結果を分析のために試験ユニット12に送信する。

(もっと読む)

半導体試験装置

【課題】DUTに入出力される信号間の遅延の検査を短時間で行うことを目的とする。

【解決手段】DUT1から出力された応答信号SB、SCに基づいて良否判定を行う複数のコンパレータ装置30、40を備えた半導体試験装置1であって、コンパレータ装置30は、基準となるストローブ基準信号に対して遅延を与えてストローブ信号STBを発生するストローブ信号発生部34と、コンパレータ装置40に入力された応答信号SCをストローブ信号発生部34に入力するための装置間接続経路L2と、ストローブ信号発生部34が発生したストローブ信号STBのタイミングでDUT1から入力した応答信号SBを判定する判定部35と、を備えている。

(もっと読む)

標準セルライブラリーの性能改善のための測定装置

【課題】TEGを通した標準セルライブラリーの性能を測定して検証するにおいて、内蔵された回路を使用することで、標準セルの性能を効果的に改善するための測定装置を提供する。

【解決手段】外部から入力されるイネーブル信号によって活性化され、測定結果値を出力するリングオシレータブロックと;前記各リングオシレータブロックから出力される測定結果値のうち一つまたはそれ以上を選択的に出力するデコーダーと;前記デコーダーの出力を定められた区間の間に受けて、その入力値の最大値と最小値との平均を出力するスタティスティックスアシスタと;を含んで標準セルライブラリーの性能改善のための測定装置を構成する。

(もっと読む)

半導体装置

【課題】簡単で効率的にAC特性評価が可能な半導体装置を提供する。

【解決手段】搭載される内部回路を構成するMOSFETと同一の製造工程で形成されたMOSFET素子を用いて構成されたリングオシレータと外部端子から供給されるタイミング信号により上記リングオシレータの発振信号を計数の開始と停止を行う周波数カウンタを形成する。評価時に出力回路により上記周波数カウンタの計数出力をさせる。制御判定回路を設けて、上記周波数カウンタの制御と、その計数出力が許容値内にあるか判定して判定結果を出力させる。上記タイミング信号として、複数のリングオシレータのそれぞれに対応して上記周波数カウンタの計数値が最大計数値内に収まるように異なる時間に設定する。

(もっと読む)

半導体集積回路装置とその測定方法ならびにAC特性測定システム

【課題】クロック発生回路、パルス発生回路の設置を不要とする回路の提供。

【解決手段】AC測定対象のフリップフロップをリングオシレータのループ内に配設し、フリップフロップには、前記ループ内を伝播する信号から生成されたデータ及びクロックが入力され、フリップフロップから出力されるデータが前記ループ内に送出され、フリップフロップに与えるクロック信号を、前記ループ内を伝播する信号より生成するクロック生成回路と、フリップフロップに与えるデータ信号の遷移エッジとクロック信号の有効エッジとの間の遅延を、可変に制御する遅延調整回路と、フリップフロップに与えるデータ信号の遷移エッジとクロック信号の有効なエッジとの間のタイミングの前後関係を切り替えるセットアップホールド切替回路を備え、前記ループの所定のノードの発振が停止した時点の制御信号の値からAC測定値を導出する。

(もっと読む)

電子コンポーネントに問い合わせをする方法および装置

電子コンポーネント(20)に問い合わせする方法および装置が、問い合わせデバイスが前記電子コンポーネント(20)に物理的に接触することなく前記電子コンポーネント(20)への複数回の離散的な問い合わせを信頼できる形で実行する際に、該問い合わせデバイス(48/50または106)がコンジットとして使うためのインターフェース(10、24、108または54)をもつボディ(18または102)を含む。  (もっと読む)

(もっと読む)

回路シミュレーション方法

【課題】トランジスタの電気的特性を精度よく再現できる半導体集積回路のシミュレーション方法を提供する。

【解決手段】半導体集積回路のシミュレーション方法は、TEGに搭載した実デバイスの測定値を用いて実デバイスのDC特性とAC特性を再現する回路情報を抽出し、抽出した回路情報をネットリストに反映するステップと、回路シミュレーションを行うステップとを含んでいる。設計寸法と実仕上がり寸法の誤差に起因する回路シミュレーション誤差を低減できる。

(もっと読む)

半導体装置及びLSIを搭載したシステム

【課題】LSIのばらつきにより周波数仕様未達や電力仕様未達となり、不良品として破棄されていたLSIを救済する。

【解決手段】各LSIの性能を検出する性能検出部と、前記性能検出部の検出結果に基づいて前記LSIの最適動作電圧に関する値を決定する最適電圧決定部と、前記LSIへの供給電圧を制御する制御信号を前記最適電圧決定部の決定に基づいて生成する電圧制御信号生成部と、を備え、標準電源電圧が印加されたとき、前記LSIの動作周波数又は消費電力が規定範囲外となる場合に、前記制御信号のデューティ比によって前記電圧可変電源の出力電圧を変更し、前記LSIに接続される電圧可変電源は、前記制御信号によって、前記標準印加電圧とは異なる印加電圧を前記LSIに供給する。

(もっと読む)

1 - 13 / 13

[ Back to top ]