Fターム[2G132AE23]の内容

電子回路の試験 (32,879) | 試験装置(テストヘッドを除く) (4,743) | 制御回路 (1,346) | プログラムによる制御 (494)

Fターム[2G132AE23]に分類される特許

121 - 140 / 494

複数の命令タイプを使用するシステム・テスティングの方法および装置

テストされるシステムの少なくとも一部をテスト・アクセス・ポート(TAP)を介してテストする際に使用される装置を提供する。この装置は、テスト命令セット・アーキテクチャの命令のセットを格納するメモリと、テストされるシステムの少なくとも一部をTAPを介してテストするためにテスト命令セット・アーキテクチャの命令のセットを実行するプロセッサとを含む。テスト命令セット・アーキテクチャの命令のセットは、プロセッサによってサポートされる命令セット・アーキテクチャ(ISA)の複数の命令を含む命令の第1セットと、TAPに関連する複数のテスト命令を含む命令の第2セットとを含む。命令の第1セットの命令および命令の第2セットの命令は、テスト命令セット・アーキテクチャの命令のセットを形成するために統合される。  (もっと読む)

(もっと読む)

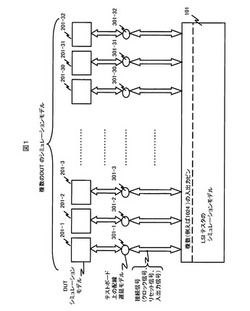

複数のデバイスアンダーテスト(DUT)の同時テストに対応したヴァーチャルテストシステム

【課題】より正確なテストプログラムのデバグを十分に行うことができるようにする。

【解決手段】ヴァーチャルテストシステムにおいて、複数のデバイスアンダーテスト(DUT)に対応して設けられた複数の半導体の動作シミュレーションモデル201−1〜201−32と、複数のDUTを同時にテストするLSIテスタの動作シミュレーションモデル101と、複数のDUTを実装するテストボード上の信号遅延モデル301−1〜301−32とを備え、複数の半導体の動作シミュレーションモデル201−1〜201−32と前記LSIテスタの動作シミュレーションモデル101とを接続する信号線に、テストボードにおける前記信号線に対応した信号遅延モデル301−1〜301−32を付加した。

(もっと読む)

データ解析のための方法および装置

【課題】データ解析のための方法および装置、特に半導体試験データ解析に適したデータ解析のための方法および装置を提供すること。

【解決手段】本発明の種々の側面にしたがうデータ解析のための方法と装置は、コンポーネントに対する試験データのようなデータ内の統計的外れ値(大きなデータ母集団のサブセット内の外れ値を表す混成外れ値を含む)を識別する。本発明の種々の側面にしたがう方法および装置は、半導体をテストするための自動テスト設備(ATE)のようなテスタを有するテストシステムと協働し得る。外れ値は、データの分布に従って識別および分類することができる。

(もっと読む)

故障解析装置

【課題】被テストデバイスの不良箇所の位置を3次元的に特定する。

【解決手段】故障解析装置70には、被テストデバイスである半導体デバイス(DUT)21にレーザ光を照射して、照射された被テストデバイスの特定箇所を加熱して熱起電流を発生させるレーザ照射手段と、前記レーザ光を水平方向及び垂直方向に走査して前記被テストデバイスの光加熱抵抗変化画像を撮影する撮影手段と、水平方向の前記光加熱抵抗変化画像と前記被テストデバイスの平面レイアウト画像を水平方向の位置座標が同一となるように重ね合わせる第1の位置座標設定手段と、縦方向の光学ステージ位置情報と前記被テストデバイスの断面情報を縦方向の位置座標が同一となるように重ね合わせる第2の位置座標設定手段とが設けられる。

(もっと読む)

試験結果表示装置

【課題】不良発生の原因や傾向をロット単位又はウェハ単位で容易に把握することができる試験結果表示装置を提供する。

【解決手段】ウェハマップ表示装置15は、複数のウェハ上に形成されたDUTに対する試験によって得られた試験結果から、ウェハ上の位置が同じであるDUTについての試験結果を検索するデータ検索部21aと、データ検索部21aによって検索された試験結果を重ね合わせたウェハマップを作成するウェハマップ作成部21bと、ウェハマップ作成部21bで作成されたウェハマップを表示装置15bに表示する表示制御部22とを備える。

(もっと読む)

半導体集積回路の故障解析方法、故障解析装置、及び故障解析プログラム

【課題】半導体検査装置から得られた半導体集積回路の異常信号と関連する回路を精度よく抽出する半導体集積回路の故障解析方法、故障解析装置、及び故障解析プログラムを提供する。

【解決手段】半導体検査装置より得た半導体集積回路の解析データに含まれる異常信号データについて解析データにおける装置座標系の座標を求める信号検出工程と、半導体集積回路の複数の基準点について装置座標系の座標と半導体集積回路の設計データにおける設計座標系の座標との対応を求め、装置座標系と設計座標系との座標変換式を求める座標変換工程と、座標変換式による装置座標系の座標と設計座標系の座標との位置誤差を求める誤差算出工程と、座標変換式と位置誤差とを用いて、装置座標系における異常信号の座標から、設計データにおける異常信号に関連する回路を抽出する回路抽出工程と、を有する。

(もっと読む)

不良解析方法、不良解析システムおよびメモリマクロシステム

【課題】使用者にとってわかりやすいFBMを作成する。

【解決手段】メモリマクロ内に配置された通常セル領域およびスペアセル領域の個数および各セル領域のサイズを含む構成情報を回路設計情報から抽出する構成情報抽出工程(S2)と、メモリマクロに配置された通常セル領域およびスペアセル領域を含めた全てのセル領域に含まれる各メモリセルが不良であるか否かを示す電気テスト結果を順次収集する電気テスト結果収集工程(S5)と、電気テスト結果の収集順に対応する配列情報を構成情報に基づいて2次元座標値に変換する2次元座標値算出工程(S8、S9)と、通常セル領域とスペアセル領域とが識別可能なように電気テスト結果を2次元座標値に基づいて表示する出力工程(S10、S11)と、を備える。

(もっと読む)

解析IDDQテストモジュール及びIDDQテスト方法

【課題】測定手段及び解析手段をBOST化することで高精度な測定と比較的大きなデータ処理(解析)を高速で実行でき、テスト時間の短縮を図る手段を提供する。

【解決手段】解析IDDQテストモジュール200中に平均値処理用連続サンプリング回路202を設ける。一度半導体試験装置100からトリガ信号が平均値処理用連続サンプリング回路202に入力されると、平均値処理用連続サンプリング回路202が規定の回数繰り返してIDDQ測定をIDDQ測定部201に実行させる。測定時のIDDQの値は高精度ADC203にてAD変換が行われモジュール制御部に送られる。モジュール制御部はデータ解析部207などで利用可能なデータを共用するデータ記憶部206に保存する。

(もっと読む)

半導体試験装置

【課題】半導体試験装置に備えられる複数の電源をテスト対象の被試験デバイスに応じて最適にオン・オフ制御することにより消費電力の低減を図ることを目的とする。

【解決手段】被試験デバイスのテストを行う複数のテストモジュールと各テストモジュールに電源を供給する複数の電源部とを備える半導体試験装置であって、前記電源部にそれぞれ備えられ、前記電源部をオンまたはオフに切り替える電源切替部と、前記被試験デバイスのテストを行うためのテストプログラムに記述されている前記テストモジュールの使用情報に基づいて、前記電源部をオンまたはオフに切り替えるための電源制御信号を生成して前記電源切替部に出力する電源制御部と、を備えている。

(もっと読む)

吸収電流像を利用した半導体検査方法及び装置

【課題】指定された配線の不良位置を自動で検出する装置を提供する。

【解決手段】試料にプローブと電子線を当て試料に吸収された吸収電流の像を利用して、長い配線でも不良位置を自動で検出する装置とその方法。プローブを当てたまま真横へ移動しながら吸収電流画像を取得し、その画像の吸収電流像を基にイメージシフトとステージの両方で補正する。試料回転ステージのないステージでバックラッシュ等の正しい角度で移動しないハード要因を含めて対策し、正確に長い配線の端まで移動しても配線を表示し続け、自動で配線の両端まで数往復する間に不良位置を検出する。

(もっと読む)

半導体試験装置及び半導体試験方法

【課題】ユーザの負担を増大させることなしにユーザの待ち時間を短縮することで効率的に信号波形を観察することができる半導体試験装置及び半導体試験方法を提供する。

【解決手段】半導体試験装置1は、DUT30に試験信号S1〜Snを印加して得られる信号D1〜Dnと所定の判定電圧値とを比較するコンパレータ15bと、コンパレータ15bの比較結果と予め定められた期待値とが一致するか否かを所定のタイミングで判定する判定部16と、判定部16の判定結果が変化する変化点を示す変化点情報を判定部16に設定される判定タイミング毎に記憶する記憶部25と、判定部16に設定した判定タイミングについての変化点情報が記憶部25に記憶されている場合に、コンパレータ15bに設定すべき判定電圧値と記憶部25に記憶されている変化点情報との大小関係に応じてDUT30に対する試験を実施するか否かを制御する制御部24とを備える。

(もっと読む)

診断装置、診断方法および試験装置

【課題】診断時における使用者の負担を軽減することができる。

【解決手段】被試験デバイスを試験する複数の試験モジュールを備える試験装置を診断する診断装置であって、複数の試験モジュールのそれぞれの種類および接続関係が記述された構成情報を記憶する構成記憶部と、構成情報に基づいて、複数の試験モジュールのそれぞれを診断するための診断用パターンを記述したパターンファイルを生成する生成部と、複数の試験モジュールのそれぞれに対して、対応する診断用パターンに応じた診断用信号を発生させて、それぞれの試験モジュールを診断する診断部と、を備える診断装置を提供する。

(もっと読む)

半導体試験装置及び半導体試験方法

【課題】ユーザの負担を増大させることなしにユーザの待ち時間を短縮することで効率的に信号波形を観察することができる半導体試験装置及び半導体試験方法を提供する。

【解決手段】半導体試験装置1は、DUT30に試験信号S1〜Snを印加して得られる信号D1〜Dnと判定電圧値とを比較するコンパレータ15bと、この比較結果と期待値とが一致するか否かを所定のタイミングで判定する判定部16と、予め設定された最小値から最大値まで判定電圧値の大きさを徐々に変化させつつ判定部16の判定結果を取得する第1制御を行い、第1制御が終了する前に取得した判定結果が変化した場合には、判定部16における判定のタイミングを所定量だけ変化させてから第1制御を新たに開始する第2制御を行う制御部24と、制御部24で取得された判定結果を用いてDUTから得られる信号D1〜Dnの信号波形を表示部23に表示する表示制御部26とを備える。

(もっと読む)

半導体試験装置

【課題】ユーザに対して煩雑な作業を強いることなしに直流試験の試験結果を容易に把握することができ、これにより試験効率を高めることができる半導体試験装置を提供する。

【解決手段】半導体試験装置1は、半導体デバイスに直流信号を印加して半導体デバイスから得られる直流信号が所定の規格内であるか否かの試験(直流試験)に用いられる複数の測定装置30a〜30nと、測定装置30a〜30nの各々から得られる測定結果と直流試験の試験条件(パス/フェイル判定に用いる直流信号の許容上限値及び許容下限値)とを関連付けたグラフを作成するグラフ作成部25と、グラフ作成部25で作成されたグラフを表示部27に表示する表示処理部26とを備える。

(もっと読む)

テストプログラムデバッグ装置、半導体試験装置、テストプログラムデバッグ方法、及び試験方法

【課題】テストプログラムの検証に多大な時間を要するという課題があった。

【解決手段】本発明のテストプログラムデバッグ装置は、被試験デバイスシミュレータ及び半導体試験装置シミュレータとを備える。そして、半導体試験装置シミュレータは、テストプログラムのうちの検証すべき命令の範囲である検証範囲を取得する検証範囲取得部と、テストプログラムのうちの検証範囲以外の範囲である非検証範囲に含まれる非検証範囲命令のうち、被試験デバイスシミュレータの設定を行うための設定命令以外の非設定命令を単純化する命令単純化部と、検証範囲に含まれる検証範囲命令、設定命令、及び命令単純化部によって単純化された非設定命令を実行する命令実行部とを有する。

(もっと読む)

半導体試験装置

【課題】ピンエレクトロニクスカードの測定データを格納するメモリ領域を増大させることなく制御ユニットに全ピンエレクトロニクスカードの測定データを収集するための処理時間を短縮できる半導体試験装置を提供する。

【解決手段】制御ユニット12により制御される多数のピンエレクトロニクスカード11を介して、多数の被測定対象の測定データを前記制御ユニット12に取り込むように構成された半導体試験装置において、前記各ピンエレクトロニクスカード11は、それぞれの測定データを前記制御ユニット12に直接書き込む。

(もっと読む)

プローブ装置、処理装置及びウェハプローブテストの処理方法

【課題】効率的なウェハプローブテストが可能なプローブ装置及び処理装置の提供。

【解決手段】プローブ装置200は複数の測定ステージ220とプローブカードを識別するための第1の識別子を複数のプローブカードから読み取る情報読み取り部260と測定ステージを識別するための第2の識別子が記憶された第1の記憶手段と第1の記憶手段から第2の識別子を読み取る情報読み取り部260と読み取った第1第2の識別子が対応付けられて記憶される測定ステージID記憶部212と搬送アーム230で測定ステージへ搬送された半導体ウェハに第1の検査を行う手段と処理装置から測定ステージの不使用を示す情報と第1及びまたは第2の識別子が対応付けられたステージ情報を受信する情報送受信部270と受信したステージ情報に基づいて、測定ステージへ半導体ウェハを搬送する搬送アーム230と搬送された半導体ウェハに第2の検査を行う手段を具備する。

(もっと読む)

チップの欠陥検出のために関連度値を判定し、チップ上の位置で欠陥確率を判定する方法及び装置

関連度値(R(i,m))を判定する方法を記載する。各関連度値は、チップ上の欠陥検出において、第1個数(I個)の入力ノードの入力ノード(i)と、第2個数(M個)の測定ノードの測定ノード(m)との組み合わせ((i,m))の関連度を表す。該方法は、第1個数(I個)の入力ノードで第3個数(K個)のテストを適用することと、第2個数(M個)の測定ノードの各測定ノード(m)につき、第3個数(K個)の測定値を得るため、第3個数(K個)のテストの各テスト(k)につき、第2個数(M個)の測定ノードの各測定ノードで信号を測定することと、関連度値(R(i,m))を判定することと、を含み、第3個数(K個)のテストの各テスト(k)は、各入力ノード(i)につき、テスト入力チョイス(U(k,i))を指定し、各測定値(Y(k,m))は、測定を行ったテスト(k)と測定が行われたところの測定ノード(m)に対応付けられ、各関連度値は、各組み合わせの入力ノード(i)に指定された第3個数(K個)のテスト入力チョイス(U(k,i))と、各組み合わせ(i,m)の測定ノード(m)に対応する第3個数(K個)の測定値(Y(k,m))との相関に基づいて計算される。 (もっと読む)

光子放出に基づいた欠陥検知のためのシステム及び方法

【課題】光子放出を利用して集積回路中の欠陥デバイスを検出する方法を提供する。

【解決手段】集積回路160の領域から放出画像(IREM)を取得するステップと、集積回路の前記領域に存在する各デバイスからの放出の決定強度を提供するために、強度の値を決定するステップと、各デバイスに対応する参照強度を取得するステップと、強度が参照強度に対して描画され、曲線適合計算が実行されて計算強度と参照強度との直線関係が取得され、最大偏差が、標準偏差計算のような計算によるか、ユーザによる手動入力によって、各決定強度を対応する参照強度と比較するステップとを備える。

(もっと読む)

ICテスト装置

【課題】テストモードへの移行状態を確認して効率的にICのテストを行なうことが可能なICテスト装置を提供すること。

【解決手段】テストモードに関する状態出力が可能なICをテストするICテスト装置であって、前記ICに対してテストモード移行確認を行ない、前記ICからテストモード移行確認が得られた場合には、ICテストを行なってテスト結果を出力し、前記ICからテストモード移行確認が得られなかった場合には、該テストモード移行確認が得られなかった回数が所定回数以内であるときには、再度前記ICに対してテストモード移行確認を行ない、該テストモード移行確認が得られなかった回数が所定回数を超えるときには、テストフェール判定を出力する、ICテスト装置。

(もっと読む)

121 - 140 / 494

[ Back to top ]