Fターム[2G132AE23]の内容

電子回路の試験 (32,879) | 試験装置(テストヘッドを除く) (4,743) | 制御回路 (1,346) | プログラムによる制御 (494)

Fターム[2G132AE23]に分類される特許

101 - 120 / 494

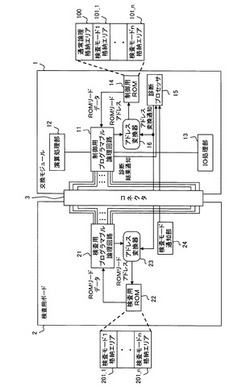

診断装置及び診断方法

【課題】交換モジュールの検査を低コストで実現すること。

【解決手段】本発明に係る診断装置1は、検査用プログラマブル論理回路21と、複数の検査モードの情報を格納する検査用記憶手段22と、を有する検査用ボード2と、制御用プログラマブル論理回路11と、複数の検査モードの情報を格納する制御用記憶手段14と、検査用ボード2が接続された場合に、検査用記憶手段22及び制御用記憶手段14に格納された複数の検査モードの情報に基づいて、検査用プログラマブル論理回路21及び制御用プログラマブル論理回路11を検査用の論理に置き換え、複数の検査モードを順次実行することで診断を行う診断プロセッサ15と、を有する交換モジュールと1、を備えるものである。

(もっと読む)

診断機能を備える装置、診断方法、およびプログラム

【課題】デバイスの生産性を下げないシステム。

【解決手段】複数の診断箇所の診断機能を備える装置であって、複数の診断箇所のそれぞれの診断不要期間を取得する取得部と、複数の診断箇所のうち、診断不要期間が経過している診断箇所を選択して診断する診断部と、を備える装置を提供する。複数の診断箇所のそれぞれに対応する診断インターバルを記憶する診断インターバル記憶部と、複数の診断箇所のうち診断部が診断した診断箇所の診断不要期間を、当該診断箇所に対応する診断インターバルにより更新する更新部と、を更に備えてもよい。

(もっと読む)

表示装置の検査装置

【課題】例えば、液晶プロジェクタ等の表示装置を検査する検査装置において、適切な検査を行う。

【解決手段】検査装置(100)は、表示装置(1100)に対して、複数のステップからなる検査を、ステップ毎に、表示装置の内部動作に影響を与える複数のパラメータのうち少なくとも一つの検査対象パラメータを変更させつつ、画像を投影するように表示装置を制御することによって、実行する検査装置であって、検査フローに含まれる第1ステップが実行された後に、第1ステップの次に実行されるべき第2ステップが実行されるように、前記表示装置を制御する第1制御手段(122)と、第1ステップが実行された後に、第1ステップの前に実行された第3ステップが実行されるように、前記表示装置を制御する第2制御手段(123)とを備える。

(もっと読む)

半導体試験装置

【課題】急峻に変化する試験信号或いは緩やかに変化する試験信号を生成することができ、これにより試験に要する時間の短縮やDUTに合わせた柔軟な対応を図ることができる半導体試験装置を提供する。

【解決手段】半導体試験装置1は、DUT40−1〜40−nに印加すべき試験信号を出力するDAC31と、DAC31から出力される試験信号をDUT40−1〜40−nに印加するか否かを切り替えるリレー33−1〜33−nと、2つの入力端の切り替えに要する時間がDAC31のセトリング時間よりも短く、一方の入力端に入力されるDAC31からの試験信号及び他方の入力端に入力される信号の何れか一方をリレー33−1〜33−nにそれぞれ出力するマルチプレクサ32−1〜32−nと、DAC31に対する試験信号の出力制御及びマルチプレクサ32−1〜32−nにおける切り替え制御を行う制御部12とを備える。

(もっと読む)

ディレイ故障診断プログラム

【課題】 半導体集積回路の故障診断に関し、ディレイ故障の故障箇所を高精度に特定する。

【解決手段】 故障仮定と終点フリップフロップFF抽出部116を設け、故障仮定情報より故障仮定を選択し、故障仮定より出力側に向かって論理トレースを実行する。故障仮定からトレースの結果得られた終点のフリップフロップFFのテスト結果を判定する(117)。終点のフリップフロップFFまでの伝搬経路の最大値と最小値を求め、そこからディレイ余裕度を求める。ディレイ余裕度と117で求めたテスト結果を用いてディレイ範囲を求め(118)、故障候補とディレイ範囲決定部119で故障候補とディレイ故障のディレイ範囲を特定する。

(もっと読む)

半導体製品ダイのテスト方法及び同テストのためのテストダイを含むアセンブリ

【課題】製品ダイ(2011,300)の製品回路(202,302,304)をテストするためのテストアセンブリ(2000)を提供すること。

【解決手段】一実施形態では、テストアセンブリは、テストダイ(2010,400)及び該テストダイをホストコントローラ(2002)へ電気的に結合する相互接続基板(2008)を含む。該テストダイは、テスト回路(202A,402,404)及び製品回路を統合化された設計(102)に同時に設計するステップを含むテストダイ及び製品ダイに関する設計方法論(100)に従って設計可能である。テスト回路は、該テスト回路により必要とされるシリコン領域の量にほぼ関係なく、対応する製品回路に関して高度の欠陥検出範囲を提供するよう設計可能である。次いで該設計方法論は、統合化された設計をテストダイ及び製品ダイへと分割する(104)。テストダイはテスト回路を含み、製品ダイは製品回路を含む。

(もっと読む)

配線故障検査装置及び方法

【課題】進行性断線・短絡故障の検出精度を向上させる。

【解決手段】本発明は、少なくとも2つのチップ間を接続するチップ間配線の故障を検査する配線故障検査装置1であって、前記検査の対象となるチップ間配線に、該検査の種類に応じた検査電流を流す経路を決定する検査電流経路決定部2と、前記検査電流を発生させるための最適な電源電圧を決定する電源電圧決定部3と、前記検査の対象となる対象チップ間配線と接続するバッファの出力と、前記検査の対象とならない非対象チップ間配線と接続するバッファの出力とを異ならせるバッファ出力制御部4とを備える。

(もっと読む)

LSIテスタ

【課題】新旧のシステムソフトウェアバージョンを切り替えて測定が行えるLSIテスタを提供する。

【解決手段】新旧バージョンのシステムソフトウェアを格納するシステムソフトウェア格納部33と、これらシステムソフトウェアのバージョン別の校正データを格納する校正データ格納部34と、DUTの機種に対応したテストプログラムを格納するテストプログラム格納部44と、これらテストプログラムとシステムバージョンとを対応付けたデータセット・システムバージョン対応テーブル35と、前記テストプログラム格納部から所望のテストプログラムを選択し、前記データセット・システムバージョン対応テーブルからこの選択されたテストプログラムに応じたシステムバージョンを選択し、前記バージョン別校正データ格納部から所定の校正データを読み出してテストシステムを駆動するインタフェース、とで構成されたことを特徴とするLSIテスタ。

(もっと読む)

LSIテスタ

【課題】無駄な消費電力を削減できるLSIテスタを提供する。

【解決手段】試験検査系統が多チャンネル化されたLSIテスタにおいて、テストヘッドTH、電源部1、ピンエレクトロニクス2、テスタコントローラ3、スイッチ4、スイッチ制御部5により構成され、DUTの種別に応じたプログラムに基づき、DUTのテストに使用する試験検査系統のみに電源部1の第1電源11、第2電源12、第3電源13および第4電源14から選択的に電源を供給する構成にする。

(もっと読む)

コンタクトパラメータの設定方法、コンタクトパラメータの設定用プログラム及びコンタクトパラメータの設定用プログラムが記録された記録媒体

【課題】コンタクトパラメータを視覚的に確認しながら設定して半導体ウエハのデバイスとプローブの接触工程全体をシミュレーションすることができるコンタクトパラメータの設定方法を提供する。

【解決手段】コンタクトパラメータの設定方法は、時間軸と高さ軸とからなる座標図1を用意する工程と、座標図1上で、半導体ウエハの各電極パッドと複数のプローブが電気的に離接する間の半導体ウエハの複数の昇降位置とこれらの昇降位置までにそれぞれ要する半導体ウエハの昇降時間をそれぞれ指定し、複数の指定点Pを直線で結んで折れ線グラフとして表示することにより半導体ウエハのコンタクトパラメータを設定する第2の工程と、を備えている。

(もっと読む)

データ分析用の装置および方法

【課題】データ分析に関する発明を提供すること。

【解決手段】本発明の種々の局面による半導体のテスト方法およびテスト装置は、2つ以上のデータセットからのデータを分析するよう構成された複合データ分析要素を備えるテストシステムを含んでいる。このテストシステムを、出力レポートにデータをもたらすように構成することができる。複合データ分析要素は、空間分析を適切に実行して、複合データセット内におけるパターンおよび不規則性を特定する。さらに、複合データ分析要素は、複合データ分析を洗練させるため、クラスタ検出システムおよび除外システムなど、他のさまざまな分析システムと関連して動作できる。さらに、複合データを、他のデータとマージすることができる。

(もっと読む)

半導体テストのための方法および装置

【課題】半導体をテストするための方法を提供すること。

【解決手段】本発明の様々な局面による半導体をテストするための方法および装置は、テスト結果のセットにおいて有効なデータを分類するように構成される。テストシステムは、出力レポートにおけるデータを提供するように構成され得る。アウトライヤー分類エレメントは、実行時に解析を適切に実行する。アウトライヤー分類エレメントは、さらに、データをスムージングし、かつ、テスト結果基準からの傾向および領域を分類するために、スムージングシステムと共に動作し得る。

(もっと読む)

回路モジュール、半導体集積回路、および検査装置

【課題】各回路モジュールの動作を制御する制御信号を流用することで、スキャンテストの効率化を図ること。

【解決手段】半導体集積回路100内のスキャンチェーンを構成する回路モジュールMは、選択回路103と、シフトレジスタと、クロックゲーティング回路102を有している。選択回路103は、スキャン信号を取り込む短絡パスとスキャン信号をシフトレジスタへ経由させて取り込む冗長パスのうち、制御信号生成回路101から供給される制御信号(EN_M)がシフトレジスタの動作を許可する場合、冗長パスを選択し、許可しない場合、短絡パスを選択する。

(もっと読む)

検出データ処理装置及びプログラム

【課題】回路基板における異常又は故障を高精度に検出することを支援する。

【解決手段】故障診断装置10の解析データ抽出部104は、回路基板の動作状態を検出する動作状態検出部1から取得された検出データの複数のグループについて互いに相関関係を求め、他のグループとの相関関係を表す値が予め設定された閾値よりも小さいグループの検出データを解析データとして選択し抽出する。第一マハラノビス距離算出部106は、正常な回路基板を動作させたときの検出データから解析データ抽出部104が抽出した解析データを用いて生成された第一のマハラノビス空間と、診断対象の回路基板を動作させたときの検出データと、に基づいて1段目のマハラノビス距離を算出する。

(もっと読む)

半導体試験装置および半導体試験方法

【課題】演算処理に応じてDSPモジュールを逐次的に実行させるのか、並列的に実行させるかを最適に選択し、演算時間の短縮化を図ることを目的とする。

【解決手段】複数のCPUを備えるDSPモジュール4と演算処理が記述されたテストプログラムに従ってDSPモジュール4の制御を行うテスタコントローラ3とを備える半導体試験装置であって、テスタコントローラ3に備えられ、テストプログラムに記述されている演算処理に基づいて、DSPモジュール4に演算処理を逐次的に実行させるシングルモードと並列的に実行させるマルチモードとのうち何れか一方の動作モードを選択する動作モード選択部15と、DSPモジュール4に備えられ、動作モード選択部15の選択に基づいて1つのCPUを逐次的に動作させるか2つ以上のCPUを並列的に動作させるかの選択を行うCPU制御部24と、を備えている。

(もっと読む)

組合せ型スイッチングマトリクスの構築方法およびその半導体装置の試験システム

【課題】 組合せ型スイッチングマトリクスの構築方法において、使用者の作業効率を高めるとともに、試験コストを削減する。

【解決手段】 第1と第2のスイッチングモジュールを選択し、第1と第2のスイッチングモジュールの出力ポートおよび入力ポートを設定し、少なくとも第1の出力ポートうちの一つと第2の入力ポートのうちの一つとを接続することで、組合せ型スイッチングマトリクスを形成し、出力ポートと入力ポートとの接続関係に基づいて接続マッピングテーブルを作成し、チャネル切換えインターフェイスを表示する。チャネル切換えインターフェイスは、複数の入力端子と、出力端子と、仮想スイッチとを備え、入力端子および出力端子の間の経路のオン・オフ状態を表す組合せ型スイッチングマトリクスを表示する。

(もっと読む)

製品試験装置、ロット管理方法およびプログラム

【課題】 製品試験装置の自己診断結果に異常が発見された場合における影響を受ける範囲の特定の容易化。

【解決手段】 製品試験装置は、試験対象の製品に応じて試験条件を設定し、前記試験条件を用いて試験を行った製品のロット情報を前記試験条件と関連付けて記録していく。前記自己診断機能による自己診断結果が出る度に、前記自己診断結果と、前記試験条件とを照合し、前記自己診断結果による影響を受ける試験条件にて試験を行った製品のロット情報を出力する。

(もっと読む)

半導体試験装置

【課題】DUTからの信号と所定の期待値との比較を行う比較器とその比較結果であるフェイル情報を記憶するフェイルメモリとの対応付けの自由度を高め、これによりプローブカード等の設計自由度の向上及び製造コストの削減を図ることができる半導体試験装置を提供する。

【解決手段】半導体試験装置1は、被試験対象である複数のDUT20−1〜20−nから出力される信号と期待値パターンE1〜Emとの比較を行う論理比較器17−1〜17−mと、論理比較器の各々に対して一意に対応付けられており、論理比較器の比較によって得られるパス/フェイルの判定結果を示すフェイル情報を記憶する複数のフェイルメモリ19−1〜19−nと、論理比較器とフェイルメモリとの間に設けられ、論理比較器とフェイルメモリとの対応付けを変更する経路変換器18−1〜18−mとを備える。

(もっと読む)

回路基板検査装置、サーバー、回路基板検査システム

【課題】故障部位を特定することは容易ではない。そのため、回路基板検査装置の修理に要する時間が長くなってしまうという課題がある。

【解決手段】被検査回路基板Sを順次検査し、被検査回路基板Sごとの検査結果を出力する検査部4と、文字や画像を表示するディスプレイ2と、検査結果が異常であることを示すエラー情報としてのエラーコードを検査部4から取得すると、サーバー30にエラーコードを送信するエラー情報送信部10と、サーバー30から送信された検査部4のエラーコードに対応する修理情報としての修理内容を取得する修理情報取得部11と、修理内容をディスプレイ2に表示する修理情報表示部12と、を備えた回路基板検査装置1を提供する。

(もっと読む)

電源供給支援プログラム、電源供給支援装置および電源供給支援方法

【課題】半導体集積回路におけるマクロ試験時の消費電力を削減すること。

【解決手段】電源供給支援装置100では、試験対象回路110内の電源供給先としてあらかじめ分類されているグループ1〜4のうち、試験対象となる素子を含むグループを抽出することによって、マクロ試験時に正しい試験結果を得るために電源供給先を特定することができる。ここで特定した電源供給先にのみ電源を供給させることによって、マクロ試験時の電源供給を必要最低限に抑えることができる。

(もっと読む)

101 - 120 / 494

[ Back to top ]