Fターム[2G132AG08]の内容

電子回路の試験 (32,879) | 信号の印加に関するもの (2,293) | クロックパルス、タイミング信号 (573)

Fターム[2G132AG08]に分類される特許

1 - 20 / 573

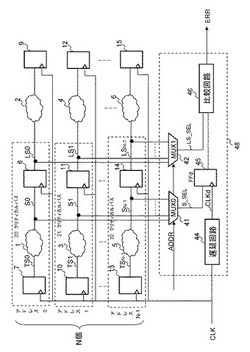

半導体装置

【課題】複数箇所のタイミング違反検出を、小規模な回路構成で実現する。

【解決手段】選択信号に基づいて、複数の信号からいずれか1つを選択する第1のセレクタと、上記選択信号に基づいて、ラッチされた複数の信号からいずれか1つを選択する第2のセレクタと、クロック信号CLKを所定時間遅延する遅延回路と、遅延回路により遅延したクロック信号に同期して、第1のセレクタの出力をラッチするタイミング違反検出用フリップフロップ回路と、タイミング違反検出用フリップフロップ回路の出力と第2のセレクタの出力とを比較する比較回路とを、備える。複数の信号に対し、個別に回路を設けることなく、1つのタイミング違反検出回路で構成することができる。

(もっと読む)

半導体集積回路設計装置、半導体集積回路設計方法、および、プログラム

【課題】半導体集積回路において、スキャンテスト時における消費電力を削減する。

【解決手段】半導体集積回路設計装置は、第1のスキャンFFのデータ入力端子に接続された第1のロジックコーンの入力端子数である第1の入力端子数と、第1のロジックコーンにデータを設定する第2のスキャンFFのデータ入力端子に接続された第2のロジックコーンの入力端子数である第2の入力端子数とを比較するデザイン解析部と、複数のスキャンFFのそれぞれのデータ入力端子に接続されたロジックコーンの入力端子数、および、複数のスキャンFFのそれぞれを第1のスキャンFFとした場合の前記比較結果に応じて、複数のスキャンFFを複数のグループに分類し、複数のグループのそれぞれに含まれるスキャンFFを相互に接続したスキャンチェーンを複数のグループのそれぞれについて生成するスキャンチェーン構築部と、を備える。

(もっと読む)

半導体集積回路のテスト回路及びテスト方法

【課題】外部端子数の増加を抑えつつ、半導体集積回路のテスト時間を短縮する。

【解決手段】テスト回路は、入力されるリファレンスクロック109を逓倍して、テスト対象回路106をテスト動作させるための実動作クロック112及びサンプリングクロック105を生成するPLL108と、入力されるテストコマンドに従い、テスタ同期クロック103に同期してテスト対象回路106のテスト結果を出力するテスト結果出力回路107と、を備えるテスト回路であって、テストコマンドを含むテスト入力信号104とサンプリングクロック105とに基づきテスタ同期クロック103を生成するテスタ同期クロック生成回路100を備えるものである。

(もっと読む)

集積回路および集積回路の制御方法

【課題】タイミングエラーの種類を判別することができる集積回路を提供する。

【解決手段】エラー測定部は、同期動作回路に入力されているデータ信号が第1の期間内に変化した場合には同期動作回路における第1のタイミングエラーを検出する。また、エラー測定部は、第1の期間の前または後に所定の長さのエラー警告期間を加えた第2の期間内に前記データ信号が変化した場合には同期動作回路における第2のタイミングエラーを検出する。エラー補償制御部は、第1および第2のタイミングエラーがともに検出された場合には第1および第2のタイミングエラーの検出結果の履歴に基づいてタイミングの前後のいずれにおいて前記データ信号が変化したかを判断する。

(もっと読む)

半導体集積回路検査装置,および,半導体集積回路の検査方法

【課題】テスト時間をより短縮するテストパターンを作成する半導体集積回路検査装置,および,半導体集積回路の検査方法を提供する。

【解決手段】半導体集積回路検査装置20は,テストパターンを複数の区間に分割した分割テストパターン毎に,分割テストパターンに対する論理演算を異なる周期のクロック信号に基づき半導体集積回路に実行させることにより得られた半導体集積回路31の故障判定結果に基づき,分割テストパターン毎の最適クロック周期を算出する最適周期算出部213と,テストパターンと,テストパターンに係る分割テストパターン毎の最適クロック周期を有するテストパターンファイルを生成する新テストパターンファイル生成部214を有する。

(もっと読む)

半導体集積回路装置の試験方法及び半導体集積回路装置

【課題】 半導体集積回路装置の試験方法及び半導体集積回路装置に関し、所定の回路動作を行った状態のまま半導体集積回路装置側の操作で所望の温度に制御する。

【解決手段】 スクリーニング試験前の工程にて測定された半導体集積回路装置の回路毎の電源電流値或いは電流ランクのいずれかにより、前記半導体集積回路装置全体毎または個別の回路動作毎に、適切な周波数に周波数設定し、所望の発熱量になるよう発熱量の制御を行い、スクリーニング試験時に、所定の回路動作を行った状態のまま所望の温度に制御する。

(もっと読む)

半導体試験装置における電気長測定方法

【課題】ウェハを対象とした半導体試験装置において、簡易にプローブ先端を接地状態として電気長測定を行なえるようにする。

【解決手段】試験対象のウェハと接触するプローブを複数備えた半導体試験装置における、プローブを一端とする信号経路の電気長測定方法であって、電気伝導性領域を有するキャリブレーションウェハの電気伝導性領域を全プローブに接触させ、信号経路の他端から測定信号を入力し、電気伝導性領域との接触部で反射した信号波形を他端側で測定することにより電気長を算出する。

(もっと読む)

半導体集積回路

【課題】テスト時の消費電力を低減することができる半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路100は、フリップフロップFF、制御回路10及び排他的論理和ブロックを有する。フリップフロップFFは、テスト入力Tにテストデータ信号TINが入力する。排他的論理和ブロック20は、一方の入力がフリップフロップFFのテスト入力Tと接続され、他方の入力がフリップフロップFFの出力Qと接続される。制御回路10は、排他的論理和ブロック20の出力XORとクロック信号CLKとが入力し、排他的論理和ブロックの出力XORの値に応じてフリップフロップFFへのクロック信号CLKの出力を制御する。

(もっと読む)

半導体集積回路及びその制御方法

【課題】精度の高いディレイテストを行うことが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路1は、クロック信号CLKに同期して動作する複数のレジスタを有する内部回路11と、クロック信号CLKに同期して動作し第1ノードから第2ノードまでの信号伝搬時間を測定する遅延測定回路12と、遅延測定モードの場合に、遅延測定回路12に対してのみクロック信号CLKを供給し、電圧検出モードの場合に、内部回路11及び遅延測定回路12に対してクロック信号CLKを供給するクロック供給回路13と、を備える。

(もっと読む)

試験装置および試験方法

【課題】精度良く被試験デバイスを試験する。

【解決手段】データ信号とクロック信号とを授受する被試験デバイスを試験する試験装置であって、被試験デバイスにデータ信号およびクロック信号を試験信号として供給する試験信号供給部と、被試験デバイスが出力するデータ信号を、被試験デバイスが出力するクロック信号に応じたタイミングで取得するデータ取得部と、データ取得部が取得したデータ信号を期待値と比較した比較結果に基づいて被試験デバイスの良否を判定する判定部と、調整時において、データ信号を取得するタイミングを生成するためのクロック信号の遅延量を調整する調整部とを備える試験装置を提供する。

(もっと読む)

パターンプログラム作成支援装置、コンピュータプログラム

【課題】高速パターン発生器と、低速パターン発生器とを備えた半導体試験装置で、希望する低速レート時間長とサイクル比とで半導体試験を行なえるようにする。

【解決手段】高速パターン発生器の分解能の設定を受け付けるパターン発生器パラメータ設定部と、作成対象のパターンプログラムの低速レート時間長と、サイクル比の設定を受け付けるプログラム条件設定部と、低速レート時間長をサイクル比で割った値未満で最も大きい分解能の倍数を切捨てレート時間長とし、値超で最も小さい分解能の倍数を切上げレート時間長とするレート時間長算出部と、低速レート時間長に対応する高速パターンのサイクルにおける切捨てレート時間長の個数と切上げレート時間長の個数とを、合計のレート時間長が低速レート時間長と等しくなるように設定する個数設定部とを備えたパターンプログラム作成支援装置。

(もっと読む)

半導体集積回路のスキャンテスト回路の設計方法、スキャンテスト回路、およびスキャンテスト方法

【課題】半導体集積回路にスキャンパスを組み込んでスキャンテストを行う際に、シングルサイクルパスとマルチサイクルパスが混在している論理回路において、シングルサイクルパスの実動作速度によるテストを可能にすること。

【解決手段】実動作モードでタイミング解析を行い、マルチサイクルパスを抽出する。次に、シングルサイクルパスとマルチサイクルパスの分岐点と、シングルサイクルパスとマルチサイクルパスの合流点を抽出する。そして、上記分岐点から出力側のマルチサイクルパス側の経路上と、上記合流点から入力側のマルチサイクルパス側の経路上に、出力固定回路を挿入する。但し、出力固定回路は、マルチサイクルテスト時には、入力と同じ信号を出力し、シングルサイクルテスト時には、任意の固定値を出力する回路である。

(もっと読む)

半導体装置、試験プログラム、試験方法、および試験装置

【課題】特定パスの動作確認を容易化し、不具合箇所の特定を容易化すること。

【解決手段】選択回路101は、入力信号が入力端子120から受け渡される半導体装置110内の特定パス上の観測箇所Aと観測箇所Bとが選択信号に応じて順に選択される。カウンタ102は、選択された観測箇所ごとに観測箇所でのエッジ数をカウントする。第1のレジスタ103は、カウンタ102によりカウントされた観測箇所Aでの第1のエッジ数を保持する。第2のレジスタ104は、カウンタ102によりカウントされた観測箇所Bでの第2のエッジ数を保持する。比較回路105は、第1のレジスタ103に保持された第1のエッジ数と第2のレジスタ104に保持された第2のエッジ数とを比較し、出力端子106は、比較回路105による比較結果を出力する。

(もっと読む)

半導体試験装置

【課題】複数のドライバのタイミングを校正するときに、高い精度のタイミング校正を行うことを目的とする。

【解決手段】本発明の半導体試験装置は、DUT1に信号を出力するドライバ10およびドライバ10に接続されるコンパレータ11とドライバ10のタイミングを校正するために設けた基準コンパレータ6との間の校正経路Lに信号を反射する複数の半導体スイッチ15が設けられる半導体試験装置2であって、コンパレータ11がドライバ10から出力されて基準コンパレータ6で反射した校正信号を検出するときに、半導体スイッチ15で多重反射した反射信号が校正信号の検出に干渉しないように、校正経路Lを基準コンパレータ6が分割した各分割経路L1〜L3の電気長Tpd1〜Tpd3を設定している。

(もっと読む)

半導体装置及びそのテスト方法

【課題】従来の半導体装置では、電源電圧変動を抑制するために回路規模が大きくなる問題があった。

【解決手段】本発明の半導体装置は、テスト対象回路11〜13と、スキャンモード制御信号SMCと、ノイズ制御信号CNTと、クロック信号CLKと、テストパターンSINとが入力され、テスト対象回路12に対するテストを行うテスト回路20と、を有し、テスト回路20は、ノイズ制御信号CNTがイネーブルであるダミーノイズ生成期間にテスト回路20において保持されているテストパターンSINに基づくテスト値を維持し、ダミーノイズ生成期間にクロック信号CLKの周期に応じて変動するダミー電源ノイズを生成し、ダミーノイズ生成期間の終了後にテストパターンによりテスト対象回路12をテストする。

(もっと読む)

プリント基板劣化検査装置および劣化検査方法

【課題】プリント基板を破壊することなく、故障発生前にプリント基板またはプリント基板上の回路(検査部位)の修理もしくは交換を容易にできる劣化検査装置を提供する。

【解決手段】プリント基板劣化検査装置は、パルス波を出力するパルス発生器51と、プローブ32と、オシロスコープ53と、コンピュータ60とを備える。プローブ32は、検査部位と接続されたプリント基板上の配線パターンにパルス波を印加するために用いられる。オシロスコープ53は、パルス波がプリント基板から反射された反射波を、プローブ32を介して測定する。コンピュータ60は、プリント基板または検査部位に対して測定された反射波と比較のための参照用波形に基づいて、プリント基板あるいは検査部位の劣化を判定する。

(もっと読む)

遅延時間測定装置および遅延時間測定方法

【課題】フリップフロップ間のパスの数が増えると、遅延時間を測定するために必要なフリップフロップ数が大きく増加する。

【解決手段】遅延時間測定装置は、第1のクロックと第2のクロックとを出力するクロック生成部と、第1のクロックのエッジに同期して第1の信号を出力する第1のフリップフロップと、第1の信号を入力とし、第2のクロックのエッジに同期して第2の信号を出力する第2のフリップフロップと、第2の信号を入力とし、第1のクロックのエッジに同期して第3の信号を出力する第3のフリップフロップと、第1のクロックの第1のエッジが生成された時から第2のクロックの第1のエッジが発生されるまでの第1の設定時間と、記第2のクロックの第2のエッジが生成された時から第1のクロックの第2のエッジが生成されるまでの第2の設定時間とを制御する制御部と、を有する。

(もっと読む)

ジッタ付加装置およびジッタ付加方法

【課題】

ジッタ付加装置のジッタ発生量の出力値が発生量保証値に達した場合であっても、さらなるジッタ発生量にて試験を続行しながらもユーザが直感的にジッタ発生量の出力値が発生量保証値に達したことを把握することができるようにする。

【解決手段】

ジッタの発生量を含むパラメータを任意に設定するとともに、ジッタを付加する種別であるジッタ種別から任意の複数のジッタ種別を設定する操作部10と、ジッタを付加するためのジッタ付加部14とを備えたジッタ付加装置1において、ジッタの発生量の出力値が保証可能な値である発生量保証値を複数のジッタ種別の組合せにそれぞれ対応させてパラメータ値として予め記憶したジッタ発生量記憶部13と、任意に設定したジッタの発生量がジッタ発生量記憶部に記憶された発生量保証値に達したか否かを判定する発生量保証値判定部12bとを備えた。

(もっと読む)

テスト回路、及び、シリアルI/F回路、半導体装置

【課題】半導体パッケージにテストモード時にのみ使用される端子を設けなくても、テストモードの設定及びテストモード設定後のテスト信号入力ができるテスト回路を提供する。

【解決手段】複数の電圧レベルを含むパルスパターンを有するテストモード用電圧と基準電圧とを比較して、トリガー信号及びデータ信号を含むパルス信号をそれぞれ出力する複数の比較器6a〜6cと、トリガー信号に基づいてデータ信号をシリアル/パラレル変換してテスト信号を生成し、テスト信号を被テスト回路9に供給するテスト信号生成回路5とによってテスト回路を構成する。

(もっと読む)

電源装置および試験装置

【課題】簡便な構成により電源電圧を一定に保つことが可能な試験装置を提供する。

【解決手段】半導体デバイスに電源電圧を供給する電源装置が提供される。メイン電源10は、半導体デバイスの電源端子P1に電力を供給する。電源補償回路12のソーススイッチ12bは、電源端子P1と接地端子の間に設けられる。電源補償回路12は、ソーススイッチ12bをノーマリオンとして電流IDCを発生させ、スイッチングによってソーススイッチ12bをオフしたときの電流の変化量を、ソース補償電流ISRCとして半導体デバイスの電源端子P1に注入する。

(もっと読む)

1 - 20 / 573

[ Back to top ]