Fターム[2G132AJ01]の内容

Fターム[2G132AJ01]の下位に属するFターム

能動素子を有するもの (7)

スイッチ、表示器付 (4)

機械的な構造 (8)

Fターム[2G132AJ01]に分類される特許

1 - 20 / 43

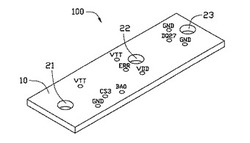

DDR信号をテストするための補助冶具

【課題】マザーボードのDDR信号を容易にテストすることができるテスト補助冶具を提供すること。

【解決手段】本発明に係るDDR信号をテストするための補助冶具は、DDRメモリ用コネクタを有するマザーボードに着脱可能に固定される板体を備え、前記板体には、前記マザーボードのDDRメモリ用コネクタのピンに各々対応する複数のテスト孔が設けられ、前記板体における各々のテスト孔の近傍には、キャラクターが設けられ、前記キャラクターは、各々のテスト孔と組み合わせられるDDRメモリ用コネクタのピンの名称或いは機能をそれぞれ示す。

(もっと読む)

テストカード

【課題】本発明は、テストカードを提供する。

【解決手段】本発明のテストカードは、電源インターフェースと、コントローラーと、テストインターフェースと、複数のテストポイントとを備え、テストインターフェースは、電源ピンと、スタートピンと、複数のデータ信号ピンとを備え、電源インターフェースは、コントローラー、電源ピン及び外部電源に接続されて、外部電源からの作動電圧をコントローラー及び電源ピンに提供し、コントローラーは、スタートピンにスタート信号を送信し、複数のデータ信号ピンは、複数のテストポイントにそれぞれに接続され、マザーボードのコネクターをテストインターフェースに接続すると、電源ピン、スタートピン及びデータ信号ピンは、マザーボードのコネクターの対応するピンにそれぞれに接続され、マザーボードがスタート信号を受信すると、システムを運行して、テストポイントにマザーボードのデータ信号を出力する。

(もっと読む)

IC及びマザーボードの間の入出力信号の計測方法

【課題】アダプタ基板を用いたIC及びマザーボードの間の入出力信号の計測方法であって、パッドの近傍に部品が存在している場合においても、アダプタ基板を実装することができるための手段を得る。

【解決手段】マザーボードとアダプタ基板とのとの間に測定すべきICと同じ大きさの中継基板を配置させる。また、中継基板を多層構造とし、中継基板の内層を電源層及びグラウンド層の組とする。

(もっと読む)

集積回路装置のテストシステム、及び集積回路装置のテスト方法

【課題】効率よくバーンインテストを行うことができる、集積回路装置のテストシステム、及び集積回路装置のテスト方法を提供する。

【解決手段】基板と、前記基板上に設けられ、テスト対象装置を搭載するソケット部と、前記基板に設けられ、高周波磁界内に配置されたときに電磁誘導によって電力を生成する、電力発生部と、前記基板に設けられ、前記電力発生部により生成した電力を利用して、前記テスト対象装置にテスト用電圧を供給する、制御回路とを具備する。前記ソケット部は、高周波磁界内に配置されたときに発熱する発熱部材を備えている。前記発熱部材は、前記発熱部材から前記テスト対象装置に熱が供給されるように、前記テスト対象装置と接触する接触面を備えている。

(もっと読む)

診断装置及び診断方法

【課題】交換モジュールの検査を低コストで実現すること。

【解決手段】本発明に係る診断装置1は、検査用プログラマブル論理回路21と、複数の検査モードの情報を格納する検査用記憶手段22と、を有する検査用ボード2と、制御用プログラマブル論理回路11と、複数の検査モードの情報を格納する制御用記憶手段14と、検査用ボード2が接続された場合に、検査用記憶手段22及び制御用記憶手段14に格納された複数の検査モードの情報に基づいて、検査用プログラマブル論理回路21及び制御用プログラマブル論理回路11を検査用の論理に置き換え、複数の検査モードを順次実行することで診断を行う診断プロセッサ15と、を有する交換モジュールと1、を備えるものである。

(もっと読む)

半導体集積回路の試験装置及び半導体集積回路の試験方法

【課題】アナログ・デジタル混載試験装置により試験される被試験半導体装置の進化はきわめて短期間のうちに行われるようになってきている。そのため、設備投資や開発・改造費用の回収をした程度のタイミングで試験モジュールの改定が必要となる場合もあり、コスト的に優位となるアナログ処理とデジタル処理とを混載した半導体集積回路の試験装置を低価格で開発・改造するための技術が求められている。

【解決手段】アナログ回路の試験をインターフェースボード1で行い、デジタル試験装置3からインターフェースボード1に試験シーケンスを伝えるようにした。アナログ回路の試験を低TATで開発・改造し得るインターフェースボード1で行うため、設備投資や開発・改造費用の回収が容易になった。また、DUTの直近で試験できることから、配線による位相回転や雑音の流入が抑えられ、アナログ回路の試験を高い精度をもって行えるようになった。

(もっと読む)

差動出力回路の試験方法および試験回路

【課題】試験時間の短縮および試験コストの低減を図る。

【解決手段】差動出力回路の出力端子間に同値の抵抗R1,R2を直列接続し、その共通接続ノードCを同値の抵抗R3を介して終端電圧端子31に接続する。同相電圧の試験では、電圧源トランジスタMP1と電流源I1を動作させトランジスタMN1〜MN4を制御して、ノードP,Mの間の論理を“H”又は“L”の状態に制御し、ノードCに発生する電圧が上限同相規格電圧と下限同相規格電圧の範囲内に入るか否かを判定する。差動電圧の試験では、前記同相電圧の試験状態から電圧源トランジスタMP1を不動作にした状態に制御し、終端電圧端子31に既知の電圧を印加し、ノードCに発生する電圧が定められた上限値と下限値の電圧範囲内に入るか否かの判定を行う。

(もっと読む)

ICテスタ

【課題】テストヘッドの汎用性を維持しつつ、アナログ試験モジュールをテストヘッドに設けることができるICテスタを実現することを目的にする。

【解決手段】本発明は、アナログ試験モジュールをテストヘッドの内部に搭載し、被試験対象を試験するICテスタであって、アナログ試験モジュールは、メイン基板と、このメイン基板の前後にコネクタにより接続し、前半領域の両面に設けられる第1のアナログ回路、後半領域の両面に設けられ、第1のアナログ回路と電気的に接続する第1のデジタル回路を有し、アナログ試験を行う第1のサブ基板と、メイン基板の第1のサブ基板と反対側に、前後にコネクタにより接続し、前半領域の両面に第2のアナログ回路、後半領域の両面に設けられ、第2のアナログ回路と電気的に接続する第2のデジタル回路を有し、アナログ試験を行う第2のサブ基板とを備えたことを特徴とするものである。

(もっと読む)

半導体デバイスのテスト補助回路およびテスト方法

【課題】チャンネル数の少ないテスターを使用する時や、DUTの信号ピン数が多い時であっても、容易に複数のDUTを同時にテストすることができる半導体デバイスのテスト補助回路を提供する。

【解決手段】テスト補助回路は、DUTの信号ピンの本数分のテスト単位回路と、複数のDUTの不良を検出する不良検出回路を備える。各々のテスト単位回路は、DUTの個数分の単位回路を備え、各々の単位回路は、入力値/出力期待値の入力端子とDUTの対応する信号ピンに接続される双方向端子との間に接続されたスイッチ、DUTの信号ピンの出力信号の電圧と判定基準電圧とを比較する回路、電圧比較結果と出力期待値とを比較する回路、期待値比較結果に応じたテスト結果を出力する回路を備える。不良検出回路は、各々の信号線をプルアップないしはプルダウンする、DUTの個数分の抵抗素子を備え、各々の信号線には、対応するDUTのテスト結果がワイヤード接続されている。

(もっと読む)

電流測定方法

【課題】電気機器の設計段階で行う回路パターンの電流測定の準備に掛かる手間と時間を削減する電流測定方法を提供することである。

【解決手段】電源回路基板30とAV回路基板31と間の電力供給をフレキシブルフラットケーブル36を用いて行うために両回路基板30、31にそれぞれ設けられたケーブル接続部30a、31aと、1本ずつ分かれた複数の平行導体42aを有する治具42のコネクタ42b、42cとを、それぞれフレキシブルフラットケーブル36、43を介して接続し、平行導体42aを1本ずつ引き上げた状態で電流測定用のプローブを用いて電流値を測定する電流測定方法であって、ケーブル接続部30a、31aのピン数よりも治具42のコネクタ42b、42cのピン数の方が多い構成とする。

(もっと読む)

試験装置、調整用ボードおよび調整方法

【課題】信号入出力のタイミングを調整する処理を効率化する。

【解決手段】試験装置は、被試験デバイスへ信号を出力する複数の信号出力部と、被試験デバイスの端子から出力される信号を入力する複数の信号入力部と、複数の信号出力部の出力タイミングを調整する場合に複数の信号出力部および基準とする一の信号入力部に接続され、各信号出力部から順次選択された信号出力部が出力する出力信号を基準とする信号入力部へ伝播させる第1接続部とを備え、各信号出力部の出力信号を、基準とする信号入力部が同一タイミングで受信するように各信号出力部の出力タイミングを調整し、複数の信号入力部の入力タイミングを調整する場合において、各信号入力部を、調整済の信号出力部の何れかに順次接続する第2接続部を備え、調整済の各信号出力部が出力する出力信号を、接続先の各信号入力部が同一タイミングで受信するように各信号入力部の入力タイミングを調整する。

(もっと読む)

コネクタセットおよび試験装置

【課題】高密度実装された同軸コネクタ接続における、隣接経路への信号リークの回避。

【解決手段】複数の第1同軸コネクタが互いに並行に配列された第1コネクタブロックと、それぞれが対応する第1同軸コネクタに電気的に接続される複数の第2同軸コネクタが並行に配列された第2コネクタブロックとを備え、複数の第1同軸コネクタおよび複数の第2同軸コネクタが嵌合された場合において、少なくとも1つの第1同軸コネクタおよび第2同軸コネクタの接続部分におけるシールドの境界部分と、他の少なくとも1つの第1同軸コネクタおよび第2同軸コネクタの接続部分におけるシールドの境界部分とが、信号伝播方向においてずれた位置に設けられるコネクタセットを提供する。

(もっと読む)

検出装置

【課題】欠陥チップを取り除くことなく動作可能な、プリント回路板のチップを検出する検出装置を提供する。

【解決手段】プリント回路板に電気的に接続されたチップを検出する検出装置20であって、複数のピンを有する書き換え可能チップ21と、前記書き換え可能チップに電気的に接続され、両側に設置された複数のピン25と、前記書き換え可能チップのピンに電気的に接続された代替プリント回路板23と、前記チップと前記書き換え可能チップに接続され、前記チップと前記書き換え可能チップを制御するスイッチ29と、を備える検出装置。この検出装置によれば、検出装置に電気的接続された欠陥チップが無効にされ、書き換え可能チップが欠陥チップの代用をすることから、欠陥チップを取り除くことなく動作することができる。

(もっと読む)

パフォーマンスボードおよびカバー部材

【課題】パフォーマンスボード200裏面の小型で廉価な断熱構造を提供する。

【解決手段】半導体試験装置100のテストヘッド130に装着されて、被試験デバイス160を実装されるパフォーマンスボード200であって、基板500と、基板500の表面に装着されて被試験デバイス160を実装されるソケット510と、基板500の裏面に装着されてテストヘッド130側に結合されるコンタクトパッド530と、基板500においてソケット510が装着された領域の裏面に装着され、基板500の裏面における当該領域を包囲して外部から熱的に遮断するカバー部材400とを備える。

(もっと読む)

試験装置

【課題】ベースバンド信号がキャリア信号により変調された出力信号を出力する被試験デバイスを、効率よく試験する。

【解決手段】出力信号を中間周波数に周波数変換したIF信号を出力する周波数変換部と、IF信号をサンプリングしてデジタル化したデジタル信号を出力するアナログデジタル変換部と、デジタル信号と当該デジタル信号の期待値信号とを比較する比較部と、周波数変換部、アナログデジタル変換部および比較部のうちの少なくとも一つの動作設定値を、複数の試験のそれぞれに対応させて記憶する設定値メモリと、制御部からの試験開始の指示を受けたことに応じて、複数の試験のそれぞれについて順次に動作設定値を設定値メモリから読み出し、読み出した動作設定値を周波数変換部、アナログデジタル変換部および比較部に設定し、複数の試験を順次に実行するシーケンサとを有する試験モジュールを備える試験装置を提供する。

(もっと読む)

半導体集積回路の検査装置

【課題】コネクタの接続を容易に行いながら、ロードボード側コネクタに位置ずれが発生しても、ロードボードと検査装置の電気的な接続を維持することを目的とする。

【解決手段】検査装置側のコネクタ3に、検査装置側のコネクタ3との間に隙間を設けた規制治具8と、ロードボード側コネクタの位置にあわせ、検査装置側コネクタ3の位置を誘導するガイド斜面31を備えることにより、隙間の分だけコネクタ3が稼動可能な状態で検査装置1に検査装置側のコネクタ3を固定できるため、コネクタ3の接続を容易に行いながら、ロードボード側コネクタに位置ずれが発生しても、ロードボードと検査装置1の電気的な接続を維持することができる。

(もっと読む)

アダプタ及びそれを備えた電子部品試験装置

【課題】既存のテストヘッドを残さずに既存のパフォーマンスボードを有効に活用するアダプタを提供する。

【解決手段】新式のパフォーマンスボードにICデバイスを電気的に接触させてICデバイスの試験を行うために用いられるテストヘッド20Aに、新式のパフォーマンスボードに代えて旧式のパフォーマンスボード30’を適合させるためのアダプタは、テストヘッド20Aに電気的に接続可能な第1の接続ボード110と、旧式のパフォーマンスボード30’に電気的に接続可能な第2の接続ボード120と、第1の接続ボード110と第2の接続ボード120とを電気的に接続する第3の接続ボード130と、を備えている。

(もっと読む)

自動識別検査システムとこれの制御方法

【課題】電子部品の電気的特性検査にて、人手によらず品種切り替え、検査が行える自動識別検査システムとこれの検査方法を提供する。

【解決手段】 複数の被測定物の検査を行う自動識別検査システムは、複数の被測定物を搭載し、該当する識別情報及び前記被測定物の検査履歴情報を有する検査対象基板、及び被測定物の品種並びに検査規格を蓄積する基板情報蓄積手段と、検査対象基板に書き込まれた識別情報及び検査履歴情報を読み出す読み出し手段と、読み出された識別情報に基づいて、該当する基板情報を基板情報蓄積手段から検索する基板情報検索手段と、検索された品種に対応する被測定物を検査履歴情報により選定し、選定された被測定物の検査を行う検査手段と、該結果を検査規格により判定する判定手段と、判定結果を検査履歴情報として識別情報に対応させて検査対象基板に格納する格納手段とからなる主制御装置とから構成される。

(もっと読む)

半導体装置用DUTボードおよびテスタ

【課題】DUTボードの管理負担を軽減する半導体試験装置を提供する。

【解決手段】半導体装置と接続することが可能であって、前記半導体装置の良否判定を行うためのデータをテスタに送信可能な端子を備えたDUTボードにおいて、

前記DUTボードは、前記テスタとDUTボードとの適合性判断の基礎となる第1の情報を格納するボード記憶装置を備えていることを特徴とする半導体装置用DUTボード。

(もっと読む)

ICソケット及び半導体集積回路試験装置

【課題】装置の大型化やテストプログラムの複雑化を来たすことなく並列試験個数を従来よりも増大させる。

【解決手段】被測定デバイスをテストボード上に着脱自在に実装するICソケットにおいて、試験装置本体からの制御指令に基づいて試験用信号を発生して被測定デバイスに出力する試験用信号発生部を備える。

(もっと読む)

1 - 20 / 43

[ Back to top ]