Fターム[2G132AK15]の内容

電子回路の試験 (32,879) | 試験のための被試験体の構成、回路構成 (3,847) | 試験のための回路構成 (3,586) | 試験モードへの切替回路 (419)

Fターム[2G132AK15]の下位に属するFターム

通常電圧以外の電圧で切り替えるもの (22)

シフトレジスタを用いるもの (30)

カウンタを用いるもの (28)

AD変換回路を用いるもの (16)

デコーダを用いるもの (59)

遅延回路を用いるもの (42)

Fターム[2G132AK15]に分類される特許

1 - 20 / 222

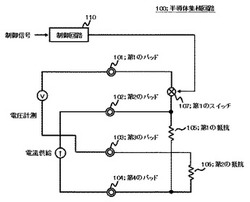

半導体集積回路

【課題】半導体集積回路に含まれる終端抵抗の抵抗値を4端子法によって測定をするためには、必要となる端子が増加し、半導体集積回路のチップサイズが増加するという問題がある。そのため、半導体集積回路のチップサイズ増加を抑制しつつ、終端抵抗の抵抗値を高精度で測定可能な半導体集積回路が、望まれる。

【解決手段】半導体集積回路は、第1乃至第4のパッドと、第2のパッドと第4のパッドの間に接続される第1の抵抗と、第3のパッドと第4のパッドの間に接続される第2の抵抗と、第1のパッドと第2のパッドの間に接続される第1のスイッチと、第1のパッド及び第3のパッドを4端子法における電圧測定端子として、第2のパッド及び第4のパッドを4端子法における電流供給端子として、それぞれ使用し第1の抵抗の抵抗値を測定するテストモードへの遷移指示を含む制御信号に基づき、第1のスイッチをオンする制御回路と、を備える。

(もっと読む)

半導体装置

【課題】誤ってテストモードにエントリされたとしても、正常に動作させる。

【解決手段】半導体装置は、内部回路をテストするテスト回路2に対してテストを開始させるテストモードエントリ信号が入力されたことに応じて、内部のラッチ10をセットすることにより、テスト回路2に対し、テスト回路2の駆動を許可するテストイネーブル信号をラッチ10から出力するテスト信号発生回路1を備える。テスト信号発生回路1が、ラッチ10がテストイネーブル信号を出力している場合、テストイネーブル信号を遅延させて、ラッチ10をリセットするリセット信号を生成するリセット信号生成回路30と、ラッチ10がテストイネーブル信号を出力している場合に、外部から供給されるトグル信号に基づいて、リセット信号生成回路30によるリセット信号を生成する動作を初期化する遅延初期化信号を出力する遅延初期化回路40と、を有している。

(もっと読む)

半導体集積回路及びその制御方法

【課題】アプリケーション実行効率をよりよくすることができる半導体集積回路及びその制御方法を提供すること

【解決手段】本発明にかかる半導体集積回路は、スキャンチェーンを有するプロセッサと、プロセッサにアプリケーションを実行させるプロセッサ制御部と、プロセッサのスキャンテストを制御するスキャンテスト制御部と、を有する。そして、スキャンテスト制御部がスキャンテストを実行している際に、プロセッサ制御部からのスキャンテスト中断要求があった場合、スキャンテストを中断し、アプリケーションの実行後に、スキャンテストを再開させるものである。

(もっと読む)

半導体集積回路

【課題】IDDQテスト等にかかる時間を短縮できる半導体集積回路を提供する。

【解決手段】CMOS論理回路10を集積した半導体集積回路1において、CMOS論理回路10の複数の出力段CMOSデバイス12と、外部へ信号を出力する複数の出力端子32との間に、出力論理値制御回路20を設ける。出力論理値制御回路20は、複数の出力段CMOSデバイス12に各々対応して複数設けられた2入力1出力の論理演算子21で構成され、一方の入力端に出力段CMOSデバイス12が出力する論理値を、他方の入力端に制御信号22を入力する。この論理演算子21は、制御信号22をHigh又はLowのどちらかに固定すれば出力端の論理値をHigh又はLowのどちらかに固定できる演算子である。

(もっと読む)

半導体装置およびその検査方法

【課題】本発明の実施形態は、高周波スイッチ回路の高周波特性の良否を簡便に判定することができる半導体装置およびその検査方法を提供する。

【解決手段】実施形態に係る半導体装置は、複数の高周波端子と、共通高周波端子と、の間の信号経路を、前記高周波端子と前記共通高周波端子との間に直列に設けられた複数のFETにより切り替える高周波スイッチ回路を有する半導体装置であって、前記共通高周波端子に接続された複数のFETを含む半導体スイッチと、前記半導体スイッチを介して前記共通高周波端子に接続された発振回路と、前記発振回路の出力を入力とする検波回路と、前記検波回路の出力端子と、を備える。

(もっと読む)

テストモード設定回路

【課題】端子数の少ないテストモード設定回路を提供する。

【解決手段】半導体装置のテストモードを制御するテスト端子に、低閾値電圧のディテクタと高閾値電圧のディテクタを設け、低閾値電圧のディテクタによって論理回路のリセットを解除し、高閾値電圧のディテクタでテストモードを切替え制御するような構成にした。従って、テスト端子とリセット端子とテストモード制御端子が共通になり、端子の数を大幅に削減することが可能である。

(もっと読む)

半導体装置

【課題】テスト信号を誤動作なく発生するテスト回路を備えた半導体装置を提供する。

【解決手段】動作指定コマンドがテスト動作モードの設定を示すときに、コマンド信号CMD1及びコマンド信号CMD2に応じて、第1のテスト信号(テスト信号DFT1〜DFTn)のうち所定の信号を活性化するコマンドデコーダ106と、動作指定コマンドがテスト動作モードの設定を示すときに第1のテスト信号を受け取り、第2のテスト信号(制御用テスト信号DFTF1〜DFTFn)として並列に出力し、テスト動作モードの設定以外の動作を指定するときに、スキャンチェーン接続され、第1のテスト信号を第3のテスト信号としてスキャン出力端子TSOUTへ直列に出力するレジスタ部107と、テスト動作モードの設定を示すときに、第2のテスト信号に応じてメモリセルアレイの動作を制御する読み出し及び書き込み制御部104と、を備える。

(もっと読む)

半導体集積回路及びその制御方法

【課題】テストモードにおいて、複数の内部回路のうち所望の内部回路のみを動作させて消費電流測定を行うことが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路は、電源スイッチ7,8と、電源スイッチ7を介して電源が供給される内部回路4と、電源スイッチ8を介して電源が供給される内部回路5と、電源スイッチ7,8のオンオフを制御する電源制御信号を出力する制御回路2と、を備える。制御回路2は、電源スイッチ7,8のオンオフを制御するための制御信号n2,n3を生成する通常動作モード用電源制御回路21と、電源スイッチ7,8のオンオフを制御するための制御信号t2,t3を生成するテストモード用電源制御回路22と、制御信号n2,n3及び制御信号t2,t3のいずれかを、モードに応じて選択的に電源制御信号p2,p3として出力するセレクタ25,26と、を有する。

(もっと読む)

半導体集積回路装置およびテストモード設定方法

【課題】簡易な回路で、よりセキュリティ性を向上させる。

【解決手段】半導体集積回路装置(100)は、複数の機能ブロック(125−127)と、取り込み部(131)と、検出部(132)と、判定部(150)とを具備し、動作パターンが所定の規則に従って変化したときにテストモードに移行する。複数の機能ブロック(125−127)は、制御装置(200)からの指示に応答して動作する。取り込み部(131)は、複数の機能ブロック(125−127)のそれぞれの動作状態を示す信号を取り込む。検出部(132)は、複数の機能ブロック(125−127)のうちの少なくとも1つの機能ブロックの動作状態の変化を検出する。判定部(150)は、取り込まれた動作状態を示す信号によって示される動作パターンが所定の規則に従って変化するか否かを判定する。

(もっと読む)

半導体集積回路の試験システムおよびその試験方法

【課題】半導体集積回路の不良選別を効果的に行う。

【解決手段】互いに非同期のクロックで動作する複数の回路ブロックを有し、複数の回路ブロックの一の回路ブロックによってセルフテストを実行する半導体集積回路の試験システムであって、複数の回路ブロックに対応するクロック信号を生成し半導体集積回路に供給するクロック発生装置と、半導体集積回路からの要求に応じてセルフテストの実行を代行するプロセッサを有する。これにより、各モジュールが非同期のクロックで動作する半導体集積回路の動作テストを行うことができる。

(もっと読む)

半導体装置およびその試験方法

【課題】チップ間の接続を検査可能な半導体装置を提供する。

【解決手段】第1電源ラインLVDD1と第2電源ラインLVDD2には、独立に電源電圧を供給可能となっている。バッファBUF1は、第1パッドP1ごとに設けられ、それぞれの出力端子が対応する第1パッドP1に接続され、信号を出力するイネーブル状態と、出力がハイインピーダンスとなるディスイネーブル状態が切りかえ可能となっている。試験時には、検査対象のワイヤと接続される第1パッドP1および第2パッドP2がハイインピーダンスとされ、第1電源ラインLVDD1に電源電圧VDD1を、第2電源ラインLVDD2に接地電圧が供給される。テスト用パッドPTESTに対して試験電流ITESTが供給され、テスト用パッドPTESTの電圧が測定される。

(もっと読む)

半導体メモリ、半導体装置及び半導体メモリの制御方法

【課題】試験時間の短縮を図る。

【解決手段】ソース線電圧制御回路31は、テストモード制御回路から供給されるテストモード信号TMに応答して、テストモードにおけるソース線SL0を、通常モードのリード動作における電位(第1の電圧)と異なる電位(第2の電圧)に制御する。ソース線SL0の電位が第1の電圧に制御されたとき、メモリセルには、消去状態又は書込状態に応じたセル電流が流れる。ソース線SL0の電位が第2の電圧に制御されたとき、メモリセルには、参照電流より少ないセル電流が流れる。センスアンプ27bは、書込状態のメモリセル、つまり「データ0」に応じた「0」のデータDoutを出力する。

(もっと読む)

半導体集積装置

【課題】高速インターフェースのAC特性を測定する場合において、簡単な回路構成で信号種による差動入力回路での遅延時間差の発生をなくして、安価で低速なLSI検査装置で測定を行うことができる半導体集積装置を提供する。

【解決手段】第1、第2の差動入力回路13、20を含むデータ入出力を行う高速インターフェース回路を備えた半導体集積装置において、第1、第2の差動入力回路13、20の一方の入力側にデータ入力又は基準電圧のいずれか一方を選択入力するための選択器22を有し、AC特性を測定するテストモード時は、選択器22による入力選択により第1、第2の差動入力回路13、20の一方の入力側へ基準電圧を入力し、第1、第2の差動入力回路の他方の入力側へ高速インターフェース回路からの出力データを入力する。

(もっと読む)

半導体装置

【課題】データの入出力用端子のうち、一部の端子にテスト用ピンを接続することで、全ての入出力用回路の検査を可能にした半導体装置を提供する。

【解決手段】複数の外部端子と、複数のメモリセルを含むメモリセルアレイと、複数の外部端子のそれぞれに対応して、外部端子とメモリセルアレイとの間に並列に設けられた入力回路および出力回路と、検査対象の外部端子に対応して設けられた入力回路に所定のメモリセルから出力回路および外部端子を介してデータが入力されると、データに基づく信号を、検査対象の外部端子とは異なる所定の外部端子に出力する検出部とを有する。

(もっと読む)

システムLSIにおける電気信号特性の観測及び解析装置

【課題】システムLSI内部の信号を観測するために、小数個のテストコネクションポイントを設け、そこに選択的に切り替えられた観測対象信号を出力することは出来るが、これでは内部状態を物理的に外部に引き出しただけであり、電気信号単体での波形立ち上がり時間/ジッタ値/アイ・ダイアグラムの開口、また2つ以上の電気信号での位相ズレ、そして観測信号そのものの信号品質について対応が不十分である。

【解決手段】本発明では、内蔵された信号を外部に引き出す場合の特殊な構造を設けることによって、システムLSIにおける電気信号特性の観測及び解析を可能とする。パッケージ上に内蔵された電気信号をデジタル的かつアナログ的に観測することでシステムLSIの解析をするこが可能となる。さらに観測用端子についても最小限に抑えることができ、システムの省スペース化及び、コストダウンに対応することが可能となる。

(もっと読む)

半導体装置

【課題】積層型半導体装置において積層される半導体チップ間の接続テストにあたり、回路規模の拡大の抑制およびテスト時間の短縮を図る。

【解決手段】チップ200において、トランジスタTR11乃至14の組とTR21乃至23の組を貫通電極201a乃至201hに対して互いに1つずつずらして配置して接続する。制御電圧VDDと基準電圧VSSを最下層から各層のチップに対して印加した状態で、トランジスタTR11乃至14は、下層にチップが積層され、上層にチップが積層されないときにオンとなるように駆動する。トランジスタTR21乃至23は、下層および上層にチップが積層されているときにオンとなるように駆動する。これにより、最上層とその下の層のチップ間のマイクロバンプ210と220の接合部のコンタクトチェーンを形成する。接続テストはコンタクトチェーンの抵抗値を測定する。

(もっと読む)

テスト回路およびテスト回路の制御方法

【課題】テスト専用端子の増加を防ぎ、テストの長時間化を防止する。

【解決手段】テストアクセスポートに入力されるテスト信号に応じて、回路ブロックの試験を行うテスト回路であって、第1のTAP制御部及びその制御下にある第2のTAP制御部と、第1のTAP制御部のテスト動作の無効と、記憶情報の書き換えを不可に制御する第1の情報を記憶する第1のレジスタと、第1の情報に応じて記憶情報の書き換えを不可に制御され、第2のTAP制御部のテスト動作の有効・無効の制御する第2の情報を記憶する第2のレジスタと、外部から入力されるTDI信号に応じて前記第1、2のレジスタが書き換え不可状態を解除する制御回路と、を有するテスト回路。

(もっと読む)

半導体装置

【課題】電源投入時において誤ってテストモードが設定されたテスト回路をリセットするテスト信号発生回路を備えた半導体装置を提供する。

【解決手段】テスト信号発生回路100は、テストイネーブル信号TESTEをLレベルからHレベルへと遷移させてテスト回路を活性化し、テストイネーブル信号TESTEをHレベルからLレベルへと遷移させてテスト回路を非活性化する。テストモードエントリ信号ENTESTBがHレベルからLレベルへ遷移すると、テストイネーブル信号TESTEをLレベルからHレベルへと遷移させ、テストイネーブル信号TESTEがHレベルへと遷移してから予め設定された所定期間経過後に、テストモードエントリ信号ENTESTBがHレベルに遷移しているとき、テストイネーブル信号TESTEをHレベルからLレベルへと遷移させる。

(もっと読む)

回路試験装置

【課題】簡易な構成で論理回路を用いたシステムを停止させることなく論理回路の試験を行なう回路試験装置を得ること。

【解決手段】システムの動作の一部を実行する試験対象部と同じ機能を有した論理回路をFPGAを用いて再構成する試験対象機能代替部11を備え、試験対象入力選択部15は、試験対象部10の試験が行なわれる際には試験データ準備部16からの試験情報を選択して試験対象部10に出力し、且つ試験対象部がシステムの動作の一部を実行する際にはシステム前段P1からの入力情報を選択して試験対象部10に出力し、有効回路選択部14は、試験対象部の試験が行なわれる際には再構成後の試験対象機能代替部11による処理結果を選択してシステム後段Q1側へ出力し、且つ試験対象部10がシステムの動作の一部を実行する際には試験対象部10による処理結果を選択してシステム後段Q1側へ出力する。

(もっと読む)

テストモード付きフラッシュメモリ及びその接続試験方法

【課題】フラッシュメモリとその周辺回路との接続性試験を上位アドレス線を含めて適確に行なう。

【解決手段】コマンドデコーダ603は、外部ピンからの入力信号が特定のアドレスに対する特定の値の書き込みであることを検出する。ステートデコーダ602は、ステートマシン307の状態が所定のモードであるCFIクエリモードであるかを判定する。判定回路604は、ステートデコーダ602がCFIクエリモード配下でコマンドデコーダ603の検出出力とに基づいてテストモードになったことを判定する。データ保持回路605は、判定回路604の判定出力をセットし、テストモードになったことを示すテストモード表示信号403を保持する。テストモードにおいては、例えばアドレス線の上位側をデータ線に出力する。

(もっと読む)

1 - 20 / 222

[ Back to top ]