Fターム[2G132AL01]の内容

Fターム[2G132AL01]の下位に属するFターム

電子的手段によるもの (4)

Fターム[2G132AL01]に分類される特許

1 - 18 / 18

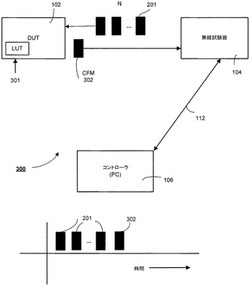

電子デバイスにおけるパケットエラー率の決定論的試験のためのシステム及び方法

【課題】電子機器におけるパケットエラー率を試験する方法及びシステムを提供する。

【解決手段】試験器104からDUT102に一連のデータパケット201を送信し、事前定義される受信エラーフリーデータパケットの数を設定し、一連のデータパケット201からDUT102でエラーなしに受信されたデータパケット201の数が事前定義される受信エラーフリーデータパケットの数と等しいか評価し、一連のデータパケット201からDUT102でエラーなしに受信されたデータパケット201の数が事前定義される受信エラーフリーデータパケットの数と等しくないとき正常動作のDUT102でゼロの受信パケットエラーを生成することが既知の電力レベルで試験器104からDUT102に追加データパケットを送信して、電子機器におけるパケットエラー率を試験する。

(もっと読む)

コンデンサの実装状態判別装置およびコンデンサの実装状態判別方法

【課題】コンデンサの実装・非実装の判別と共に、非実装のときには非実装のコンデンサが実装されるべき位置を判別する。

【解決手段】導体パターン11,12上の測定点P1,P2間のインピーダンスの周波数特性を測定する測定部2と、コンデンサ21〜23が正常に実装された状態での周波数特性に現れる各共振周波数f1〜f3毎に、共振周波数f1〜f3を含む判定範囲fr1〜fr3と共振周波数f1〜f3に対応するコンデンサ21,22,23とを対応付ける基準データD2が記憶された記憶部3と、コンデンサ21〜23の実装状態が未知の導体パターン11,12についての周波数特性を測定部2に測定させ、この周波数特性に現れている共振周波数と基準データD2の各判定範囲fr1〜fr3とを比較して、共振周波数を含まない判定範囲fr1〜fr3に対応付けられたコンデンサが非実装状態であると判別する処理部4とを備えている。

(もっと読む)

試験装置によってセキュアドチップへのアクセスを認証する方法

試験装置TDによってセキュアドチップSCへのアクセスを認証する方法。試験装置は少なくとも1つの共通鍵CK及び1つの試験鍵TKを格納し、セキュアドチップSCは同じ共通鍵CK及び試験鍵TKへの暗号関数の適用から生じる基準ダイジェストF(TK)を格納する。本方法は、試験装置TDによって、セキュアドチップSCにより生成されたチャレンジRを受信するステップと、試験装置TDによって、双方向数値演算(op)を適用することにより、受信されたチャレンジRを試験鍵TKと組み合わせ、共通鍵CKでその結果(TK op R)を暗号化し、暗号CK(TK op R)を得るステップと、暗号CK(TK op R)をセキュアドチップSCに送信するステップと、セキュアドチップSCによって、共通鍵CKで暗号CK(TK op R)を解読し、チャレンジRで、試験装置TDによって以前に用いられた数値演算(op)の逆演算(op−1)を適用することによって、試験鍵TKを表すイメージ鍵TK′を得るステップと、暗号一方向性関数でイメージ鍵TK′の予想されるダイジェストF(TK′)を算出するステップと、予想されたダイジェストF(TK′)を基準ダイジェストF(TK)と比較することによって有効性を確認するステップと、イメージ鍵TK′のダイジェストF(TK′)と基準ダイジェストF(TK)の比較の結果がポジティブである場合には、試験装置TDによって、試験モードでセキュアドチップSCにアクセスするステップと、を含む。 (もっと読む)

回路ユニットおよび電子機器

【課題】検査用コネクタの有効活用を図ることで、不具合を生じさせることなく回路基板に実装される電子部品を削減し、更なる小型化を達成することが可能な回路ユニットおよび電子機器を提供することを目的とする。

【解決手段】本発明にかかる回路ユニットの構成は、回路基板140と、回路基板に接続されるフレキシブルケーブル120と、を備える回路ユニットであって、回路基板は、フレキシブルケーブルとの接続面に、当該回路ユニット製造時の信号入出力検査に用いられる検査用コネクタ152を有し、フレキシブルケーブルは、検査用コネクタに接続される接続部124を有することを特徴とする。

(もっと読む)

プローブ装置、処理装置及びウェハプローブテストの処理方法

【課題】効率的なウェハプローブテストが可能なプローブ装置及び処理装置の提供。

【解決手段】プローブ装置200は複数の測定ステージ220とプローブカードを識別するための第1の識別子を複数のプローブカードから読み取る情報読み取り部260と測定ステージを識別するための第2の識別子が記憶された第1の記憶手段と第1の記憶手段から第2の識別子を読み取る情報読み取り部260と読み取った第1第2の識別子が対応付けられて記憶される測定ステージID記憶部212と搬送アーム230で測定ステージへ搬送された半導体ウェハに第1の検査を行う手段と処理装置から測定ステージの不使用を示す情報と第1及びまたは第2の識別子が対応付けられたステージ情報を受信する情報送受信部270と受信したステージ情報に基づいて、測定ステージへ半導体ウェハを搬送する搬送アーム230と搬送された半導体ウェハに第2の検査を行う手段を具備する。

(もっと読む)

電子機器、外部メモリ装置、電子機器の検査方法及びプログラム

【課題】検査の結果得られる詳細な内容を確実且つ簡易に回収して後日活用する。

【解決手段】外部装置を接続するためのUSB−I/F32及びUSBコネクタ36と、USBコネクタ36に当該機器の機種に対応した特定の検査用プログラムを記憶した外部メモリ装置(40)が接続されたことを判断し、その判断時に外部メモリ装置(40)から検査用プログラムを読出し、読出した検査用プログラムを実行して検査結果データと当該機器個体の誤差を補正するキャリブレーションデータとを取得し、取得した検査結果データとキャリブレーションデータとを関連付けてデータファイル化し、USBコネクタ36を介して外部メモリ装置(40)に転送して記憶させるCPU28及びプログラムメモリ29とを備える。

(もっと読む)

電子デバイス及び解析方法

【課題】電子デバイスの劣化を精度よく解析し、かつ、電子デバイスを精度よく識別する。

【解決手段】電子デバイスの実動作時に動作する実動作回路と、電子デバイスの試験時に動作する第3のテスト用回路及び第2のテスト用回路と、電子デバイスの実動作時に、第2のテスト用回路に電源電圧が印加されない状態を維持して、実動作回路及び第3のテスト用回路に電源電圧を印加し、電子デバイスの識別時に、第2のテスト用回路に電源電圧を印加する電源部とを備える電子デバイスを提供する。第2および第3のテスト用回路は、電気的に並列に設けられた複数のテスト用素子と、電子デバイスの試験時において、それぞれのテスト用素子を順次オン状態に制御する選択部と、選択部が順次オン状態に制御したテスト用素子のそれぞれの端子電圧を、電子デバイスの識別情報として出力する識別情報出力部とを有してよい。

(もっと読む)

半導体装置検査方法

【課題】半導体装置の検査工程及び検査内容が簡略化された検査を行う半導体装置検査方法を提供すること。

【解決手段】半導体装置検査方法は、ウエハを検査する第1のウエハ検査工程と、ウエハをバーンインするバーンイン工程と、第1のウエハ検査工程で得られた検査データに基づいて、ウエハを再び検査するか否かを判定する第1の判定工程と、第1の判定工程での判定結果に応じて、バーンインされたウエハを再び検査する第2のウエハ検査工程と、ウエハから得られたチップをパッケージングしたパッケージ品を検査する第1のパッケージ品検査工程と、第1のパッケージ品検査工程で得られた検査データに基づいて、パッケージ品を再び検査するか否かを判定する第2の判定工程と、第2の判定工程での判定結果に応じて、パッケージ品を再び検査する第2のパッケージ品検査工程とを有する。

(もっと読む)

試験結果間の関係を推測する方法及び機械可読媒体

【課題】試験結果間の関係を推測する単純な方法を提供すること。

【解決手段】試験結果間の関係を推測する方法であって、1)多数の被試験デバイス(DUT)に関する試験を行う試験装置から順次試験データを受信し、2)DUT識別子を受信すると、前記DUT識別子のうちの1つによって識別されるDUTに対するデータ構造が存在するかどうかを判断し、3)前記データ構造が存在しないと判断した場合に、前記データ構造を作成し、i)前記DUT識別子のうちの1つに関連する任意の試験結果をii)前記データ構造に関連づけ、4)前記データ構造が存在すると判断した場合に、前記データ構造の子として子データ構造を作成し、i)前記DUT識別子のうちの1つに関連する任意の試験結果をii)前記子データ構造に関連づけ、前記子データ構造からは、それに関連する前記試験結果が再試験結果であることが推測される。

(もっと読む)

リセット検出装置

【課題】複数のチップが同一のパッケージに搭載されたマルチチップパッケージにおいて、任意のチップがリセットしたことを他のチップが簡易な構成で検出可能なリセット検出装置を提供すること。

【解決手段】第1リセット検出回路A2は、リセット検出線ARの電位が第2チップリセット電位を超えた場合に、第2チップがリセットされたことを検出する。また、第2リセット検出回路B2は、リセット検出線BRの電位が第1チップリセット電位を超えた場合に、第1チップがリセットされたことを検出する。これにより、任意のチップがリセットされたことを他のチップへ通知するリセット通知線を各チップ毎に設けたり、各チップがリセットされたか否かを監視する監視用のチップを新たに設けなくとも、任意のチップがリセットされたことを他のチップが検出でき、設計面およびコスト面からも好ましい。

(もっと読む)

回路デザイン電気的チェックシステム

【課題】 PCB、PWBの回路設計におけるデザインルールチェックに際し、作業の負担を軽減し、適切な電気的チェックを行う。

【解決手段】 回路デザインでのシンボルに電気情報を付加するにあたり、各入出力ピンに対して供給電源ピンを指定する手段と、上記供給電源ピンの指定に基づき、その供給電圧から各ピンのI/F電圧を特定する手段と、接続されるピンの上記I/F電圧を比較することにより接続違反の可否を判断する手段とを備え、使用する電源に合わせて各シンボルのピンの電気的な値を変更せずに、部品間の接続違反を検出する。

(もっと読む)

半導体集積回路

【課題】 テスト内容や、本体回路のロムコード、電気的特性等がわかってしまうことのないテスト回路の構成方法を提示する。本体回路の秘密保持が可能となり、信頼性も高まる。

【解決手段】 本体回路が構成された本体チップとは別に、テスト信号の入力およびテスト結果の出力を行う一つのテスト端子と、前記本体回路をリセットするとともにそのときに入力されたテスト信号の論理レベルに応答してテスト回路制御ユニットを初期化して周辺ユニットをテスト状態にセットするテスト状態セット手段とを有し、前記テスト端子を介して入力されたテストコマンドによりテストを行い、それにより得られたテスト結果のデータを前記テスト端子から出力する入出力手段とを備えた、テスト回路をテストチップとして1チップに集積する。本体チップと、テストチップとは近接した別のチップに配置しており、これらのチップ間は、スクライブ上で、アルミ等の金属配線でつながれている。

(もっと読む)

半導体装置の検査方法および半導体装置のテスター

【課題】 本発明は、一枚のシリコンウエハに複数種類の半導体デバイスを形成した場合において、テスターの観点から、各当該半導体デバイスを効率良く検査することができる半導体装置の検査方法等を提供する。

【解決手段】 第一の発明では、半導体デバイスに対応して配設されている識別マークを、認識するステップと、当該認識した識別マークに基づいて、予め設定された対応関係に従って、半導体デバイスの検査に必要なテストプログラムを、決定するステップと、当該決定したテストプログラムに基づいて、半導体デバイスを検査するステップとを、備えている。

(もっと読む)

プログラマブル回路及びプロセサエレメント

【課題】デバイスを基板実装後、通常動作モード時に個々の論理構成で必要に応じて実施する事を可能とする。

【解決手段】プログラマブルデバイスあるいは動的にデータ処理の論理構成を変更するデバイスにおいて、論理構成に従って変更されるプロセサエレメント間の接続に対応可能な経路遅延テストをデバイスにあらかじめ実装しておく。この経路遅延テストのうち論理構成の情報をもとに実効的に有効な経路に対して経路遅延テストを実施する。前記、プロセサエレメント間の接続に対応したターゲット周波数に対する経路遅延テストの結果をもとに、論理構成の入れ替え、あるいは、動作周波数の最適化を行う。

(もっと読む)

半導体メモリモジュール

【課題】搭載された複数のチップのうちの特定のチップのみを選択して動作命令を実行させることを可能とする。

【解決手段】半導体メモリモジュールに搭載された各半導体メモリチップ毎に異なるチップIDを設定し、このチップIDを、ヒューズ素子等により構成されたチップID格納部F1〜Fnにより各チップ毎に格納する。特定のチップのみを選択して動作命令を実行させる場合、テスタ装置から、チップIDを指定した動作命令を各チップに入力する。各チップでは、排他的論理和回路201〜20n、ゲート回路301〜30n、ラッチ回路401〜40n、AND回路50等により、指定されたチップIDと設定されたチップIDとの比較を行い、これらが一致した場合のみ、動作命令を受け付ける。

(もっと読む)

試験装置、診断プログラムおよび診断方法

【課題】各々の試験モジュールの診断に使用することのできる診断用パフォーマンスボードを定めた設定情報を、これまでより少ない作業負担で変更させる。

【解決手段】複数の試験モジュールを有する試験装置を提供する。試験装置は、診断対象の試験モジュールの種類毎に当該種類の診断対象試験モジュールの診断を制御させる対象診断プログラムを記憶し、それとは別個に、各々の対象診断プログラムによって診断対象試験モジュールを診断するためにテストヘッドに搭載されるべき診断用パフォーマンスボードの識別情報の組を、診断対象試験モジュールの種類毎に記憶する。診断用パフォーマンスボードがテストヘッドに搭載された場合に、その診断用パフォーマンスボードの識別情報を取得し、その識別情報が、指定された診断対象試験モジュールの種類に対応付けて記憶している識別情報と一致することを条件として、当該種類に対応する対象診断プログラムを実行する。

(もっと読む)

集積回路

【課題】集積回路の故障箇所における故障前後の特性データなどを記憶し、故障箇所の特定および軌跡が可能な集積回路を提供する。

【解決手段】集積回路100に不揮発性メモリ部110を備え、前記集積回路100の機能ブロック120の電流値の特性データ、または集積回路100の温度変化を示す電流値データ、または機能ブロック120内の振幅値の特性データ、または機能ブロック120内の回路動作を制御するデータなどを、それらが変化する毎に、前記不揮発性メモリ部110に書き換え可能にする。

(もっと読む)

半導体集積回路装置のI/Oセルチェック方式

【課題】 半導体集積回路装置の作成前、又は出荷する前にその論理機能や動作特性を検証する段階で、搭載されている個々のI/Oセルの種別を事前に確認可能とする半導体集積回路装置を提供する。

【解決手段】 複数のI/Oセルを搭載する半導体集積回路装置であって、各I/Oセル内に設けられ、そのI/Oセルを識別するためのセル識別情報を保持するセル識別情報保持部と、半導体集積回路装置に設けられ、外部より入力される制御信号に応じて各I/Oセルの識別情報保持部に対し、そのI/Oセルのセル識別情報を出力させる制御部とを備え、外部のシミュレータ又はテスタを用いてピン番号情報を外部より入力して、各I/Oセルの識別情報保持部からセル識別情報を読み出し、ピン番号情報との対応を確認可能とした。

(もっと読む)

1 - 18 / 18

[ Back to top ]