Fターム[2H092KA11]の内容

液晶−電極、アクティブマトリックス (131,435) | 能動素子、光導電体層の材料 (8,799) | ゲート絶縁層 (1,439)

Fターム[2H092KA11]の下位に属するFターム

Fターム[2H092KA11]に分類される特許

21 - 39 / 39

表示装置の欠陥検出方法および表示装置の欠陥検出装置

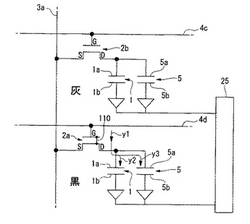

【課題】 マトリクス構造における進行性のある欠陥を容易に検出可能にする。

【解決手段】 マトリクス構造で格子状に交差する複数のゲート線4c、4d及び複数のデータ線3aを有する。複数のゲート線4c、4d及び複数のデータ線3aの交差部毎に配置された画素部2aに所定の駆動電圧が印加される。駆動電圧よりも大きな電圧を画素部に印加して欠陥110の進行を加速させる工程と、駆動電圧を画素部2aに連続的に印加して欠陥110の進行を加速させる工程との少なくともいずれか一方の工程を有する。

(もっと読む)

画素構造、アクティブマトリクス基板、アクティブマトリクス基板の製造方法、電気光学装置、並びに電子機器

【課題】 製造プロセスにおける半導体層の熱的制限の影響が少なく、低コスト化に有利な画素構造を提供する。

【解決手段】 画素構造は、画素電極20と、この画素電極20に対応するスイッチング素子10とを有する。画素電極20とスイッチング素子10とが同一の基板P上に形成されており、スイッチング素子10における半導体層11に比べて基板P側の層(第1層L1)に画素電極20が配されている。

(もっと読む)

アクティブマトリクス基板用中間生成物、アクティブマトリクス基板の製造方法及びアクティブマトリクス基板

【課題】 第1支持基板から第2支持基板に転写する際に、アクティブマトリクス素子の構造や機能を破壊することがなく、信頼性の高いアクティブマトリクス基板の製造方法及びこの製造方法によって得られるアクティブマトリクス基板を提供する。

【解決手段】 第1支持基板21と、この第1支持基板21上に設けられた、この第1支持基板21とは材質及び組成の少なくとも一方が異なる第1成膜層22と、この第1成膜層22上に設けられた、この第1成膜層22とは材質及び組成の少なくとも一方が異なる第2成膜層13と、この第2成膜層13上に設けられた、この第2成膜層13とは材質及び組成の少なくとも一方が異なる第3成膜層14と、この第3成膜層14上に設けられた薄膜トランジスタ(15S,15C,15D,16,17,19,20)を有する画素のマトリクスとを備える。

(もっと読む)

電気光学装置及びその製造方法、薄膜トランジスタ、電子機器

【課題】 半導体層を挟んだ両側にそれぞれゲート電極が配された薄膜トランジスタにおける前記両ゲート電極の電圧印加効果を良好なものとして薄膜トランジスタのスイッチング特性を十分に発揮させ、もって良好な高精細表示を得られるようにした電気光学装置を提供する。

【解決手段】 本発明の電気光学装置は、半導体層42と、該半導体層42のチャネル領域の一面側に下地絶縁膜12(第1絶縁膜)を介して対向する第1ゲート配線15b(第1ゲート電極)と、前記チャネル領域の他面側に絶縁薄膜2(第2絶縁膜)を介して対向するゲート電極32(第2ゲート電極)とを具備したTFT30を備えており、前記半導体層42は、前記第1ゲート配線15bと対向する第1ポリシリコン膜42aと、前記ゲート電極32(33)と対向する第2ポリシリコン膜42bとの積層膜からなるものとされている。

(もっと読む)

電気光学装置、電子機器

【課題】 同一基板上に高速動作可能な周辺駆動回路と高耐圧な画素回路の双方を備えた電気光学装置を提供する。

【解決手段】 本発明の電気光学装置は、同一基板10上に画素回路と周辺駆動回路とを備えた電気光学装置であって、前記画素回路と前記周辺駆動回路はそれぞれ多結晶半導体層30s,32sを備えたトランジスタ30,32を含み、前記画素回路のトランジスタ30はトップゲート型の構造を有し、前記周辺駆動回路用のトランジスタ32はボトムゲート型の構造を有することを特徴とする。

(もっと読む)

液晶表示装置とその製造方法

【課題】アクティブ基板上に柱状スペーサを形成し、液晶表示装置の生産コストの低減を図る。

【解決手段】アクティブ基板を保護する機能を有するパシベーション絶縁層またはソース・ドレイン配線上に形成された感光性有機絶縁層パターンの形成にあたり、ハーフトーン露光技術を併用して、パシベーション絶縁層上に局所的に感光性有機絶縁層パターンを形成する、感光性有機絶縁層よりなるパシベーション絶縁層の一部の膜厚を厚く形成する、あるいはソース・ドレイン配線上に形成された感光性有機絶縁層の一部の膜厚を厚く形成する等の手段によりアクティブ基板上に柱状スペーサを形成する。

(もっと読む)

半透過型液晶表示装置

【課題】半透過型液晶表示装置の光漏れを抑制する。

【解決手段】半透過型液晶表示装置は、所定の間隙を介してお互いに接合した一対の基板1と、間隙に保持された液晶とからなる。片方の基板1には行状の走査線4と列状の信号線5とこれらを被覆する平坦化膜6とこれら走査線4及び信号線5によって駆動される行列状の画素7とが形成されている。各画素7は上下の走査線4と左右の信号線5とで区画されている。各画素7は反射電極が形成された反射領域8と透明電極が形成された透過領域9とに上下で分かれている。信号線5より幅の太い遮光膜10が信号線5と基板1の表面との間に介在しており、透過領域9で信号線5の脇からの光漏れを防止する。

(もっと読む)

電子装置製造方法及び電子装置

導電部所有体500の表面に被覆膜100を形成する工程と、上記被覆膜100が形成された導電体500上に感光性膜110を形成する工程と、上記感光性膜110を、凹部又は凸部のパターンに対応するパターンに露光する工程と、上記露光された感光性膜110を現像する工程と、上記現像された感光性膜110をベーキングする工程とを有する電子装置の製造方法。該製造方法により、金属膜が必要以上に除去されてしまう現象を防止又は緩和する。  (もっと読む)

(もっと読む)

薄膜トランジスタ及びその製造方法

【課題】高速動作が可能であり、小型化が可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、透明なサファイア基板10と、サファイア基板10の所定領域を覆うSi02膜と、Si02膜上に形成されており、ソース領域20a1、ドレイン領域20a3及びチャンネル領域20a2を備える単結晶シリコン層20aと、

単結晶シリコン層20aのチャンネル領域20a2上に順次積層されたゲート絶縁膜26及びゲート電極28と、を備えている。

(もっと読む)

薄膜半導体装置、電気光学装置、電子機器、薄膜半導体装置の製造方法、及び薄膜電子装置

【課題】 例えばTFT等の薄膜半導体装置において、耐電圧性を高め、オフリーク電流を低減する。

【解決手段】 チャネル領域、ソース領域及びドレイン領域を含むと共に島状の平面パターンを有する半導体膜と、この上又は下に積層されたゲート絶縁膜と、これを介してチャネル領域に対向配置されたゲート電極とを備える。ゲート絶縁膜は、半導体膜における島状の平面パターンの周辺領域とゲート電極との層間に挟持される第1部分において、局所的に厚く形成されている。

(もっと読む)

液晶表示装置の作製方法

【課題】 本発明は、材料の利用効率を向上させ、少ないフォトマスク数で、しきい値のずれが生じにくく、高速動作が可能なTFTを有する液晶表示装置の作製方法を提供する。

【解決手段】 本発明は、非晶質半導体膜に触媒元素を添加し加熱して、結晶性半導体膜を形成するとともに該結晶性半導体膜から触媒元素を除き、その後逆スタガ型薄膜トランジスタを作製する。また本発明は、薄膜トランジスタのゲート電極層と画素電極層を同工程同材料を用いて液滴吐出法により選択的に形成し、工程の簡略化と、材料のロスの軽減を達成する。

(もっと読む)

薄膜半導体装置、電気光学装置、および電子機器

【課題】 同一基板上に形成されたTFTと容量素子に対して、高い耐電圧を確保するとともに、容量素子の静電容量を向上可能な薄膜半導体装置、電気光学装置、および電子機器を提供すること。

【解決手段】 TFTアレイ基板10において、誘電体膜2cは、第1領域1cの外側領域には、第1領域201cよりも膜厚が厚い第2領域202cを備えているので、蓄積容量70の耐電圧が高い。従って、蓄積容量70では、高い耐電圧が得られるとともに、耐電圧を高くするために誘電体膜2cの膜厚を厚くしたことに起因する静電容量の低下を最小限に止めることができる。よって、同一基板上に形成されたTFT30と蓄積容量70に対して、高い耐電圧を確保するとともに、蓄積容量70の静電容量を向上することができる。

(もっと読む)

半透過型液晶表示装置

【課題】透過型液晶表示装置として使用したとき、及び反射型液晶表示装置として使用したときのいずれにおいても良好な表示品質が得られる半透過型液晶表示装置を提供する。

【解決手段】1つの画素毎に、反射電極120と、透明電極122と、反射電極120に接続されたTFT116と、透明電極122に接続されたTFT117とを形成する。そして、反射電極120にTFT116を介して第1のデータ信号を書き込み、透明電極122にTFT117を介して第2のデータ信号を書き込む。このように、反射電極120及び透明電極122に個別のデータ信号を書き込むことにより、透過型液晶表示装置として使用したとき、及び反射型液晶表示装置として使用したときのいずれにおいても良好な表示品質が得られる。

(もっと読む)

半透過型液晶表示装置及びその製造方法

【課題】透過型液晶装置として使用したとき、及び反射型液晶表示装置として使用したときのいずれの場合であっても良好な表示品質を得ることができ、且つ製造が容易な半透過型液晶表示装置及びその製造方法を提供する。

【解決手段】ゲートバスライン111と同じ層に制御電極113を形成する。また、ゲートバスライン111及び制御電極113を覆う絶縁膜115の上に反射電極120を形成する。制御電極113はTFTのソース電極118sと電気的に接続し、反射電極120は制御電極113と容量結合する。TFT及び反射電極の上に絶縁膜121を形成し、反射電極120が露出する開口部を形成した後、全面に透明導電体膜を形成し、この透明導電体膜をパターニングして、透明電極122a〜122cを形成する。透過領域の透明電極112a,112cは、TFTのソース電極118sと電気的に接続される。

(もっと読む)

薄膜トランジスタパネル及びその製造方法

【課題】 アモルファスシリコン薄膜トランジスタとポリシリコン薄膜トランジスタとを備えた薄膜トランジスタパネルにおいて、より一層の小型化を図る。

【解決手段】 アモルファスシリコンからなる半導体薄膜42を有する光電気変換型の薄膜トランジスタ3は、ポリシリコンからなる半導体薄膜25、26を有する駆動回路用のCMOS薄膜トランジスタ21、22よりも上層側に設けられている。これにより、半導体薄膜42を半導体薄膜25、26と同一の層上に設ける場合と比較して、より一層の小型化を図ることができる。この場合、薄膜トランジスタ3のボトムゲート電極9、ソース・ドレイン電極10及びトップゲート電極8と薄膜トランジスタ21、22のソース・ドレイン電極に接続される導電体層35、36とを接続するための上層接続配線49、52、55、58は、トップゲート電極8を覆う層間絶縁膜40上に設けられている。

(もっと読む)

薄膜トランジスタパネル及びその製造方法

【課題】 アモルファスシリコン薄膜トランジスタとポリシリコン薄膜トランジスタとを備えた薄膜トランジスタパネルにおいて、より一層の小型化を図る。

【解決手段】 アモルファスシリコンからなる半導体薄膜41を有する光電気変換型の薄膜トランジスタ3は、ポリシリコンからなる半導体薄膜25、26を有する駆動回路用のCMOS薄膜トランジスタ21、22よりも上層側に設けられている。これにより、半導体薄膜41を半導体薄膜25、26と同一の層上に設ける場合と比較して、より一層の小型化を図ることができる。この場合、薄膜トランジスタ3のボトムゲート電極9、ソース・ドレイン電極10及びトップゲート電極8と薄膜トランジスタ21、22のソース・ドレイン電極を含む導電体層35、36とを接続する接続配線の一部である上層接続配線48、51、54は、トップゲート電極8が設けられたトップゲート絶縁膜39上に設けられている。

(もっと読む)

半導体装置及び半導体装置の駆動方法

【課題】ゲッタリングのための構造として、電極としても用いることができ、かつ遮光を実現する構造としての、半導体素子の支持体及び半導体素子の支持体の駆動方法を提供する。

【解決手段】半導体素子の支持体100上に形成されているMOSトランジスタ302や、保持容量303等の半導体素子に印加されている最低電位を0Vとしたとき、半導体素子の支持体100の構成要素であるタングステン膜103には、−3Vの電位を与えて駆動する。タングステン膜103に半導体素子の最低電位0Vよりも低い電圧が与えられているため、珪酸ガラス基体101や酸化珪素膜102、104に存在している正の電荷を有する可動性のあるナトリウムイオン等のアルカリ金属は、低い電位に保たれているタングステン膜103の方へ移動し、タングステン膜103に捕らえられることで固定される。

(もっと読む)

半導体装置およびその作製方法

【課題】 高い開口率を得ながら十分な保持容量(Cs)を確保し、また同時に容量配線の負荷(画素書き込み電流)を時間的に分散させて実効的に低減する事により、高い表示品質をもつ液晶表示装置を提供する。

【解決手段】 ゲート電極106と異なる層に走査線102を形成し、容量配線107が信号線109と平行になるよう配置する。各画素はそれぞれ独立した容量配線107に誘電体を介して接続されているため隣接画素の書き込み電流による容量配線電位の変動を回避でき、良好な表示画像を得る事ができる。

(もっと読む)

液晶表示セル

【課題】 OCB液晶表示装置の黒表示時の青味を低減する。

【解決手段】 対向電極Ecomを配置した対向基板130および画素電極Dpixを配置したアレイ基板120間にベンド配列される液晶層140を挟持し、前記基板の一方に赤、緑、青の各色フィルタ層を備える液晶表示セル11において、対向電極は青色フィルタ層に対応する部分Ecom(B)の膜厚tBが正面反射率の分光スペクトルにおける最小値が380nm〜480nm内になるように、かつ、 100nm<tB≦140nmに設定される。

(もっと読む)

21 - 39 / 39

[ Back to top ]