Fターム[2H092NA26]の内容

液晶−電極、アクティブマトリックス (131,435) | 目的 (17,448) | その他 (8,438) | 省電力化 (311)

Fターム[2H092NA26]に分類される特許

141 - 160 / 311

液晶表示パネル

【課題】補助容量を適宜に設定することによって、開口率が大きくしかも消費電力も小さ

くすることのできるFFSモードの液晶表示パネルを提供すること。

【解決手段】本発明の液晶表示パネル10Aは、液晶層を挟持して対向配置された一対の

基板を有し、前記一対の基板の一方には複数のスリット19を有する上電極20と、前記

上電極20と絶縁膜17、18を介して前記基板側に平面視で前記上電極20と一部が重

なるように形成された下電極16aと、を備えた液晶示パネル10Aにおいて、前記下電

極16aには前記上電極20のスリット19と平行にスリットが形成されており、前記下

電極16aのスリット15aは平面視で前記上電極20と重畳する位置に形成されている

ことを特徴とする。

(もっと読む)

表示装置及び液晶表示装置

【課題】開口率が高く、明所でも暗所でも視認性が高く高品位な表示を行い、かつ低消費電力な表示装置および液晶表示装置を提供する。

【解決手段】薄膜トランジスタ基板20には、画素1の透過光の輝度を制御する透明電極3と、透明電極3と併置され、画素1の反射光の輝度を制御する反射電極2と、透明電極3および反射電極2に映像情報等を伝送する信号線4と、信号線4と交差して配置され、薄膜トランジスタ10A・10Bの駆動を制御する走査線5A・5Bと、画素1の電位を安定化させるための補助容量を形成する補助容量配線9とを備え、補助容量配線9は、反射電極2の下方に設けられ、薄膜トランジスタ10A・10Bは、信号線4の下方、または反射電極2の下方、または走査線5A・5Bの下方に設けられている。

(もっと読む)

液晶セル

【課題】外光の強度を正しくかつ安定的に測定するための液晶セルを提供する。

【解決手段】第1偏光板5は光センサ11を覆うように、この場合、表示領域と額縁領域を占有するように配置される。第2偏光板7は光センサ11を覆うように、この場合、同様に、表示領域と額縁領域を占有するように配置される。第1接着剤層6は導電性を有し、第2接着剤層8も導電性を有するものとなっている。例えば、第1接着剤層6は、導電性を有する粒子が添加された接着剤により形成される。例えば、第2接着剤層8も同様である。

(もっと読む)

アクティブマトリクス基板、これを備えたパネル型表示装置、及びアクティブマトリクス基板の製造方法

【課題】アクティブマトリクス基板上における各トランジスタの利用目的に応じてその配置の方向を変更し、効率の良い回路設計を行う。

【解決手段】本発明のアクティブマトリクス基板は、ゲートドライバ21(第2の電気回路)およびソースドライバ22(第1の電気回路)が設けられた周辺領域を有している。ゲートドライバ21およびソースドライバ22に設けられている各トランジスタ25・26は、基板上にラテラル成長させて形成された結晶化半導体膜41を含んで構成されている。ソースドライバ22内に形成されているトランジスタ26では、半導体膜41内の結晶の成長方向D1に沿って、ソース電極45およびドレイン電極46が配置されている。一方、ゲートドライバ21内に形成されているトランジスタ25では、ソース電極45およびドレイン電極46の配置が成長方向D1に沿っているものと、沿っていないものとが混在している。

(もっと読む)

表示素子

【課題】表示むらおよび消費電力を抑制し、かつ、高速駆動が可能な液晶パネルを提供する。

【解決手段】少なくとも酸化物半導体により形成した活性層33cを備えたnチャネル型の複数の画素駆動用TFT33を備える。非酸化物半導体により形成した活性層45cを備えた複数の駆動回路用TFT45を備える。活性層33cの欠陥密度のばらつきを抑制しかつ閾値電圧が相対的に低い画素駆動用TFT33によって副画素を駆動するので、表示むらおよび消費電力を抑制できる。ドライバを電界効果移動度が高い非酸化物半導体によって形成した活性層45cを有する駆動回路用TFT45により駆動できるので、高速駆動が可能になる。

(もっと読む)

薄膜トランジスタ

【課題】欠陥を低減することが可能な非晶質半導体層及びその作製方法を提供する。または、薄膜トランジスタに代表される半導体素子の動作特性が改善されるように、非晶質半導体層の膜質を制御する。または、非晶質半導体層の堆積過程を制御して、TFTに代表される半導体素子の特性向上を図る。または、薄膜トランジスタのオン電流及び移動度を向上させる。

【解決手段】絶縁表面を有する基板上に、ゲート電極を覆うゲート絶縁層と、ゲート絶縁層上に非晶質半導体層と、非晶質半導体層上に一導電型を付与する不純物元素を含む半導体層と、を有し、非晶質半導体層はNH基を有するトランジスタとする。非晶質半導体層において、ダングリングボンドをNH基で架橋することにより、非晶質半導体層の欠陥を低減する。

(もっと読む)

電気光学パネル、電気光学装置、これを搭載した電子機器、および、これに用いられる駆動IC

【課題】液晶表示装置などの電気光学装置において、DAC回路の構成を工夫することで駆動ICのコストを下げ、サイズも増大させない。

【解決手段】複数の基準電位を取り出すことができる基準電位回路(第1のラダー抵抗511)は基板としてのアクティブマトリクス基板101上に形成されており、駆動IC921は、基板としてのアクティブマトリクス基板101上に実装されている。駆動IC921は、基準電位回路の基準電位を用いてデジタル信号をアナログ電位に変換する。また、基準電位回路は、基板としてのアクティブマトリクス基板101上において、駆動IC921が実装される領域形成されてる。

(もっと読む)

電気光学装置および電子機器

【課題】光電変換特性が高く、かつ、光電変換特性の経時変化が小さい光センサ素子を素子基板上に効率よく形成することのできる光センサ付き電気光学装置、および当該光センサ付き電気光学装置を備えた電子機器を提供すること。

【解決手段】液晶装置などの電気光学装置の素子基板10上に薄膜トランジスタ構造の光センサ用半導体素子1hを構成するにあたって、結晶粒径が数nmから100nmの微結晶シリコン膜を半導体膜2dとして用いる。また、素子基板10上には画素スイッチング用の薄膜トランジスタも形成されているが、かかる薄膜トランジスタの能動層にも微結晶シリコン膜を用いる。

(もっと読む)

液晶表示装置

【課題】製造時にマスクずれ等の誤差があっても安定した光検知特性が得られ、外光検出の信頼性を高めた光検知部を備えた液晶表示装置を提供する。

【解決手段】アクティブマトリクス基板と、カラーフィルタ基板と、アクティブマトリクス基板とカラーフィルタ基板との間に狭持された液晶層と、アクティブマトリクス基板上に形成されたTFTからなる光検知部Lsを有する光検知部LSと、TFTからなる光検知部Lsのソース電極SLに接続された配線部分15及びドレイン電極DLに接続された配線部分14との間に形成された容量部CXと、を備えた液晶表示装置であって、容量部CXは、ソース電極SLに接続された配線部分15又はドレイン電極DLに接続された配線部分14の一部を櫛歯状に形成することにより形成されたものである。

(もっと読む)

表示装置の画素を用いて、通信リンクを介して光情報を伝達するシステムおよび方法

光情報ビットを送信するのに、表示装置の少なくとも1つの表示用画素を、および光情報ビットを受信するのに、表示装置の少なくとも1つの検知用画素を使う、光通信リンクを介して通信するシステムが提供される。光情報ビットを送信するために、表示装置のコントローラは、送信表示用画素を、少なくとも第1および第2の光学表示条件の間で切り換えさせて、1つまたは複数の情報ビットを表す変調光信号を生じる。光情報ビットを受信するために、コントローラは、受信検知用画素によって発生された電気検知信号を読み取り、受信用画素から読み取られた電気検知信号を、1つまたは複数の情報ビットに対応するものとして解釈する。  (もっと読む)

(もっと読む)

表示装置及び電子機器

【課題】薄膜トランジスタを使用したメモリ回路において、トランジスタのバラツキによって、メモリ回路の歩留まりの低下や、応答速度の低下などの問題が発生していた。

【解決方法】本発明は、メモリセルの論理振幅と異なる電圧でワード線を駆動することによって、メモリセルの歩留まり向上、応答速度の向上を図るものである。本発明はSRAM、DRAM、マスクROMなどに適応が可能であり、本発明のメモリ回路を表示装置と一体形成することで、より多機能な表示装置を構成することが可能になる。

(もっと読む)

電気光学装置、および電子機器

【課題】電気光学装置の小型化と画像データの転送の際の省電力化を図る。

【解決手段】複数の走査線、複数のデータ線、及び複数の画素が形成される画素領域104を有する電気光学パネル100と、電気光学パネルの基板102に実装され、複数のデータ線にデータ信号を供給する少なくとも1つのデータドライバSD1、SD2と、基板102に実装され、少なくとも1つのデータドライバを制御する表示コントローラLCと、を含み、表示コントローラは、少なくとも1画面分の画像データを記憶する表示メモリMBと、表示メモリの制御処理と、外部とのインターフェース処理を行う制御ロジック回路LOGと、を含み、表示コントローラ及び少なくとも1つのデータドライバは、画素領域の第1の辺である第1の画素領域側辺SA1と、電気光学パネルの第1の辺であって第1の画素領域側辺に対向する第1のパネル側辺SB1との間に設けられる。

(もっと読む)

検査回路、電気光学装置、及び電子機器

【課題】液晶装置に搭載された検査回路に発生する消費電力を低減し、且つ液晶装置の誤動作を低減する。

【解決手段】液晶装置100では、その動作時、即ち、液晶装置100が画像を表示している際に、シフトレジスタ162に電源VDDCが供給されていない状態で電源VDDYを電源として走査線駆動回路104が駆動されることによって画像が表示可能となるため、液晶装置100の動作時にシフトレジスタ162で消費される電力を低減できる。加えて、電源VDDYが供給される外部回路接続端子102aと、電源VDDCが供給される検査用端子111とが、物理的に別々に設けられているため、液晶装置100の動作時に電源VDDCを供給する電源回路を検査用端子111に電気的に接続しないことによって、電源VDDYがシフトレジスタ162に供給されることがなく、シフトレジスタ162で消費される電力を確実に低減できる。

(もっと読む)

接触及び接近を感知することができるディスプレイパネルとディスプレイ装置及びそのパネルを用いる接触及び接近感知方法

本発明は、接触及び接近を感知することができるディスプレイパネルとディスプレイ装置及びそのパネルを利用した接触及び接近の感知方法を提供する。このディスプレイパネルは、マトリックス状に配列された複数個のピクセル、映像が出力される方向に配置されるピクセル基板、上記ピクセルに対向する位置に配置される共通電極を備える共通基板、及び接触感知モード時に複数個のデータラインを介して複数個のピクセル電極の静電容量を感知して接触物体の接触及び接近位置を判別するパネル制御部を備えることを特徴とする。したがって、別途のタッチスクリーンを備えなくても、ディスプレイパネルが接触及び接近を感知することができる。  (もっと読む)

(もっと読む)

薄膜トランジスタにおけるN型半導体材料

シクロアルキル基のトランス立体配置では赤道配向を成し、シクロアルキル基のシス立体配置では軸配向を成す、少なくとも1つのフッ素化置換基を4位置に有する少なくとも1つのシクロアルキル基を有するN,N’−1,4,5,8−ナフタレンテトラカルボン酸ジイミドを含む有機半導体の層を含んで成る薄膜トランジスタ。このトランジスタは、誘電体層、ゲート電極、ソース電極及びドレイン電極を有する電界効果トランジスタとなることができる。ゲート電極と有機半導体材料の薄膜との両方が絶縁層と接触し、そしてソース電極とドレイン電極との両方が有機半導体材料の薄膜と接触している。  (もっと読む)

(もっと読む)

液晶表示装置

【課題】電源がオフ状態であっても所定の文字や絵、模様等を視認できるようにした液晶

表示装置を提供すること。

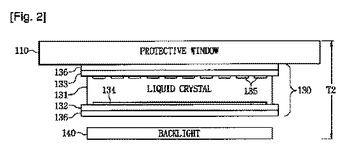

【解決手段】本発明の液晶表示装置1Aは、液晶を挟持して対向配置された一対の基板を

備え、前記一対の基板のそれぞれに光反射領域15及び光透過領域16を有するサブ画素

10Aが複数形成された表示領域を有していると共に、バックライトを備えた液晶表示装

置1Aにおいて、前記複数のサブ画素10Aのそれぞれの前記光反射領域15及び光透過

領域16は互いに独立して駆動され、電源オフ時に特定画像を継続して表示させる際に、

前記光反射領域15を一旦直流駆動して前記特定画像を表示した後に電源オフ状態とする

ことを特徴とする。

(もっと読む)

表示装置

【課題】累乗係数を考慮した感度補正機能を備え、かつ簡便な工程で製造することができ

る光量検出装置を有する表示装置を提供すること。

【解決手段】本発明の表示装置1は、第1の光検出回路LS1及び減光手段を備えた第2

の光検出回路LS2を有する光検出部10と、光センサ読み取り部20を備え、前記光セ

ンサ読み取り部20は、前記光検出部10の出力信号Sa及びSbから光劣化累乗補正係

数Kを演算する光劣化係数演算部21と、前記光劣化累乗補正係数Kから変化した累乗係

数a',b'を演算して累乗補正後の前記第1及び第2の出力信号を求め、この累乗補正後

の前記第1及び第2の出力信号の比率と前記初期比率と、の比率である光劣化傾き補正係

数K"を演算する光劣化率演算部22と、前記光劣化傾き補正係数K"に基づいて前記第1

又は第2の出力信号を初期状態の光量信号となるように補正して出力する光信号出力部2

4と、を備えている。

(もっと読む)

液晶装置

【課題】従来の液晶装置では、信頼性の向上を図ることが困難である。

【解決手段】互いに対向する第1基板51及び第2基板81と、第1基板51及び第2基板81間に介在する液晶19と、第2基板81と液晶19との間に介在する位相差膜95と、第1基板51と位相差膜95との間に設けられ、平面視で液晶19を囲むシール材21と、位相差膜95及びシール材21の間に設けられた保護膜105と、を有することを特徴とする液晶装置。

(もっと読む)

保護回路及びそれを有する表示装置

【課題】保護回路の電気的特性を良好にさせ、占有面積を小さくすることを目的の一とする。また、薄膜トランジスタを有する表示装置の信頼性を高めることを目的の一とする。

【解決手段】基板上に形成される第1配線と、第1配線と交差する第2配線と、第1配線及び第2配線を絶縁する絶縁膜とが形成され、第1配線及び第2配線の交差部において、第1配線または第2配線の一方が、第1配線または第2配線の他方側へ突出する保護回路である。また、第1配線及び第2配線を絶縁する絶縁膜は、第1配線及び第2配線の交差部において、凹部または分離部が形成され、当該領域において、第1配線または第2配線の一方が、第1配線または第2配線の他方側に突出する保護回路である。

(もっと読む)

液晶表示装置

【課題】画素トランジスタとしてアモルファス・シリコン薄膜トランジスタを使用し、周辺回路に低温ポリシリコン薄膜トランジスタを使用する場合に、画素容量への映像電圧の書き込み不足が生じるのを防止する。

【解決手段】複数の映像線は、n(n≧3)個の映像線毎にグループ分けされており、分割スイッチ回路の複数のスイッチング素子は、n個のスイッチング素子毎にグループ分けされており、各画素トランジスタは、半導体層としてアモルファス・シリコンを使用するアモルファス・シリコン薄膜トランジスタであり、分割スイッチ回路の各スイッチング素子は、半導体層としてポリ・シリコンを使用するポリ・シリコン・薄膜トランジタであり、各グループの中で一番最後にオンとなるスイッチング素子を介して映像電圧が供給される画素に対する書き込み時間は、各グループの中で一番最後にオンとなるスイッチング素子がオンとなる時間を除いて、1水平走査期間の1/2以上である。

(もっと読む)

141 - 160 / 311

[ Back to top ]