Fターム[2H092NA26]の内容

液晶−電極、アクティブマトリックス (131,435) | 目的 (17,448) | その他 (8,438) | 省電力化 (311)

Fターム[2H092NA26]に分類される特許

101 - 120 / 311

表示システム、スクリーンおよびプロジェクター

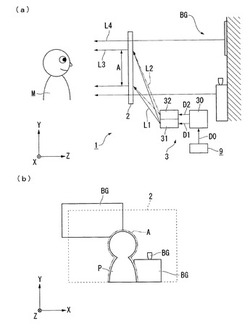

【課題】臨場感溢れる映像を表示可能な表示システムを提供する。

【解決手段】本発明の表示システム1は、不可視光L2が入射した領域ごとに、可視光L1を散乱させる散乱状態と可視光を透過させる透過状態とが切替わるスクリーン2と、スクリーン2に可視光L1による画像を投射する画像投射系31と、画像投射系31により画像が投射される領域が散乱状態になるように、スクリーン2に不可視光L2を投射する不可視光投射系32と、を備えている。

(もっと読む)

画素アレイ及びその駆動方法、並びに該画素アレイを備えた表示パネル

【課題】テストのプログラムが簡単である画素アレイ及びその駆動方法、並びに表示パネルを提供することを目的とする。

【解決手段】スキャン線G(2n−1)は、画素P(2m−1,n)及びP(2m+2,n)の制御端に接続され、スキャン線G(2n)は、画素P(2m,n)及びP(2m+1,n)の制御端に接続され、データ線X(m)は、画素P(2m−1,n)及びP(2m,n)のデータ端に接続され、ソース駆動回路は複数のデータ線に接続され、第tフレーム期間において、ソース駆動回路は、データ線X(m)を通じて、それぞれ「正、負、負、正、負、正、正、負」の極性で、画素P(2m−1,n)、P(2m,n)、P(2m−1,n+1)、P(2m,n+1)、P(2m−1,n+2)、P(2m,n+2)、P(2m−1,n+3)及びP(2m,n+3)を順次に駆動する(変数は全て整数である)。

(もっと読む)

電子装置用配線基板、その製造方法及びタッチパネル

【課題】配線としての積層膜の電気抵抗を低減し消費電力も低減することができるようにする。

【解決手段】本発明は、絶縁性透明基板2上に回路配線を備えた電子装置用配線基板1において、回路配線は、銅と微量の添加元素とからなる配線本体5と、配線本体5の外周側に形成された、絶縁性透明基板に接している第1の被膜層61と、絶縁性透明基板に接していない第2の被膜層62とを有し、第1および第2の被膜層61,62は、膜厚みが異なるとともに、厚み大である被膜層61は、透明な酸化物導電膜を形成しうる無機元素の酸化物と、添加元素の酸化物とを含む複合酸化物であり、第1および第2の被膜層61,62中の添加元素の濃度は、配線本体5中の添加元素の濃度よりも高い、ことを特徴としている。

(もっと読む)

半導体装置およびその作製方法

【課題】開口率の高い半導体装置またはその製造方法を提供する。また、消費電力の低い半導体装置またはその製造方法を提供する。

【解決手段】第1の薄膜トランジスタを有する画素部と第2の薄膜トランジスタを有する駆動回路を有し、第1の薄膜トランジスタは、ゲート電極層とゲート絶縁層と半導体層とソース電極層及びドレイン電極層を有し、第1の薄膜トランジスタのゲート電極層、ゲート絶縁層、半導体層、ソース電極層、ドレイン電極層は透光性を有し、第2の薄膜トランジスタのゲート電極層は、第1の薄膜トランジスタのゲート電極層と材料が異なり、第1の薄膜トランジスタのゲート電極層よりも低抵抗の導電層を有し、第2の薄膜トランジスタのソース電極層及びドレイン電極層は、第1の薄膜トランジスタのソース電極層及びドレイン電極層と材料が異なり、第1の薄膜トランジスタのソース電極層及びドレイン電極層よりも低抵抗の導電層を有する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

半導体装置

【課題】消費電力を抑えつつ、走査線へ十分な振幅の信号を供給することができる半導体装置の提供を課題の一とする。また、消費電力を抑えつつ、走査線に供給する信号のなまりを抑制し、立ち上がり時間又は立ち下がり時間を短くすることができる半導体装置の提供を課題の一とする。

【解決手段】表示素子及び少なくとも1つの第1トランジスタをそれぞれ有する複数の画素と、複数の画素を選択するための信号を走査線に供給する走査線駆動回路とを有し、表示素子の画素電極層と、第1トランジスタのゲート電極層、ソース電極層及びドレイン電極層と、走査線とは、透光性を有する導電膜を用いており、走査線駆動回路は、第2トランジスタと、第2トランジスタのゲート電極層とソース電極層の間の電圧を保持する容量素子と、を有しており、第2トランジスタのソース電極層は走査線に接続されている半導体装置。

(もっと読む)

タッチスクリーン液晶表示装置

【課題】データピクセルラインとリードピクセルラインを共有する構造の液晶モジュールを利用してデータをピクセルに保存して、タッチ情報を読み込むことができるようにデザインされたタッチスクリーン液晶表示装置を提供する。

【解決手段】本発明によるタッチスクリーン液晶表示装置によれば、データピクセルラインとリードピクセルラインを共有する構造の液晶モジュールを利用することで、小さなサイズの液晶パネルを利用しながらもデータピクセルの開口率を確保することができる長所がある。また、本発明によるタッチスクリーン液晶表示装置は、共有ラインを駆動する出力バッファーに供給されるバイアス電流を増加させるか、または共有ラインの出力バッファーに連結されたマルチプレクサーのサイズを大きくすることで、共有ラインで発生するディレイを償って出力波形の偏差を減らすことができる効果がある。

(もっと読む)

半導体装置

【課題】各種回路に配置される薄膜トランジスタの構造を、回路の機能に応じて適切なものとすることにより、半導体装置の動作特性および信頼性を向上させ、かつ、低消費電力化を図ると共に、工程数を削減して製造コストの低減および歩留まりの向上を実現することを目的とする。

【解決手段】薄膜トランジスタのLDD領域を、テーパー部を有するゲート電極及びテーパー部を有するゲート絶縁膜に対応させて設ける。具体的には、第1のLDD領域はゲート電極のテーパー部の下に設けられ、第2のLDD領域はゲート絶縁膜のテーパー部の下に設けられる。

(もっと読む)

薄膜トランジスタ、その製造方法及び液晶表示装置

【課題】オフ電流が小さく、電位保持特性が優れており、消費電力が低いと共に、動作速度も速い低温ポリシリコントランジスタを含む薄膜トランジスタ、この薄膜トランジスタの製造方法及びそれを使用した液晶表示装置を提供する。

【解決手段】ガラス基板10上にゲート電極11、ゲート絶縁膜12、チャネル領域、ソース・ドレイン電極15a,15bを形成した逆スタガ構造の薄膜トランジスタである。このチャネル領域は、ポリシリコン膜13と、このポリシリコン膜13の上面及び側面を覆うa−Si:H膜14とから構成されている。

(もっと読む)

露光装置、記録装置、記録システム及びプログラム

【課題】光書込型の表示媒体に情報を書き込む場合において、指示体により指示された位置に強い光が照射される時間を少なくする。

【解決手段】露光装置は、表示媒体の表示層に対して、指示体により指示された第1の期間と、その後の第2の期間とに光を照射する。その結果、露光装置は、指示体により指示が開始されてから終了するまでの指示期間に加え、指示期間に続く残光期間に光を照射する。これにより、残光期間に光を照射しない場合に比べ、指示期間に照射される光を弱めることが可能である。

(もっと読む)

表示装置及び封緘具

【課題】再書き込みを行わずに表示する画像を切り替える。

【解決手段】表示部3は、表示される画像を規定する電位を保持するデジタルメモリ素子618a〜618dと、該デジタルメモリ素子618a〜618dが保持する電位が供給されることによって表示を行う液晶セル614a〜614dとを含み、表示部3を構成する画素のうち、表示画素群に属する画素では、デジタルメモリ素子618a、618dから液晶セル614a、614dへ上記電位を供給して、表示部3に画像を表示し、かつ、非表示画素群に属する画素では、デジタルメモリ素子618b、618cから液晶セル614b、614cへ上記電位を供給せず、表示部3に画像を表示しないように制御するための、切替配線6、分岐配線7、デジタルメモリ素子621、及びAND回路622a〜622dを備えているので、再書き込みを行わずに表示する画像を切り替えることができる。

(もっと読む)

薄膜トランジスタ及びその製造方法、電気光学装置、並びにセンサー

【課題】オン電流が高く、特性シフトが低減された薄膜トランジスタを提供する。

【解決手段】基板上に、活性層としてのIn、Ga、及びZnを含む酸化物半導体膜と、ゲート電極と、ゲート絶縁膜と、ソース電極と、ドレイン電極と、を有し、

前記酸化物半導体膜のモル比〔In:Ga:Zn〕を2.0−x:x:y(但し、0.0<x<2.0、0.0<y)で表したとき、前記酸化物半導体膜の膜厚方向についての前記yの分布において、前記基板に近い側の膜面、及び、前記基板から離れた側の膜面よりも、前記yが大きい領域が存在する。

(もっと読む)

液晶表示装置

【課題】高表示品位を実現可能なFFSモードの液晶表示装置を提供する。

【解決手段】本発明に係る液晶表示装置は、平板状電極14と平面視上、重畳する領域を有し、ソース配線12L又はゲート配線11Lのいずれかと実質的に同一方向に複数のライン状のパターンが形成されるように、複数のスリット状の開口部を有するスリット電極15を具備する第1の基板91と、スリット電極のライン状のパターンと実質的に同一方向に延在され、ソース配線11L又はゲート配線11Lのいずれかと平面視上、重畳する領域を有し、かつ単色表示した際にカラーフィルタ膜32間の混色を防止するように配置した遮光膜31を具備する第2の基板92を備える。遮光膜31、スリット電極15が平面視上、重畳的に配置される領域において、遮光膜31によって透過率が低減しないように、スリット電極15の幅方向端部に遮光膜の非対向領域を形成した。

(もっと読む)

液晶表示パネル、液晶表示モジュール、および液晶表示装置

【課題】他のパネルと接続されていない単独の状態の液晶表示パネルでも、ソースバスライン容量に依存する消費電流の低減を可能とする。

【解決手段】液晶表示パネルは、アクティブマトリックス型の液晶表示パネルであって、上記液晶表示パネル内における複数の画素領域の少なくとも1つに、当該画素領域内に設けられているソースバスラインS1〜SxのON/OFFを切り換える切換部Tr11〜Trxyが備えられている。

(もっと読む)

表示装置および電子機器

【課題】静電容量型のタッチセンサを備えた表示装置において、シールド層を用いずに物体の検出精度を向上させることが可能な表示装置を提供する。

【解決手段】静電容量の変化に応じてタッチ検出電極から得られる検出信号Vdetに基づいて、物体の接触位置を検出する。また、検出回路8において、コモン駆動信号Vcomにおける極性反転前の検出信号Vdetを用いて、極性反転後における検出動作を行う。これにより、従来のようなシールド層を用いることなく、上記反転後ノイズの影響を取り除きつつ、極性反転後の検出動作を行うことができる。

(もっと読む)

低電力アクティブマトリクス型ディスプレイ

低い周波数でリフレッシュされる液晶ディスプレイ(LCD)における、電力消費量の低減及びデバイスのストレス蓄積の軽減のためのシステム及び方法が開示される。典型的な一実施形態において、LCD画素の電荷を保持するために、直列にされた2つ以上のトランジスタが使用される。トランジスタへの負ストレスを防止するため、上記2つ以上のトランジスタは交互に“オン”状態に駆動され、何れの1つのトランジスタも長い“オフ”時間を経験しないようにされる。他の一実施形態において、周辺ESD回路における動的電力消費及び静的電力消費を最小化するような、フレーム書込及びストレス緩和を実行する回路及び信号伝達波形が提供される。  (もっと読む)

(もっと読む)

半導体表示装置の作製方法

【課題】高精彩・高解像度・高画質・低消費電力の小型半導体表示装置を提供すること。

【解決手段】本発明の半導体表示装置は、画素マトリクス回路、データ線駆動回路、および走査線駆動回路を有しており、これらの構成要素が多結晶TFTによって同一基板上に形成される。また、その製造方法における、触媒元素を用いた結晶性の助長化プロセス、および触媒元素のゲッタリングプロセスによって、小型にもかかわらず、高精細・高解像度・高画質の半導体表示装置が提供される。

(もっと読む)

表示装置、その製造方法、および電子機器

【課題】照明付きの反射型の表示装置においてFPCの増加を抑える。

【解決手段】端子T1と、端子T1に電気的に接続された中継配線102と、液晶素子LCとを有し、液晶素子LCの光透過率を制御して階調を表示する表示体100と、陽極112及び陰極114を含み、陽極112と陰極114との間に供給される電源を用いて発光する発光素子P1と、陽極112と電気的に接続された接続部C1と、陰極と電気的に接続された接続部とを有し、発光素子P1を発光させて液晶素子LCを照らす照明体110と、中継配線102と接続部C1とを電気的に接続する導電体120と、他方の中継配線と陰極と電気的に接続された接続部とを電気的に接続する導電体とを備える。

(もっと読む)

スキャナー、電気光学パネル、電気光学表示装置及び電子機器

【課題】ブートストラップされた高電位による素子破壊や信頼性低下を効果的に防止する。

【解決手段】同一導電型のトランジスターで構成された複数の単位回路からなるスキャナーであって、前記スキャナーを構成する前記単位回路は、外部から与えられる信号を選択的に出力端子に出力する出力トランジスターを有し、前記出力トランジスターのゲート電極は電圧制限トランジスターの一端に接続され、前記電圧制限トランジスターのゲート電極は第1の電源電位が供給されるスキャナー。

(もっと読む)

液晶表示装置

【課題】製品の小型化を図ることができ、製品コストを抑制することができ、低消費電力化を図ることができる液晶表示装置を提供する。

【解決手段】液晶表示装置は、複数の信号線並びに複数の画素を有したアレイ基板と、対向基板と、液晶層と、を具備した液晶表示パネルと、それぞれN本の信号線に接続され、入力される映像信号をN本の信号線の何れかに選択的に与える複数の切替え素子群を含んだ切替え回路と、複数の切替え素子群に接続され、それぞれ複数の切替え素子群に映像信号を与えるドライバ回路81と、ドライバ回路に接続され、ドライバ回路が複数の切替え素子群に映像信号を与えるタイミングを制御するコントロール回路82と、を備えている。ドライバ回路81及びコントロール回路82は、多結晶化された同一のシリコンチップ80に形成されている。

(もっと読む)

101 - 120 / 311

[ Back to top ]