Fターム[2H092NA26]の内容

液晶−電極、アクティブマトリックス (131,435) | 目的 (17,448) | その他 (8,438) | 省電力化 (311)

Fターム[2H092NA26]に分類される特許

21 - 40 / 311

半導体装置の作製方法

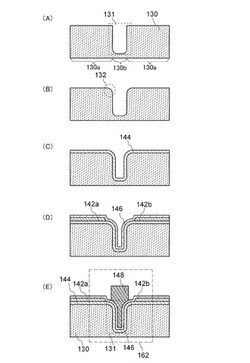

【課題】不良を抑制しつつ微細化を達成した半導体装置を提供する。

【解決手段】絶縁層に凸状部またはトレンチ(溝部)を形成し、該凸状部またはトレンチに接して半導体層のチャネル形成領域を設けることで、チャネル形成領域を基板垂直方向に延長させる。これによって、トランジスタの微細化を達成しつつ、実効的なチャネル長を延長させることができる。また、半導体層成膜前に、半導体層が接する凸状部またはトレンチの上端コーナー部に、R加工処理を行うことで、薄膜の半導体層を被覆性良く成膜する。

(もっと読む)

表示装置

【課題】簡便な構成及び動作によって表示装置の消費電力を低減すること。

【解決手段】表示装置が入力デバイスを備え、該入力デバイスから出力される画像操作信号に応じて、駆動回路に対する画像信号の入力を制御する。具体的には、入力デバイスが操作されない際の画像信号の入力頻度を、入力デバイスが操作される際の画像信号の入力頻度よりも低くする。これにより、当該表示装置が使用される際の表示の劣化(表示品質の低下)を抑制することが可能となり、且つ使用されない際の消費電力を低減することが可能になる。

(もっと読む)

光導電スイッチング素子、光導電スイッチング素子アレイ、表示装置および画像形成装置

【課題】省電力で駆動が可能な光導電スイッチング素子、光導電スイッチング素子アレイ、表示装置および画像形成装置を提供すること。

【解決手段】光導電スイッチング素子アレイ1は、第1の共通電極2と、第1の共通電極2に対向配置され、第1の共通電極2との間で電圧が印加される個別電極3と、第1の共通電極2と個別電極3との間に配置され、アドレス光L2を受光することにより導電性が発現する光導電層4とを備え、光導電層4は、アドレス光L2を受光した際に電荷を発生する機能を有する第1の電荷発生層41および第2の電荷発生層42と、第1の電荷発生層41および第2の電荷発生層42でそれぞれ発生した電荷を輸送する機能を有する電荷輸送層43とを備え、第1の電荷発生層41と第2の電荷発生層42とは、電荷輸送層43の面方向の異なる位置に配置され、電荷輸送層43の厚さ方向にも異なる位置に配置されている。

(もっと読む)

半導体装置および該半導体装置の作製方法

【課題】良好な電気特性を有する半導体装置および該半導体装置の作製方法を提供する。

【解決手段】ゲート電極を形成し、ゲート電極を覆ってゲート絶縁膜を形成し、ゲート絶縁膜上に酸化物半導体膜を形成し、酸化物半導体膜上に水素透過膜を形成し、水素透過膜上に水素捕縛膜を形成し、加熱処理を行って、酸化物半導体膜から水素を脱離させ、酸化物半導体膜の一部に接するソース電極およびドレイン電極を形成し、水素捕縛膜の露出されている部分を除去して、水素透過膜のチャネル保護膜を形成する半導体装置の作製方法である。また、該作製方法で作製された半導体装置である。

(もっと読む)

酸化物半導体膜、半導体装置および半導体装置の作製方法

【課題】酸化物半導体膜を用いたトランジスタに安定した電気的特性を付与し、信頼性の高い半導体装置を作製する。

【解決手段】酸化物半導体膜を活性層に用いるトランジスタにおいて、チャネル領域と隣接するソース領域およびドレイン領域に微小な空洞を設ける。酸化物半導体膜に形成されるソース領域およびドレイン領域に微小な空洞を設けることによって、微小な空洞に酸化物半導体膜のチャネル領域に含まれる水素を捕獲させることができる。

(もっと読む)

半導体装置

【課題】大面積化しても低消費電力を実現した半導体装置の構造およびその作製方法を提供する。

【解決手段】画面で使われる画素の薄膜トランジスタを作製する。その薄膜トランジスタにおいて、ソース配線、ゲート電極を同一平面上に作製する。また、ソース配線と薄膜トランジスタをつなぐ配線と、画素電極と薄膜トランジスタをつなぐ配線を同一工程で作製する。

(もっと読む)

液晶素子、液晶表示装置

【課題】2つの配向状態間の遷移を利用する新規な液晶素子の視角特性を向上させること。

【解決手段】液晶素子は、対向配置された第1基板及び第2基板、第1基板又は第2基板に設けられたプリズムアレイ、第1基板に設けられた第1配向膜、第2基板に設けられた第2配向膜、第1基板と第2基板の間に設けられた液晶層、第1基板の外側に配置された第1偏光板、第2基板の外側に配置された第2偏光板、第1基板及び第2基板に設けられた電圧印加手段を含む。第1基板及び第2基板は、液晶層の液晶分子を第1方向へ捻れさせるように各配向膜への配向処理の方向を配置される。液晶層は、液晶分子を第1方向とは逆の第2方向に捻れさせる性質のカイラル材を含有する。電圧印加手段は、少なくとも、第1基板に設けられた第1電極と第2基板に設けられた第2電極を有する。

(もっと読む)

表示装置

【課題】カップリング欠陥と縦線状欠陥を防止すると共に高速駆動を行うことができる表示装置を提供する。

【解決手段】画素PXは第1副画素電極及び第1薄膜トランジスタが接続された第1副画素PXaと第2副画素電極及び第2薄膜トランジスタが接続された第2副画素PXbを含み、各副画素はデータ線D1a〜D6b及びゲート線Gj−1〜Dj+2が接続され、ゲート線を挟んで上側に第1副画素PXam、下側に第2副画素PXbが配置され、第1薄膜トランジスタは第1副画素電極に接続されており、第2薄膜トランジスタは第2副画素電極に接続されており、画素PXは一つの色フィルターに対応している表示装置。

(もっと読む)

液晶表示装置およびその製造方法

【課題】反射型液晶表示装置の紫外線による劣化を防止し、反射率の低下、フリッカーのない良好な表示品位を得る。

【解決手段】絶縁性基板と透明電極との間に、波長365nmにおける透過率(T(365nm))と波長315nmにおける透過率(T(315nm))の比(T(365nm)/T(315nm))が6.3以上である紫外線吸収層を設ける。

(もっと読む)

半導体装置の作製方法

【課題】オフ電流の極めて小さい酸化物半導体膜を用いたトランジスタを提供する。また、該トランジスタを適用することで、消費電力の極めて小さい半導体装置を提供する。

【解決手段】基板上に加熱処理により酸素を放出する下地絶縁膜を形成し、下地絶縁膜上に第1の酸化物半導体膜を形成し、基板を加熱処理する。次に、第1の酸化物半導体膜上に導電膜を形成し、該導電膜を加工してソース電極およびドレイン電極を形成する。次に、第1の酸化物半導体膜を加工して第2の酸化物半導体膜を形成した直後にソース電極、ドレイン電極および第2の酸化物半導体膜を覆うゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極を形成する。

(もっと読む)

液晶表示装置及び電子機器

【課題】液晶素子に印加される電圧を異ならせて視野角特性を改善する。

【解決手段】 本発明の一は、一画素に三以上の液晶素子を有し、該液晶素子の各々に印

加される電圧値が異なる液晶表示装置である。各液晶素子に印加される電圧を異ならせる

には、加えた電圧を分圧する素子を配置することにより行う。印加される電圧を異ならせ

るためには、容量素子、抵抗素子、又はトランジスタ等を用いる。

(もっと読む)

表示装置及び電子機器

【課題】SRAMを用いたアクティブマトリクス型表示装置では、SRAM回路を構成するトランジスタ数が多く、画素面積が小さい場合、画素の中に入りきらない、もしくは開口率が低下するという問題があった。リフレッシュが不要で消費電力の小さな表示装置を提供する。

【解決方法】本発明は、画素をスイッチング素子と、不揮発性メモリ素子で構成する。不揮発性メモリ素子は強誘電体素子を用い、保持を行うことによって、静止画を表示する場合フレーム毎に書き込みを行う必要をなくすことができる。また、強誘電体メモリは占有面積が小さいので開口率を著しく落とすことなく、メモリを内蔵することができる。

(もっと読む)

半導体回路及びその駆動方法、並びに記憶装置、レジスタ回路、表示装置、及び電子機器

【課題】トランジスタのしきい値電圧を最適な値に保持可能な半導体回路を提供すること。またトランジスタのしきい値電圧を制御可能な半導体回路、及びその駆動方法を提供すること。また上記半導体回路を適用した記憶装置、表示装置、及び電子機器を提供すること。

【解決手段】被制御トランジスタのバックゲートに接続されるノードに、ダイオードと第1の容量素子を設け、トランジスタのしきい値電圧が最適になるように所望の電圧を印加可能で且つその電圧を保持することができる構成とし、さらにダイオードに並列に接続された第2の容量素子を設け、当該ノードの電圧を一時的に変化させられる構成とすればよい。

(もっと読む)

半導体装置、表示装置、液晶表示装置、表示モジュール及び電子機器

【課題】トランジスタのしきい値電圧の変動を抑制し、表示パネルに実装するドライバICの接点数を削減し、表示装置の低消費電力化し、表示装置の大型化又は高精細化するための技術を提供する。

【解決手段】劣化しやすいトランジスタのゲート電極に、オンしたトランジスタを介して信号を入力することで、劣化しやすいトランジスタのしきい値電圧のシフト及びオンしたトランジスタのしきい値電圧のシフトを抑制するものである。すなわち、高電位(VDD)がゲート電極に印加されているトランジスタを介して(若しくは抵抗成分を持つ素子を介して)、交流パルスを劣化しやすいトランジスタのゲート電極に加える構成を含んでいる。

(もっと読む)

表示装置、及びその作製方法

【課題】作製工程を削減し、低コストで生産性の良い表示装置を提供する。消費電力が少なく、信頼性の高い表示装置を提供する。

【解決手段】トランジスタの、ゲート電極となる導電層、ゲート絶縁層となる絶縁層、半導体層、およびチャネル保護層となる絶縁層を連続して形成する。ゲート電極(同一層で形成される他の電極または配線を含む)と島状半導体層の形成を、一回のフォトリソグラフィ工程で行う。該フォトリソグラフィ工程と、コンタクトホールを形成するフォトリソグラフィ工程と、ソース電極及びドレイン電極(同一層で形成される他の電極または配線を含む)を形成するフォトリソグラフィ工程と、画素電極(同一層で形成される他の電極または配線を含む)を形成するフォトリソグラフィ工程の、4つのフォトリソグラフィ工程で表示装置を作製する。

(もっと読む)

TFT基板及びその製造方法

【課題】TFT基板及びその製造方法を提供する。

【解決手段】ガラス基板と、横方向のゲートラインと、ネット状のVcom線と、縦方向のデータラインと、を備えるTFT基板であって、前記ネット状のVcom線の各行におけるVcom線は電気的に接続され、Vcom線はVcom線IC接続部を介してIC素子と電気的に接続される。また、データラインの数をNとする場合、前記Vcom線IC接続部の数は0より大きく、且つN+1より小さくなり、隣接する両行Vcom線との間に少なくとも一組の対応するVcom線縦方向電気接続段がある。

(もっと読む)

液晶光学素子

【課題】表面が導電処理されている透明構造体を内包し、対向電極と短絡を起こさない液晶光学素子を提供すること。

【解決手段】一対の基板(2,4)に液晶層(8)を挟持し、一対の基板(2,4)内に凹凸を有する光学構造体(6)を内包し、該光学構造体(6)の液晶層に面する側の表面に導電膜(5)を備えた液晶光学素子において、光学構造体(6)と対向する対向電極(3)における導電膜が、光学構造体(6)の凸部の頂点に対応する位置で除かれており、且つ対向電極(3)には一様の駆動電圧が印加されていることを特徴とする。

(もっと読む)

表示パネルおよびその製造方法、表示装置、ならびに電子機器

【課題】信号線と共通電極との間に形成される配線容量を低く抑えつつ、画素電極を駆動するために必要な電圧も低く抑えることの可能な表示パネルおよびその製造方法と、上記の表示パネルを備えた表示装置および電子機器とを提供する。

【解決手段】ソース線36のうちゲート線35との交差部分以外の部分(部分ソース線36B)と、画素電極24とが互いに異なる面上に形成されている。具体的には、部分ソース線36Bは透光性基板22の表面上に形成されており、画素電極24は絶縁膜23の表面上に形成されている。

(もっと読む)

液晶表示装置

【課題】少ない消費電力で液晶表示パネルを駆動することができる液晶表示装置を提供する。

【解決手段】ソースドライバ内の出力マルチプレクサ27は、新たにラッチ部が1行分のデータを取り込んだときに、D−Aコンバータがソースライン毎に出力した電位と等しい電位を、出力部45からソースラインに出力する。また、その1行とその前の1行の画像データであって、ソースラインに対応する画像データ同士の間で、MSBの排他的論理和を計算しておく。出力部45の端部に設けられた第1のスイッチ41や第2のスイッチ42は、ラッチ部にデータ取り込みを指示する信号、極性制御信号、およびスイッチ自身に対応する列の排他的論理和の結果が所定の条件を満足する場合に、対応するソースラインと第1キャパシタ31または第2キャパシタ32とを接続させる。

(もっと読む)

半導体装置及びその駆動方法

【課題】トランジスタのしきい値電圧の変動を抑制し、表示パネルに実装するドライバI

Cの接点数を削減し、表示装置の低消費電力化を達成し、表示装置の大型化又は高精細化

を達成することを目的とする。

【解決手段】劣化しやすいトランジスタのゲート電極を、第1のスイッチングトランジス

タを介して高電位が供給される配線、及び第2のスイッチングトランジスタを介して低電

位が供給される配線に接続し、第1のスイッチングトランジスタのゲート電極にクロック

信号を入力し、第2のスイッチングトランジスタのゲート電極に反転クロック信号を入力

することで、劣化しやすいトランジスタのゲート電極に高電位、又は低電位を交互に供給

する。

(もっと読む)

21 - 40 / 311

[ Back to top ]