Fターム[2H092QA14]の内容

液晶−電極、アクティブマトリックス (131,435) | 液晶の動作原理 (3,287) | 電界効果型 (3,247) | 永久双極子型 (266) | 反強誘電性型 (103)

Fターム[2H092QA14]に分類される特許

61 - 80 / 103

半導体装置及び半導体装置の作製方法

【課題】安定した電気的特性を有する酸化物半導体を用いた半導体装置を提供することを目的の一つとする。

【解決手段】フッ素や塩素に代表されるハロゲン元素により、酸化物半導体層に含まれる水素や水分(水素原子や、H2Oなど水素原子を含む化合物)などの不純物を、酸化物半導体層より排除し、上記酸化物半導体層中の不純物濃度を低減する。ハロゲン元素は酸化物半導体層と接して設けられるゲート絶縁層及び/又は絶縁層に含ませて形成することができ、またハロゲン元素を含むガス雰囲気下でのプラズマ処理によって酸化物半導体層に付着させてもよい。

(もっと読む)

半導体装置及びその作製方法

【課題】電気特性が良好で信頼性の高いトランジスタをスイッチング素子として用い、信頼性の高い半導体装置を作製することを課題とする。

【解決手段】加熱処理により脱水化または脱水素化され、表面にナノ結晶からなる微結晶群が形成された酸化物半導体層を形成し、酸化物半導体層上に非晶質で透光性のある酸化物導電層を用いてソース電極層及びドレイン電極層を形成し、酸化物半導体層上の酸化物導電層を選択的にエッチングすることで透光性のあるボトムゲート型のトランジスタを形成し、同一基板上に駆動回路部と画素部を設けた信頼性及び表示品質の高い半導体装置を作製する。

(もっと読む)

表示装置

【課題】D/A変換回路の構成を複雑にすることなく、多階調表示を可能とする表示装置を提供する。

【解決手段】外部から入力されるmビットデジタルビデオデータをnビットデジタルビデオデータに変換し、ソースドライバに前記nビットデジタルビデオデータを供給する回路と(m、nは共に2以上の正数、m>n)、を有する表示装置であって、電圧階調と時間階調とを同時に行い、2m-n個のサブフレームによって1フレームの映像を形成することによって表示を行う。

(もっと読む)

半導体装置およびその作製方法

【課題】画素部の開口率を高くしながら、駆動回路部の特性を向上させた半導体装置を提供することを課題とする。または、消費電力の低い半導体装置を提供することを課題とする。または、しきい値電圧を制御できる半導体装置を提供することを課題とする。

【解決手段】絶縁面を有する基板と、基板上に設けられた画素部と、画素部を駆動する駆動回路の少なくとも一部を有し、画素部を構成するトランジスタおよび駆動回路を構成するトランジスタは、トップゲートボトムコンタクト型のトランジスタであって、画素部においては、電極および半導体層が透光性を有し、駆動回路における電極は、画素部のトランジスタが有するいずれの電極よりも低抵抗である半導体装置である。

(もっと読む)

半導体装置およびその作製方法

【課題】開口率の高い半導体装置またはその製造方法を提供する。また、消費電力の低い半導体装置またはその製造方法を提供する。

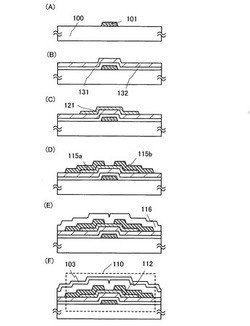

【解決手段】第1の薄膜トランジスタを有する画素部と第2の薄膜トランジスタを有する駆動回路を有し、第1の薄膜トランジスタは、ゲート電極層とゲート絶縁層と半導体層とソース電極層及びドレイン電極層を有し、第1の薄膜トランジスタのゲート電極層、ゲート絶縁層、半導体層、ソース電極層、ドレイン電極層は透光性を有し、第2の薄膜トランジスタのゲート電極層は、第1の薄膜トランジスタのゲート電極層と材料が異なり、第1の薄膜トランジスタのゲート電極層よりも低抵抗の導電層を有し、第2の薄膜トランジスタのソース電極層及びドレイン電極層は、第1の薄膜トランジスタのソース電極層及びドレイン電極層と材料が異なり、第1の薄膜トランジスタのソース電極層及びドレイン電極層よりも低抵抗の導電層を有する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

半導体装置およびその作製方法

【課題】寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。また、駆動回路に用いる薄膜トランジスタの動作速度の高速化を図ることを課題の一とする。

【解決手段】酸化物絶縁層がチャネル形成領域において酸化物半導体層と接したボトムゲート構造の薄膜トランジスタにおいて、ソース電極層及びドレイン電極層がゲート電極層と重ならないように形成することにより、ソース電極層及びドレイン電極層とゲート電極層との間の距離を大きくし、寄生容量の低減を図ることができる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に駆動回路部と、表示部(画素部ともいう)とを有し、当該駆動回路部は、ソース電極及びドレイン電極が金属によって構成され且つチャネル層が酸化物半導体によって構成された駆動回路用チャネルエッチ型薄膜トランジスタと、金属によって構成された駆動回路用配線とを有し、当該表示部は、ソース電極層及びドレイン電極層が酸化物導電体によって構成され且つ半導体層が酸化物半導体によって構成された画素用チャネル保護型薄膜トランジスタと、酸化物導電体によって構成された表示部用配線とを有する半導体装置である。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】半導体装置の開口率を向上することを課題の一とする。

【解決手段】同一基板上に第1の薄膜トランジスタを有する画素部と第2の薄膜トランジスタを有する駆動回路を有し、画素部の薄膜トランジスタは、ゲート電極層、ゲート絶縁層、膜厚の薄い領域を周縁に有する酸化物半導体層、酸化物半導体層の一部と接する酸化物絶縁層、ソース電極層及びドレイン電極層、及び画素電極層とを有し、第1の薄膜トランジスタのゲート電極層、ゲート絶縁層、酸化物半導体層、ソース電極層、ドレイン電極層、酸化物絶縁層、及び画素電極層は透光性を有し、駆動回路部の薄膜トランジスタのソース電極層及びドレイン電極層は、保護絶縁層で覆われ、画素部のソース電極層及びドレイン電極層よりも低抵抗の導電材料である半導体装置を提供する。

(もっと読む)

半導体装置

【課題】各種回路に配置される薄膜トランジスタの構造を、回路の機能に応じて適切なものとすることにより、半導体装置の動作特性および信頼性を向上させ、かつ、低消費電力化を図ると共に、工程数を削減して製造コストの低減および歩留まりの向上を実現することを目的とする。

【解決手段】薄膜トランジスタのLDD領域を、テーパー部を有するゲート電極及びテーパー部を有するゲート絶縁膜に対応させて設ける。具体的には、第1のLDD領域はゲート電極のテーパー部の下に設けられ、第2のLDD領域はゲート絶縁膜のテーパー部の下に設けられる。

(もっと読む)

半導体装置の作製方法

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置を作製し、提供することを課題の一とする。

【解決手段】チャネル形成領域を含む半導体層を酸化物半導体膜とする薄膜トランジスタを有する半導体装置の作製方法において、酸化物半導体膜前にゲート絶縁層内に存在する水分などの不純物を低減した後、酸化物半導体膜の純度を高め、不純物である水分などを低減する加熱処理(脱水化または脱水素化のための加熱処理)を行った後、酸素雰囲気下において徐冷する。ゲート絶縁層中、及び酸化物半導体膜中に加え、上下に接して設けられる膜と酸化物半導体膜の界面に存在する水分などの不純物を低減する。

(もっと読む)

表示装置およびその作製方法

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有するICチップをボンディング等により実装することが困難となり、製造コストが増大するという問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、画素部に酸化物半導体を用いた薄膜トランジスタを用い、さらに駆動回路の少なくとも一部の回路も酸化物半導体を用いた薄膜トランジスタで構成する。同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

半導体装置の作製方法

【課題】安定した電気特性を有する薄膜トランジスタを有する、信頼性のよい半導体装置を提供することを課題の一とする。また、高信頼性の半導体装置を低コストで生産性よく作製することを課題の一とする。

【解決手段】チャネル形成領域を含む半導体層、ソース領域及びドレイン領域を酸化物半導体層とする薄膜トランジスタを有する半導体装置の作製方法において、酸化物半導体層の純度を高め、不純物である水分などを低減する加熱処理(脱水化または脱水素化のための加熱処理)を行う。かつ、加熱処理を行った酸化物半導体層を酸素雰囲気下で徐冷する。

(もっと読む)

液晶表示装置及び電子機器

【課題】高画質な液晶表示装置を提供する。

【解決手段】第1のフレーム期間中に、第1の映像信号が、第1の画素電極に供給され、第2のフレーム期間中に、第1の映像信号と逆の極性の第2の映像信号が、第1の画素に供給され、第1のフレーム期間中に、第1の映像信号と同じ極性の第3の映像信号が、第2の画素電極に供給され、第2のフレーム期間中に、第1の映像信号と逆の極性の第4の映像信号が、第2の画素電極に供給され、第1のフレーム期間中に、第1の映像信号と同じ極性の第5の映像信号が、第3の画素電極に供給され、第2のフレーム期間中に、第1の映像信号と逆の極性の第6の映像信号が、第3の画素に供給され、第1のフレーム期間中に、第1の映像信号と同じ極性の第7の映像信号が、第4の画素電極に供給され、第2のフレーム期間中に、第1の映像信号と逆の極性の第8の映像信号が、第4の画素電極に供給され、120Hzで駆動される。

(もっと読む)

液晶表示パネル及びタッチパネル

【課題】X座標検出電極とY座標検出電極の配置部に隣接する画素電極に対応する画素の開口率低下を少なくする。

【解決手段】画素電極5と画素TFT6と走査線14及び信号線15を設けた基板3に、各画素電極5と信号線15との間に信号線15と平行に形成された複数のX座標検出ライン19と、各画素電極5と走査線14との間に走査線14に平行に形成された複数のY座標検出ライン20と、Y座標検出ライン20上に絶縁膜を介して形成され、一方が絶縁膜に設けられた第1コンタクト孔29においてX座標検出ライン19に接続され、他方が絶縁膜に設けられた第2コンタクト孔30においてY座標検出ライン20に接続された複数のX座標検出電極及25びY座標検出電極26とを設け、他方の基板に設けられた対向電極に、この基板の外面側からのタッチによる撓み変形によってX座標検出電極25とY座標検出電極26の両方に接触する接点部を設けた。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層の上に、酸化物半導体層より導電率の高いバッファ層を形成し、該バッファ層の上にソース電極層及びドレイン電極層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

液晶表示装置およびその作製方法

【課題】ブルー相を呈する液晶を用い、新規な構成を有する液晶表示装置及びその作製方法を提供する。

【解決手段】同一基板上に、複数の構造体(リブ、突起、凸部とも呼ぶ)を形成し、その上に画素電極とその画素電極に対応する電極(固定電位の共通電極)を形成する。画素電極に傾斜をつけ、その画素電極に対応する電極にも傾斜をつけることにより、ブルー相を呈する液晶層に電界をかける構造とする。隣り合う構造体の間隔を狭くすることにより、液晶層に強い電界を印加することができ、液晶を駆動させるための消費電力を少なくすることができる。

(もっと読む)

半導体装置及びその作製方法

【課題】アクティブマトリクス型の表示装置においては、回路を構成する薄膜トランジスタの電気特性が重要であり、この電気特性が表示装置の性能を左右する。従って、逆スタガ型の薄膜トランジスタに水素を徹底的に排除した酸化物半導体膜を用い、電気特性のバラツキを低減する。

【解決手段】課題を解決するため、大気に触れることなくゲート絶縁膜と、酸化物半導体層と、チャネル保護膜との三層をスパッタ法により連続成膜を行う。また、酸化物半導体層の成膜は、酸素が流量比で50%以上100%以下含まれる雰囲気中で行う。また、酸化物半導体層のチャネル形成領域の上層及び下層が、窒素含有量が3原子%以上30原子%以下の酸化窒化珪素膜であることを特徴的な構造とする。

(もっと読む)

半導体装置

【課題】ゲート配線として耐熱性の導電性材料であるタングステン層を用いた場合に、タングステン層の比抵抗を低くすることによって、配線抵抗を十分に低減することを目的とする。

【解決手段】半導体層と、ゲート配線と、前記半導体層と前記ゲート配線との間に挟まれたゲート絶縁層とを有し、前記ゲート配線はタングステン層を有し、前記タングステン層中の酸素濃度を30ppm以下とすることによって、配線抵抗を十分に低減することができる。

(もっと読む)

半導体装置

【課題】開口率の高い半導体装置又はその作製方法を提供することを目的の一とする。また、消費電力の低い半導体装置又はその作製方法を提供することを目的の一とする。

【解決手段】絶縁表面を有する基板上に設けられた半導体層と、半導体層を覆うゲート絶縁膜と、ゲート絶縁膜上に設けられた第1の導電層と第2の導電層とで積層されたゲート電極を含むゲート配線と、半導体層と前記ゲート電極を含む前記ゲート配線を覆う絶縁膜と、絶縁膜上に設けられ、半導体層と電気的に接続され、第3の導電層と第4の導電層とで積層されたソース電極を含むソース配線と、を有し、ゲート電極は、第1の導電層で形成され、ゲート配線は、第1の導電層と第2の導電層で形成され、ソース電極は、第3の導電層で形成され、ソース配線は、第3の導電層と第4の導電層で形成されている。

(もっと読む)

61 - 80 / 103

[ Back to top ]