Fターム[2H093NC15]の内容

Fターム[2H093NC15]に分類される特許

1 - 20 / 215

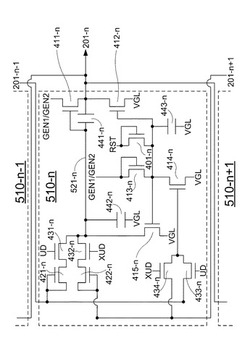

スキャナー、電気光学パネル、電気光学表示装置及び電子機器

【課題】双方向転送機能を有したスキャナーで信号数を削減するとともに出力電位を安定化させる。

【解決手段】同一導電型のトランジスターで構成された複数の単位回路510からなる双方向転送可能なスキャナーであって、前記スキャナーを構成する前記単位回路510は、外部から与えられる信号を選択的に出力端子に出力する出力トランジスターを有し、前記出力トランジスターのゲート電極は第1の方向スイッチを介して他の単位回路510の出力端子である第1の端子に電気的に接続され、前記出力トランジスターのゲート電極は第2の方向スイッチを介してさらに他の単位回路510の出力端子である第2の端子にも電気的に接続される。

(もっと読む)

表示装置および駆動装置

【課題】画像信号線駆動回路の消費電力を削減可能な表示装置等を提供する。

【解決手段】液晶表示装置は複数の画像信号線駆動回路を含んでいる。複数の画像信号線駆動回路のそれぞれは、タイミングコントローラ310と、画像データ抽出回路350と、画像データ抽出回路350によって抽出された画像データをラッチするデータラッチ回路360とを含んでいる。画像データ抽出回路350は、画像データRGBdataのうちから、その画像信号線駆動回路に対して予め割り当てられた所定数の画像信号線に対応する部分のデータを抽出する。画像データ抽出回路350は、画像データの抽出期間以外の期間では、一定電位の信号をデータラッチ回路360へ供給する。

(もっと読む)

TFTアレイ・ビルトイン・セルフ検査装置と検査方法

【課題】本発明は、高額な検査装置を使用することなく、製品とした場合にも表示機能の低下を招かず、効率的に検査し得るアクティブマトリックス型基板と、該検査方法を提供することを目的とする。

【解決手段】

アクティブマトリックス型基板において、複数のデータ線の一方の端にデータ線毎に検査用の検査用基準画素を作成し、検査用基準画素の出力と各データ線に接続された画素をデータ線を通じて比較する比較器を各データ線毎に設置し、比較器の出力を保持する 保持器兼シフトレジスターを配置し、表示領域の全画素に検査用データを書き込み、検査用基準画素に検査用基準画素用検査データを書き込み、順次表示領域の各画素内のデータと検査用基準画素内のデータとを比較し、比較の結果をシフトレジスタ−に格納し、表示領域の画素に欠陥がある場合には、シフトレジスタ−内のデータをシフトアウトして欠陥の画素を特定する。

(もっと読む)

集積回路装置、電気光学装置及び電子機器

【課題】表示ムラを防止できる集積回路装置、電気光学装置及び電子機器を提供すること。

【解決手段】集積回路装置は、データ線駆動回路200−iと、位置オフセット用レジスター230と、位置オフセット用加算回路210−iと、を含み、マルチプレクスされたデータ信号がデマルチプレクスされることで得られた複数のデータ信号が、1水平走査期間において第1〜第pの画素に供給され、位置オフセット用レジスター230が、位置オフセット用設定値OG1と、位置オフセット用設定値OGpとを少なくとも記憶し、位置オフセット用加算回路210−iが、画像データGD1iに対して、位置オフセット用設定値OG1に基づく位置オフセット補正値を加算する処理と、画像データGDpiに対して、位置オフセット用設定値OGpに基づく位置オフセット補正値を加算する処理とを少なくとも行う。

(もっと読む)

電気光学装置及び電子機器

【課題】表示品位の向上を実現することができる電気光学装置及び電子機器を提供する。

【解決手段】所定本数(RGB)毎にブロック化されたデータ線114を順番に選択すると共に、選択したデータ線114に対して映像信号Videoを供給するスイッチング回路41を有するデータ線選択回路40を備える。そして、有効表示期間にRGBの順でサブ画素への書き込みを行う前の非有効表示期間に、ブロック化されたデータ線114毎に個別に設定されたプリチャージ電圧(Bのサブ画素の階調電圧に相当する電圧)を供給する。

(もっと読む)

電気光学装置及び電子機器

【課題】表示品位の向上を実現することができる電気光学装置及び電子機器を提供する。

【解決手段】所定本数(RGB)毎にブロック化されたデータ線114を所定の順番で選択すると共に、選択したデータ線114に対して映像信号Videoを供給するスイッチング回路41を有するデータ線選択回路40を備える。そして、データ線選択回路40は、1水平走査期間における有効表示期間の前半部分(第2期間)でRGB3色のサブ画素への書き込みを行い、各画素電位を所望の電位に近づけておいた後に、後半部分(第1期間)で再度RGB3色のサブ画素への書き込みを行う。

(もっと読む)

画像表示装置

【課題】例えば、走査信号の伝達遅延又は電圧降下に起因する表示品質の低下の軽減を図ることが可能になる画像表示装置を提供すること。

【解決手段】一つの画素回路列(PRO)に対して、当該画素回路列(PRO)のうちの少なくとも一つの画素回路(P)に接続され、かつ、他の画素回路列(PRO)の画素回路(P)には接続されないデータ信号線(DTLo,DTLe)が複数配線される。画素回路列(PRO)の画素回路(P)は、複数のデータ信号線(DTLo,DTLe)のうちのいずれかに接続される。

(もっと読む)

表示装置

【課題】走査信号線の本数を大幅には増大させずにデータ信号線の本数を削減する。

【解決手段】走査信号線G(3)とデータ信号線S(1)との交点に配置された画素電極E(1,3,g)と、データ信号線S(1)に供給される階調信号が画素電極E(1,3,g)を介して印加される画素電極E(1,2,r)と、階調信号が画素電極E(1,3,g)と画素電極E(1,2,r)とを介して印加される画素電極E(1,1,b)と、画素電極E(1,3,g)のトランジスタT(1,3,g)と、画素電極E(1,3,g)と画素電極E(1,2,r)との間の導通/非導通を切換えるトランジスタT(1,2,r)と、画素電極E(1,2,r)と画素電極E(1,1,b)との間の導通/非導通を切換えるトランジスタT(1,1,b)を備え、画素電極E(1,3,g)と画素電極E(1,2,r)と画素電極E(1,1,b)とを異なる画素行として配置する。

(もっと読む)

階調電圧生成回路、ドライバ、電気光学装置、及び電子機器

【課題】階調電圧を供給する際の低電位側の階調電圧の到達時間を短縮する。

【解決手段】ラダー抵抗回路112と、ラダー抵抗回路からの複数の分割電圧をサンプリングしてホールドする複数の階調電圧生成用サンプルホールド回路を有し、ホールドした複数の分割電圧を複数の階調電圧として出力するサンプルホールド部114とを含む階調電圧生成回路110であって、各階調電圧生成用サンプルホールド回路SH1〜SH32は、差動部と出力部を有する演算増幅器OPS1を含み、演算増幅器の出力部は、高電位側電源VDDと演算増幅器の出力ノードNSH1との間に設けられ、そのゲートが差動部の出力により制御される駆動トランジスタTS6と、出力ノードと低電位側電源VSSとの間に設けられ、階調電圧生成用サンプリング期間から階調電圧生成用ホールド期間への移行の際に、流れる電流が増加する低電位側トランジスタ部TSUを含む。

(もっと読む)

表示装置

【課題】画像信号を確実に書き込み可能な表示装置を提供する。

【解決手段】第1プリチャージ用電源10a〜第3プリチャージ用電源10cに蓄積されたいずれかのプリチャージ用電位を、表示する画像の階調に基づいて第1選択スイッチ30a及び第2選択スイッチ30bで選択し、信号線S1及び信号線S2にプリチャージする。

(もっと読む)

表示装置

【課題】各表示画素毎にメモリ部を配置した表示装置において、各表示画素のメモリ部に記憶されたデータ値を読み出す。

【解決手段】複数の表示画素と、前記表示画素に映像データを入力する映像線とを有する表示パネルを備え、前記表示画素は、前記映像データを記憶するメモリ部を有し、前記メモリ部は、入力端子が第1のノードに接続され、出力端子が第2のノードに接続される第1のインバータ回路と、入力端子が前記第2のノードに接続され、出力端子が前記第1のノードに接続される第2のインバータ回路とで構成され、前記表示画素は、前記第2のインバータ回路の前記出力端子と前記映像線との間に接続される第1トランジスタと、前記第1のノードと前記映像線との間に接続される第2トランジスタを有し、前記映像データの読み出し時に、前記第2トランジスタはオフ、前記第1トランジスタはオンとなり、前記メモリ部に記憶された前記映像データを前記映像線に出力する。

(もっと読む)

駆動回路および表示装置

【課題】充放電電流の高調波成分に起因するEMIノイズを小さくする。

【解決手段】ソースドライバ10は、液晶パネルを駆動する出力端子(OUTn)と、映像信号を増幅するアンプ15と、アンプ15の出力と出力端子間に接続される出力スイッチ回路17と、出力スイッチ回路17のスイッチング動作を制御する出力スイッチインピーダンス制御回路16と、を備える。出力スイッチインピーダンス制御回路16は、出力スイッチ回路17のスイッチング動作においてオン状態とする場合に出力スイッチ回路17のインピーダンスを順次低下させるように制御する。

(もっと読む)

表示装置

【課題】第1の観察領域に第1画像を提供し、第2の観察領域に第2画像を提供する表意装置における表示品質の低下を抑制する。

【解決手段】表示パネル10には、複数の走査線12と複数のデータ線14との各交差に対応して配置される複数の電気光学素子Eが配置され、複数の電気光学素子Eは第1画像GAを表示する複数の第1画像表示用素子E1と、第2画像GBを表示する第2画像表示用素子E2とからなる。複数の走査線12の各々には、第1画像表示用素子E1と第2画像表示用素子E2とが共通に接続される。そして、第1画像GAの表示に必要な第1画像表示用素子E1が駆動されるとともに各第2画像表示用素子E2の少なくとも一部が駆動されない第1期間と、第2画像GBの表示に必要な第2画像表示用素子E2が駆動されるとともに各第1画像表示用素子E1の少なくとも一部が駆動されない第2期間とが繰り返されるように、各素子の駆動が制御される。

(もっと読む)

電気光学装置及び電子機器

【課題】液晶装置等の電気光学装置において、短板式で高品位のカラー表示を行い、高精細化を図る。

【解決手段】電気光学装置は、基板(10)上に、複数の走査線(11)及びデータ線(6)と、R、G又はBに対応する複数のサブ画素部(70)と、一列に配列された三つのサンプリング回路(71)が、複数配列されてなるサンプリング手段とを備える。サンプリング回路は、薄膜トランジスタから構成されると共に、ゲート電極(72)を共用で有し、ソース又はドレインに電気的に接続されている画像信号線は、ゲート電極と重畳部分を含む。

(もっと読む)

液晶表示装置および液晶駆動方法

【課題】PVA液晶モードにおいて、オーバードライブ駆動を行なうと生じる揺戻し現象を起因とする動画応答特性の低下を改善する。

【解決手段】画素セルは、高階調側の表示を担当する高階調側のサブ画素と低階調側の表示を担当する低階調側のサブ画素に分割され、各サブ画素を独立に駆動する個別の薄膜トランジスタを具備した多分割ドメイン制御技術を採用して視野角改善を図る。高階調側のサブ画素に対するオーバードライブ駆動特性と低階調側のサブ画素に対するオーバードライブ駆動特性とを独立に設定するルックアップテーブルを設ける。高階調側のサブ画素に対するオーバードライブ駆動特性と低階調側のサブ画素に対するオーバードライブ駆動特性の少なくとも一方を過剰気味のオーバードライブ量に設定することで、揺戻し現象を起因とする動画応答特性の低下を改善する。

(もっと読む)

表示制御装置および方法、並びにプログラム

【課題】バックライトからの光の輝度不足による画質の劣化を防止する。

【解決手段】バックライト輝度算出部121は、表示画像の画像信号に基づいて、バックライトに射出させる光のバックライト輝度を求める。動画像判定部122は、画像信号に基づいて、表示画像が動画像か否かを判定する。補正値算出部123は、表示画像が動画像である場合、前回の補正値を所定の値だけ増加させて新たな補正値とし、表示画像が静止画像である場合、前回の補正値を所定の値だけ減少させて新たな補正値とする。加算部124は、バックライト輝度に補正値を加算して、バックライト輝度を補正する。本発明は、液晶表示装置に適用することができる。

(もっと読む)

コントローラ、ホールド型表示装置、電子機器、ホールド型表示装置の信号調整方法

【課題】動画尾引きの発生を抑制しつつ、輝度効率が良好であるホールド型表示装置を提供する。

【解決手段】本発明に係るコントローラ10は、ホールド型画像表示パネル13に出力する信号を調整するコントローラであって、入力される映像信号の1フレームを複数のサブフレームに分割する倍速駆動変換部21と、複数のサブフレームを含む3原色の映像信号を3原色と混色とを含む4色以上の映像信号に変換する色変換部22と、色変換部によって変換された映像信号を、異なる複数の階調を含み、複数の階調の輝度の平均値が色変換部で変換された映像信号の輝度と同等となる複数の階調に変換し、複数の階調のそれぞれを複数のサブフレームのそれぞれの階調とするサブフレーム変換部23とを有する。

(もっと読む)

電気光学装置の駆動回路及びその駆動方法

【課題】例えば、プロジェクタが使用される使用環境に応じて、適切な輝度で画像を表示する。

【解決手段】輝度調整期間Fcは、1フィールドFの最初に到来する期間であり、当該1フィールドFの期間に表示部100に表示される画像の輝度を概ね規定するために設けられた期間である。変換回路510によって特定された特定信号Sg1が、輝度調整期間Fcにおいて表示部100に供給されることによって、画素部に黒表示が表示される。輝度調整期間Fcは、特定信号Sg1を表示部100に入力する入力期間Fc1と、特定信号Sg1に応じて画素部に黒表示が維持される維持期間Fc2とから構成されている。このように輝度調整期間Fcに画素部72に黒表示を行わせることによって、1フィールドFにおいて表示部に表示される画像の輝度のバックグラウンドを低輝度側にシフトさせることができ、画像の輝度を低下させることが可能である。

(もっと読む)

表示装置

【課題】画像の表示品位が損なわれるのを抑制することが可能な表示装置を提供する。

【解決手段】この液晶表示装置100は、クロック信号に基づいて、画素1aに映像信号

を書き込むためのサンプリングパルスを順次生成する複数のシフトレジスタ部4cを備え

、シフトレジスタ部4cは、それぞれ、2つのシフトレジスタ4fおよび4gを含み、シ

フトレジスタ部4c毎に1つのサンプリングパルスが生成されるとともに、クロック信号

の立ち上がりおよび立ち下がりのうちの予め設定されたいずれか一方に基づいて略全ての

サンプリングパルスが生成されるように構成されている。

(もっと読む)

電気光学装置、その駆動方法および電子機器

【課題】画像信号線106に画像信号dを供給する制御回路40の負荷を抑制する。

【解決手段】所定の本数毎に複数のブロックBに分けられた複数のデータ線104に対応して配置される複数の画素回路Pと、各ブロックBを単位期間Tごとに順次選択する選択回路50と、ブロックBを構成するデータ線104の各々に対応して設けられ、第1のブロック群BL1に対応する第1部分108と第2のブロック群BL2に対応する第2部分110とを各々が有する複数の画像信号線106と、複数の画像信号線106の各々に対応して設けられて当該画像信号線106の第1部分108と第2部分110との間に介在するバッファ回路112と、各データ線104に対応して設けられるとともに、選択されたブロックBに属するデータ線104に対して、画像信号線106に供給された画像信号dをサンプリングするサンプリングスイッチと、を具備する。

(もっと読む)

1 - 20 / 215

[ Back to top ]