Fターム[4M104DD50]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | 選択成長 (331) | 電極孔内のエピタキシー(凸部形成) (109)

Fターム[4M104DD50]に分類される特許

61 - 80 / 109

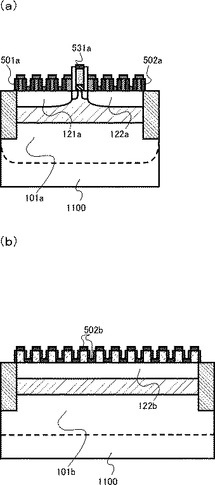

半導体装置の製造方法および半導体装置

【課題】浅いソース、ドレイン接合位置を保ちつつ、ソース、ドレインがシリサイド化され、かつ、接合リークが低く抑えられた半導体装置の製造方法および半導体装置を提供する。

【解決手段】MISFET(金属絶縁物半導体電界効果トランジスタ)を有する半導体装置の製造方法であって、シリコン基板1100の表面に、このMISFETのゲート絶縁膜を形成し、このゲート絶縁膜上にゲート電極を形成し、このゲート電極の両側に、{110}面方位を有するシリコン面上に設けられ、このシリコン面上の<100>方向に垂直な長辺と、この<100>方向に平行で幅が0.5μm以下の短辺からなる矩形状を呈し、MISFETのソース、ドレイン領域の一部を構成する複数のニッケルシリサイド(NiSi)領域501a、502aを形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】チャネル領域に歪みを有するMIS型電界効果トランジスタに関し、低抵抗な接合界面を実現する半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体基板100上にゲート絶縁膜101を介してゲート電極102を形成するステップと、ゲート電極102の両側の、半導体基板中または基板上に、不純物濃度が5×1019atoms/cm3以上1021atoms/cm3以下のp型の高濃度不純物層108を形成するステップと、高濃度不純物層108に圧縮歪みがかかっている状態で、高濃度不純物層108を金属と反応させシリサイド化するステップを有することを特徴とする半導体装置の製造方法およびその製造方法によって形成される半導体装置。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】チャネル領域に応力を印加しつつ、シリサイド層を安定した膜厚で形成する半導体装置の製造方法および半導体装置を提供する。

【解決手段】まず、Si基板11上にゲート絶縁膜13を介してゲート電極14を形成する。次に、ゲート電極14をマスクにしたエッチングにより、Si基板11の表面層を掘り下げる。次いで、掘り下げられたSi基板11の表面に、SiGe層からなる第1の層21aをエピタキシャル成長させる。続いて、第1の層21a上に、第1の層21aよりもGe濃度の低いSiGe層またはSi層からなる第2の層21bをエピタキシャル成長させる。次いで、第2の層21b上に、第2の層21bよりもGe濃度の高いSiGe層からなる第3の層21cをエピタキシャル成長させる。その後の第6工程では、第3の層21cと第2の層21bにシリサイド層22を形成することを特徴とする半導体装置の製造方法および半導体装置である。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】混晶層中のGe濃度およびC濃度の許容範囲内で、チャネル領域に十分に応力を印加することが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】Si基板1上にダミーゲート電極3を形成する。次に、ダミーゲート電極3をマスクにしたリセスエッチングにより、リセス領域7を形成する。次いで、リセス領域7の表面に、SiGe層からなる混晶層8をエピタキシャル成長させる。続いて、ダミーゲート電極3を覆う状態で、混晶層8上に、層間絶縁膜12を形成し、ダミーゲート電極3の表面が露出するまで、層間絶縁膜12を除去する。ダミーゲート電極3を除去することで、層間絶縁膜12にSi基板1を露出する凹部13を形成する。その後、凹部13内にゲート絶縁膜14を介してゲート電極15を形成することを特徴とする半導体装置の製造方法である。

(もっと読む)

半導体装置およびその製造方法

【課題】接合リーク電流の発生を抑えつつ、効果的に歪みシリコン技術の導入を図り得る半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体基板と、前記半導体基板内に形成されて素子形成領域を画定する素子分離領域と、前記素子形成領域における半導体基板の一部の上にゲート絶縁膜を介して形成されたゲート電極と、前記半導体基板の前記ゲート電極の下方に形成されたチャネル領域と、前記チャネル領域と前記素子分離領域との間の素子形成領域にエピタキシャル成長され、前記チャネル領域に歪みを付与する歪み付与層と、前記歪み付与層上に形成されたシリサイド層と、前記素子分離領域近傍で前記シリサイド層と前記半導体基板との間に介在するように、前記素子分離領域に隣接する前記歪み付与層の底面下に形成された前記半導体基板の改質層と、少なくとも前記歪み付与層内および前記素子分離領域近傍の前記改質層内に形成されたソース・ドレイン領域と、を有する。

(もっと読む)

非合金化シリサイドを有する移動度が高められたMOSFETのための構造体及び方法

【課題】 埋設シリコン・ゲルマニウム合金及びシリコン炭素合金は、特に応力エンジニアリングによってMOSFETの移動度を向上させるために、多くの有用な用途を提供するが、これらの表面上の合金化シリサイドの形成はデバイス性能を低下させる。

【解決手段】 本発明は、半導体基板上に配置されたそのようなシリコン合金表面上に非合金化シリサイドを設けるための構造体及び方法を提供する。これにより、同じ半導体基板上の埋設SiGeによって移動度が高められたPFET及び埋設Si:Cによって移動度が高められたNFETの両方に対して、低抵抗コンタクトの形成が可能になる。さらに、本発明は、トランジスタ・デバイスのチャネル上の応力を増大させるために、ゲート誘電体のレベルを上回る厚いエピタキシャル・シリコン合金、特に厚いエピタキシャルSi:C合金についての方法を提供する。

(もっと読む)

チャンネル膜を有する半導体装置の製造方法

【課題】 結晶欠陥が小さくかつ表面粗さの特性が良好なチャンネル膜を有する半導体装置の製造方法を提供する。

【解決手段】 チャンネル膜を有する半導体装置の製造方法は、チャンネルシリコン膜を形成するために、まず単結晶シリコン基板100上に、上部表面から延長して突出した部位を含む第1単結晶シリコン膜110を形成する。第1単結晶シリコン膜110の上部表面に犠牲膜112を形成する。第1単結晶シリコン膜110の前記突出した部位及び犠牲膜112の一部が除去されるように第1単結晶シリコン膜110及び犠牲膜112を1次研磨して第2単結晶シリコン膜及び犠牲膜パターンを形成する。前記犠牲膜パターンを除去し、前記第2単結晶シリコン膜を研磨してチャンネルシリコン膜を形成する。前記工程によると、単結晶シリコン膜の研磨厚さを減少させることができ、チャンネルシリコン膜は表面粗さの特性が良好であり、厚さが平坦となる。

(もっと読む)

半導体装置

【課題】エピタキシャル半導体層をチャネル領域から遠ざけることなく、エピタキシャル半導体層上に形成されるサリサイド膜と、ソース/ドレイン領域と半導体基板との間に形成される接合とを遠ざけることができる半導体装置を提供する。

【解決手段】素子分離領域12間のシリコン基板11上にはゲート絶縁膜13が形成され、ゲート絶縁膜13上にはゲート電極14が形成されている。素子分離領域12とゲート電極14との間のシリコン基板11に形成されたトレンチ内には、エピタキシャル成長法によりエピタキシャルSiGe層16が形成されている。素子分離領域12側のエピタキシャルSiGe層16にはファセット16Aが形成される。さらに、エピタキシャルSiGe層16上にはシリサイド膜18が形成され、エピタキシャルSiGe層16下のシリコン基板11にはp型半導体領域17が形成されている。

(もっと読む)

半導体装置、半導体装置の製造方法、及びSRAMセル

【課題】 開口部THの形成時におけるサイドウォールの膜減りにより、共通コンタクトの形成部分で配線層から半導体基板のウェル領域に電流漏れが生じるおそれがある。

【解決手段】 第1トランジスタのゲート電極と第2トランジスタの拡散領域とを第1開口部内で接続する第1配線層を備えるSRAMセルであって、第1配線層は、第1開口部内において、第1トランジスタ及び第2トランジスタが形成される半導体基板の主面と離間して形成される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】p型FETにおいて、浅いエクステンション層を維持しながら、接合リークを抑制しつつ、ソース・ドレイン層上にシリサイド層を形成した半導体装置を提供する。

【解決手段】半導体装置は、ゲート2と、エクステンション層4と、ソース・ドレイン層6と、シリサイド層8とを具備する。ゲート2は、n型の半導体基板1上にゲート絶縁膜3を介して設けられている。エクステンション層4は、前記ゲート2の両側面のサイドウォール5下部に設けられ、p型である。ソース・ドレイン層6は、エクステンション層4の外側に接して設けられ、p型である。シリサイド層8は、ソース・ドレイン層8の表面部分に設けられている。エクステンション層4は、エクステンション層4のp型の不純物の拡散を抑制する抑制元素を含む。シリサイド層8は、抑制元素を含まない。

(もっと読む)

半導体装置の製造方法

【課題】ニッケルシリサイドの耐熱性を向上させることが可能な半導体装置の製造方法を提供する。

【解決手段】ゲート領域2、ソース領域4及びドレイン領域5が形成された半導体基板1上にニッケル(またはニッケル合金)6を形成し(図1(A))、第1アニール工程でダイニッケルシリサイド7を形成し(図1(B))、プラズマ処理工程では水素イオンを含有するプラズマにより、水素イオンをダイニッケルシリサイド7またはダイニッケルシリサイド7の下部のゲート領域2、ソース領域4及びドレイン領域5に注入し、第2アニール工程でダイニッケルシリサイド7をニッケルシリサイド8に相変態させる(図1(C))。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】DRAM素子の微細化を進めた場合における、周辺回路側のトランジスタの短チャネル効果を抑制すると共に、コンタクト抵抗を低減することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1と、半導体基板1の表面に形成されたMOSトランジスタTr2と、MOSトランジスタTr2のソース108A及びドレイン108Bにそれぞれ接続されるコンタクトプラグ11Aとを具備してなり、コンタクトプラグ11Aが、ソース108A及びドレイン108B上に形成されて不純物が拡散されたエピタキシャル成長層を含んでなることを特徴とする半導体装置を採用する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】チャネル領域に応力を印加しつつ、シリサイド層を膜状に形成するとともに、シリサイド層の異常成長が抑制された半導体装置の製造方法および半導体装置を提供する。

【解決手段】まず、第1工程では、シリコン基板11上にゲート絶縁膜12を介してゲート電極13を形成する。次に、第2工程では、ゲート電極13をマスクにしたエッチングにより、シリコン基板11の表面層を掘り下げる。次いで、第3工程では、掘り下げられたシリコン基板11の表面に、SiGe層からなる第1の層21をエピタキシャル成長させる。続いて、第4工程では、第1の層21上に、第1の層21よりもGe濃度の低いSiGe層またはSi層からなる第2の層22を形成する。その後の第5工程では、第2の層22の少なくとも表面側をシリサイド化して、シリサイド層Sを形成する。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】隣接するコンタクト層同士の接触を抑えつつ、コンタクト抵抗を低減したコンタクトプラグを形成する。

【解決手段】配線構造14から露出するシリコン基板11の表面に、単結晶シリコン層をエピタキシャル成長し、第1コンタクト層21を形成するステップと、第1コンタクト層21の表面を露出するコンタクトホール24を有する層間絶縁膜23を形成するステップと、コンタクトホール24から露出する第1コンタクト層21の表面に単結晶シリコン層をエピタキシャル成長し、第2コンタクト層25を形成するステップとを有する。

(もっと読む)

半導体装置とその製造方法

【課題】

表面荒れの抑制されたニッケルシリサイドを有する半導体装置、またはその製造方法を提供する。

【解決手段】

半導体装置の製造方法は、シリコン領域又はポリシリコン領域の上に、ニッケルプラチナ合金層を形成する工程と、プラチナが拡散しない温度で、ニッケルプラチナ合金層とシリコン領域又はポリシリコン領域とのシリサイド反応を生じさせ、ニッケルプラチナシリサイド層を形成する1次熱処理を行う工程と、薬液による面荒れを実質的に生じることなく、未反応ニッケルプラチナ合金層を薬液でウォッシュアウトする工程と、ニッケルプラチナシリサイド層をニッケルプラチナモノシリサイド層に変換する2次熱処理を行う工程と、を含む。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置において隣接するポリシリコンパッド間のショートを防止する技術を提供する。

【解決手段】半導体装置の製造方法は、(a)第1絶縁膜13を介して下面を基板1表面に接するサイドウォール12、13、14を備えるゲート21を、基板1上に形成する工程と、(b)ゲート21間において、基板1内の拡散領域41上にエピタキシャル膜31を形成する工程と、(c)拡散領域41間に隣接する素子分離領域上に第2絶縁膜32、33を形成する工程と、(d)拡散領域41のエピタキシャル膜31上にコンタクトプラグ11を形成する工程とを具備する。(c)工程は、(c1)第2絶縁膜32、33の膜厚が第1絶縁膜13よりも厚くなるように第2絶縁膜32、33を形成する工程を備えていても良い。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の不具合を抑制しながらキャリアの移動度を高くすることができる半導体装置及びその製造方法を提供する。

【解決手段】溝8内にp型のSiGe混晶層49aがエピタキシャル成長法により形成され、その上にp型のSiGe混晶層49bがエピタキシャル成長法により形成されている。更に、SiGe混晶層49b上にp型のSiGe混晶層49cがエピタキシャル成長法により形成されている。なお、SiGe混晶層49aの最表面の溝8の底からの高さa4は、シリコン基板1の表面を基準としたときの溝8の深さよりも低い。また、SiGe混晶層49bの最表面の溝8の底からの高さb4は、シリコン基板1の表面を基準としたときの溝8の深さよりも高い。更に、SiGe混晶層49a及び49c中のGe濃度は、SiGe混晶層49b中のGe濃度より低い。

(もっと読む)

半導体装置及びその製造方法

【課題】接触抵抗の低減されたポリシリコンプラグを有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上の絶縁層に形成されたホール中に、ポリシリコンプラグが埋めこまれた構造を有する半導体装置の製造方法において、半導体基板上の絶縁層にホールを形成する工程と、前記ホールを埋めるようにポリシリコンを形成させるポリシリコン形成工程と、前記ポリシリコンを、水素雰囲気下で加熱する水素ベーク工程と、を具備する。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル領域の裏面側に応力膜を形成することでチャネル領域に歪みを導入し易くして、MOSFETのオン電流を向上するとともに、短チャネル効果の抑制を可能とする。

【解決手段】チャネル層12上にゲート絶縁膜14を介してゲート電極15を備えた半導体装置1であって、前記チャネル層12の下部に前記チャネル層12を歪ませる応力を有する応力膜13が形成されているものであり、応力膜13は、PMOSFETの場合には膜中に引張応力が内在する引張応力膜で形成され、NMOSFETの場合には膜中に圧縮応力が内在する圧縮応力膜で形成されていることを特徴とする。

(もっと読む)

61 - 80 / 109

[ Back to top ]