Fターム[4M104DD65]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | エッチング (3,048) | ドライエッチ (1,225)

Fターム[4M104DD65]の下位に属するFターム

異方性の利用 (241)

選択比向上用ガス組成 (37)

Fターム[4M104DD65]に分類される特許

941 - 947 / 947

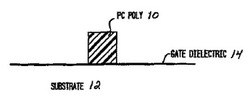

有機反射防止膜(ARC)を有する半導体装置及びその方法

半導体装置(10)の製造において、エッチングされる導電性材料(16)上のパターニング積層部は、下層にあるオルトケイ酸テトラエチル(TEOS)層(20)のパターニングに用いられるパターニングフォトレジスト層(22)を有している。TEOS層(20)は、従来より低い温度で成膜される。低温TEOS層(20)は、有機反射防止膜(ARC)(18)上に設けられ、有機反射防止膜は、導電層(16)上に設けられる。低温TEOS層(20)は、有機ARC(18)とフォトレジスト(22)との間の接着を提供し、低い欠陥性を有し、ハードマスクとして機能し、有機ARC(18)と共に望ましくない反射を低減させる位相シフト層として機能する。  (もっと読む)

(もっと読む)

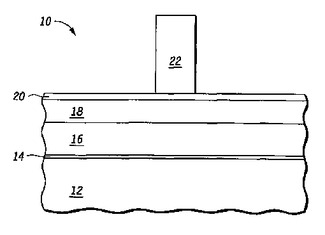

半導体デバイスを製造する方法およびその方法で使用するための装置

本発明は、基板(1)および少なくとも1つの半導体要素を含んだ半導体本体(11)を有した半導体デバイス(10)の製造方法に関する。その方法では、要素の形成後、少なくとも1つの電気的絶縁層(2)または電気的導体層(3)を含んだ層構造が形成され、開口部が、パターン形成されたフォトレジスト層(4)およびエッチング・プロセスの助けによって層構造中に形成され、残渣が、エッチング・プロセス中に半導体本体(11)の表面上に形成され、エッチング・プロセス後に、フォトレジスト層(4)が、酸素含有化合物を使用する処理によって灰にされ、その後、表面が、酸を水で希釈した溶液を含んだ洗浄剤を、室温より高い温度に加熱して使用する洗浄作業を受け、それによって形成された残渣が除去される。本発明によれば、硫酸が、洗浄剤用の酸として選択される。  (もっと読む)

(もっと読む)

個別ゲート構造を備えたトランジスタ

個別ゲート構造(701,703)を備えたトランジスタを形成する方法。これらのゲート構造はそれぞれ、半導体構造(105)の複数の側壁に隣接する。本方法は、ゲート材料層(203)を含む少なくとも一つの共形な層を、チャネル領域を含む半導体基板の上に堆積させることを含む。平坦層(403)がウェハの上に形成される。平坦層は、基板上の所定の位置において少なくとも一つの共形な層の頂部表面よりも低い位置に頂部表面を有する。少なくとも一つの共形な層をエッチングすることにより、半導体構造の上のゲート材料は除去される。  (もっと読む)

(もっと読む)

低GIDLMOSFET構造および製造方法

【課題】 従来のMOSFETデバイスに比べてGIDL電流が小さい低GIDL電流MOSFETデバイス構造を提供する。

【解決手段】 MOSFETデバイス構造は、縁部がソース/ドレイン拡散にわずかに重なる場合(82)がある中央ゲート導体と、薄い絶縁性の拡散バリア層によって中央ゲート導体から分離した側方ウイング・ゲート導体とを含む。また、側方ウイング・ゲート導体の左右の横方向の縁部が、前記ソース拡散領域および前記ドレイン拡散領域の一方に重なる場合(80)も含まれる。

(もっと読む)

配線構造並びにその形成方法及び装置

【課題】 凹部への埋め込み性が良好で、長期に亘り安定した良好な電気的特性を得ることができ、さらに作製工程を可及的に低減し得る配線構造を提供する。

【解決手段】 Cu板と基板3との温度及び温度差を所定通りに制御しつつ、原料ガスであるCl2 ガスのプラズマによりCu板をエッチングすることによりCu成分とCl2 ガスとの前駆体であるCuClを形成し、この前駆体が基板3に吸着され、その後Cu成分を析出させることによりCuの薄膜を形成する成膜反応と、この成膜反応により形成されたCu膜をCl2 ガスのプラズマでエッチングするエッチング反応とを共存させるとともに、前記成膜反応の速度が前記エッチング反応の速度よりも大きくなるように制御することにより前記凹部3aにその底部から順にCu膜を積層してこの凹部3aにCuを埋め込んだ。

(もっと読む)

微細レジストパターン、微細パターンの形成方法及び半導体装置

【課題】 半導体装置の表面にさらに微細なパターンを形成することができる微細レジストパターン、微細パターンの形成方法及び半導体装置を提供する。

【解決手段】 基板6上に、特定の元素を含む特定のガスに接触して特定の元素と結合し所定のエッチングガスに対する耐性が強化される性質を有するレジスト層9を形成する工程と、レジスト層9に第一の露光10を行い、第一の露光領域9bと第一の非露光領域9aとを形成する工程と、第一の露光領域9bに対して第二の露光11を行い、第二の露光領域9cと第三の露光領域9dとを形成する工程と、レジスト層9を特定のガスにさらして第三の露光領域9dのみを特定の元素と結合させる工程と、第二の露光領域9cと第一の非露光領域9aとをエッチングにより除去し第三の露光領域9eからなるレジストパターンを形成する工程とを備えた。

(もっと読む)

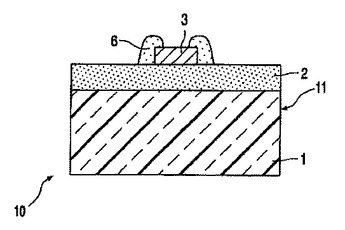

MOSトランジスタ

【課題】 再現性の高い工程を用いて低抵抗のゲート電極を有するGOLD構造を構成できるようにし、それにより、微細化が可能であるとともに信頼性の高いMOSトランジスタを提供する。

【解決手段】 半導体基板1に形成したソース及びドレイン領域10a,10bと、酸化膜3bを介して形成したゲート電極5と、前記ソース及びドレイン領域10a,10bとチャネル形成領域30の間に前記ソース及びドレイン領域10a,10bを取り囲むソース及びドレイン低濃度領域6a’,6b’とを有するMOSトランジスタにおいて、前記酸化膜3bを介して前記ソース及びドレイン低濃度領域6a’,6b’に接する導電性である2つのサイドスペーサ9aと、前記ゲート電極5及び前記サイドスペーサ9a上に形成された導電性薄膜15とを有する。

(もっと読む)

941 - 947 / 947

[ Back to top ]