Fターム[4M104DD66]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極膜のパターニング (4,427) | エッチング (3,048) | ドライエッチ (1,225) | 異方性の利用 (241)

Fターム[4M104DD66]に分類される特許

1 - 20 / 241

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

ポリメタルゲート電極を持つ半導体素子の製造方法

【課題】TiN膜及びバッファ層から形成されるバリアー膜を備えるポリメタルゲート電極を持つ半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に半導体基板側から順に積層された導電性ポリシリコン膜、第1金属シリサイド膜、バリアー膜、及び金属膜から形成されるポリメタルゲート電極と、を備える半導体素子である。バリアー膜は、第1金属シリサイド膜上に形成されるTiN膜と、TiN膜と金属膜との間に介在されるバッファ層と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】電気的特性が良好な半導体装置の製造方法を提供する。

【解決手段】実施形態に係る半導体装置の製造方法は、シリコン基板の上面に、第1方向に延びる複数の凹部を形成する工程と、前記凹部が形成された前記シリコン基板を、弗素又は弗化物を含むガス中でプラズマ処理する工程と、前記プラズマ処理する工程の後で、前記シリコン基板を、水素を含むガス中で熱処理する工程と、前記熱処理する工程の後で、前記凹部の内面上に絶縁膜を形成する工程と、前記絶縁膜上に導電膜を形成する工程と、を備える。

(もっと読む)

半導体装置

【課題】短チャネル効果の抑制およびオフリーク電流の抑制が可能な半導体装置を提供する。

【解決手段】実施形態の半導体装置は、半導体基板において素子分離領域によって仕切られた素子領域と、前記素子領域を横切る所定の方向に沿って前記素子領域の表層に設けられたゲートトレンチにより分離されて前記素子領域の表層に形成されたソース領域およびドレイン領域とを備える。また、実施形態の半導体装置は、少なくとも一部が前記ゲートトレンチ内にゲート絶縁膜を介して埋め込まれて前記ソース領域およびドレイン領域よりも深い位置まで形成されたゲート電極を備える。ドレイン領域における前記ゲート絶縁膜と接触する界面は、前記ゲート電極側に突出した凸部を有する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 寄生抵抗を低減可能な半導体装置を提供する。

【解決手段】 半導体装置は、第1半導体層の表面に沿って延びる突起(2)を有する第1半導体層(1)を含む。ゲート電極(12)は、突起の表面をゲート絶縁膜を挟んで覆う。第2半導体層(28, 45)は、突起のゲート電極により覆われる部分と別の部分の側面上に形成され、溝(31, 52)を有する。ソース/ドレイン領域(30, 46)は、第2半導体層内に形成される。シリサイド膜(33)は、溝内の表面を含め第2半導体層の表面を覆う。導電性のプラグ(37)は、シリサイド膜と接する。

(もっと読む)

半導体装置

【課題】層間絶縁膜のエッチングの際に半導体層がエッチングされることによるコンタク

ト抵抗の増大を防ぎ、書き込み特性及び電荷保持特性に優れた不揮発性半導体記憶装置及

びその作製方法を提供する。

【解決手段】ソース領域又はドレイン領域とソース配線又はドレイン配線との間に導電層

を設ける。また、該導電層は、制御ゲート電極を形成する導電層と同じ導電層からなる。

また、該導電層を覆うように絶縁膜が設けられており、該絶縁膜は該導電層の一部が露出

するコンタクトホールを有する。また、該ソース配線又はドレイン配線は、該コンタクト

ホールを埋めるように形成されている。

(もっと読む)

二層レジストプラズマエッチングの方法

【課題】プラズマエッチング室内において、基板の上に形成された二層レジストをエッチングするための方法を提供する。

【解決手段】二層レジストの第1の層の上にパターンを形成された基板をエッチング室に導入する工程から開始される。次いで、SiCl4ガスがエッチング室に流し込まれる。次に、SiCl4ガスを流し入れつつエッチング室内においてプラズマを発生させる。次いで、二層レジストがエッチングされる。

(もっと読む)

薄膜トランジスタおよびその製造方法、ならびに電子機器

【課題】ソース電極およびドレイン電極と有機半導体層とにおける電荷注入効率の向上と性能の確保とを両立させることが可能な薄膜トランジスタを提供する。

【解決手段】薄膜トランジスタは、エッチングガスと反応可能な金属元素および半金属元素のうちの少なくとも一方を含む金属含有材料により形成された有機半導体層と、互いに離間されたソース電極およびドレイン電極と、有機半導体層とソース電極およびドレイン電極とが重なる領域において有機半導体層とソース電極およびドレイン電極との間に挿入され、エッチングガスと反応可能な金属元素および半金属元素のうちの少なくとも一方を含まない非金属含有材料により形成された有機導電層とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】トレンチの対向する側面上に互いに離間されたゲート電極を有する半導体装置において、微細化に対応することができる半導体装置の製造方法を提供する。

【解決手段】トレンチ4を形成する工程およびゲート絶縁膜6を形成する工程では、トレンチ4のうち第2導電型層3と接する部分を中間部したとき、トレンチ4の対向する側面に形成されたゲート絶縁膜6の間隔において、トレンチ4の開口部に形成されている部分の間隔W1がトレンチ4の中間部に形成されている部分の間隔W2より狭くなるトレンチ4およびゲート絶縁膜6を形成する。そして、導電膜7aを形成する工程では、トレンチ4に導電膜7aで囲まれる空隙14を形成しつつ、導電膜7aを形成する。その後、ゲート電極7を形成する工程では、導電膜7aを異方性エッチングし、空隙14を介してトレンチ4の底面に形成された導電膜7aを除去してゲート電極7を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトホールの一部が素子分離領域上に配置された構造の半導体装置において、短絡及び接合漏れ電流の増大を抑制する。

【解決手段】半導体装置50は、半導体基板10における活性領域10aを取り囲むように形成された溝15bに素子分離絶縁膜15aが埋め込まれた素子分離領域15と、活性領域10aに形成された不純物領域26と、半導体基板10上を覆う層間絶縁膜28と、層間絶縁膜28を貫通し、活性領域10a上及び素子分離領域15上に跨って形成されたコンタクトプラグ34と、少なくともコンタクトプラグ34下方において、不純物領域26上に形成された金属シリサイド膜33とを備える。素子分離領域15は、コンタクトプラグ34の下方において、素子分離絶縁膜15と活性領域10aとの間に設けられた保護絶縁膜35を更に有する。

(もっと読む)

パターン形成方法

【課題】微細なパターンと比較的サイズが大きめのパターンとを有するパターン形成方法で、サイズが大きめのパターンを従来に比して精度良く形成することができるパターン形成方法を提供する。

【解決手段】実施形態によれば、加工対象上の芯材膜31に開口を形成した後、マスク膜32をコンフォーマルに形成する。マスク膜32をエッチバックして芯材膜31の側面に第1の幅のマスク膜32を残す。開口の形成領域以外の領域にレジストパターン35aを形成し、これをマスクに芯材膜31をエッチングする。さらに、芯材膜31をスリミングして第1の幅より小さい第2の幅のラインアンドスペース状のパターンを形成する。側壁膜をコンフォーマルに形成した後、エッチバックし、さらに芯材膜31を除去して、加工対象上に側壁膜からなる側壁パターンを形成する。そして側壁パターンで加工対象をエッチングする。

(もっと読む)

半導体装置及びその製造方法

【課題】本実施形態は、ゲートパターン加工時のアスペクト比を低減することができる半導体装置及びその製造方法を提供する。

【解決手段】本実施形態の半導体装置の製造方法は、基板上に、ゲート絶縁膜と下部ゲート電極と電極間絶縁膜と上部ゲート電極とハードマスクとを順次形成し、選択トランジスタの形成予定領域に、ハードマスクと上部ゲート電極と電極間絶縁膜とを貫き、下部ゲート電極まで達する溝を形成し、溝の中に選択的に下部ゲート電極の結晶構造から影響を受けつつ結晶成長させることにより、特定の結晶配向を優先的に持つ結晶構造を有し、且つ、下部ゲート電極と上部ゲート電極とを電気的に接続する接続層を形成する。

(もっと読む)

配線の形成方法

【課題】側壁転写プロセスを用いて被加工膜を形成する場合に、従来に比して工程数を減少させ、製造コストの上昇を抑えることができる配線の形成方法を提供する。

【解決手段】実施形態によれば、まず、被加工膜11上にマスク膜12と所定の形状のパターンの芯材膜13とを形成し、その上にスペーサ膜14を形成する。ついで、スペーサ膜14を後のエッチング時のマスクとして残す位置から所定の距離の範囲にスペーサ膜14が位置するようにダミーのスペーサ膜143と、芯材膜13の側壁に側壁パターンとをリソグラフィ技術とエッチング技術とを用いて形成する。その後、芯材膜13を除去し、ダミーパターンが除去されるまでスペーサ膜14をエッチングし、所定の範囲に他のスペーサ膜14が存在しない位置にパターン変質部21を生成する。そして、パターン変質部21を除去し、スペーサ膜14をマスクとしてマスク膜12と被加工膜11をエッチングする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】パターンの微細化、特に、SRAMのセル面積を縮小するためには、隣接ゲートの端部間距離を縮小することが重要となる。しかし、28nmテクノロジノードにおいては、ArFによる単一回露光でパターンを転写することは、一般に困難である。従って、通常、複数回の露光、エッチング等を繰り返すことによって、微細パターンを形成しているが、ゲートスタック材にHigh−k絶縁膜やメタル電極部材が使用されているため、酸化耐性やウエットエッチ耐性が低い等の問題がある。

【解決手段】本願発明は、メモリ領域におけるhigh−kゲート絶縁膜およびメタル電極膜を有するゲート積層膜のパターニングにおいて、最初に、第1のレジスト膜を用いて、隣接ゲート電極間切断領域のエッチングを実行し不要になった第1のレジスト膜を除去した後、第2のレジスト膜を用いて、ライン&スペースパターンのエッチングを実行するものである。

(もっと読む)

半導体装置

【課題】しきい値を電気的に調整可能な半導体装置を提供する。

【解決手段】半導体装置10では、チャネル領域14は対向する第1、第2の面14a、14bを有している。第1、第2不純物領域15、16が、チャネル領域14の両側に配設されている。第1ゲート電極18は、第1ゲート絶縁膜19を介して第1の面14aに、第1ゲート電圧Vg1が印加されると生じる第1反転層23の一側が第1不純物領域15に接触し、他側が第2不純物領域16から離間するように配設されている。第2ゲート電極20は、第2ゲート絶縁膜21を介して第2の面14bに、第2ゲート電圧Vg2が印加されると生じる第2反転層24の一側が第2不純物領域16に接触し、他側が第1不純物領域15から離間するように配設されている。第1、第2ゲート電圧Vg1、Vg2に応じて、第1、第2反転層23、24が接触し、第1、第2不純物領域15、16間が導通する。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲート電極および当該選択ゲート電極に隣接する他のゲート電極間の間隔を所望の距離に調整できるようにした不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】複数本のラインパターンのうち選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてマスクした条件にて複数本のラインパターンの側壁面をスリミングし、選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてパターン間膜を埋込むと共にスリミングされたラインパターンの側壁面に沿ってパターン間膜を形成し、選択ゲート電極の形成領域のラインパターンをマスクした条件にて当該ラインパターン以外のラインパターンを除去しマスクされたラインパターンを残留させ、パターン間膜および残留したラインパターンをマスクとして第1膜を異方性エッチングし、第1膜をマスクとして導電膜をエッチングする不揮発性半導体記憶装置の製造方法を提供する。

(もっと読む)

半導体装置の製造方法

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

半導体装置および電力変換装置

【課題】低損失と高耐圧を保持しながら、ターンオンスイッチング期間中におけるdv/dtのゲート駆動回路による制御性を向上できる半導体装置を提供する。

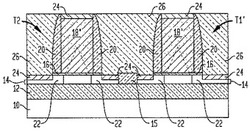

【解決手段】第1導電型の第1半導体層4と、その表面付近に形成された第2導電型の第2半導体層2と、これに電気的に接続する第1主電極11と、第1半導体層4に隣接し第2半導体層2とは逆側の表面付近に形成された第2導電型の第3半導体層6と、この上部に選択的に設けられた第1導電型の第4半導体層7と、第3半導体層6及び第4半導体層7に電気的に接続する第2主電極14と、側面が第4半導体層7と第3半導体層6に接し第1半導体層4に達するトレンチ17と、この側面に沿ってポリシリコンのサイドウオールにより形成されたゲート電極9と、トレンチ17内でゲート電極9から離れて設けられ第2主電極14と電気的に接続するポリシリコン電極18が設けられている。

(もっと読む)

半導体装置、液晶モジュール、電子機器及び配線

【課題】下地に対する選択比が大きく、テーパー形状の配線を形成するドライエッチング

方法を提供する。

【解決手段】基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下の配線を形成

する。また、基板上に導電性材料からなる膜を形成し、ICPエッチング装置を用いて前

記導電性材料からなる膜をドライエッチングして、テーパー角が60°以下のゲート配線

を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート絶縁膜上に活性層を形

成する。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

1 - 20 / 241

[ Back to top ]