ポリメタルゲート電極を持つ半導体素子の製造方法

【課題】TiN膜及びバッファ層から形成されるバリアー膜を備えるポリメタルゲート電極を持つ半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に半導体基板側から順に積層された導電性ポリシリコン膜、第1金属シリサイド膜、バリアー膜、及び金属膜から形成されるポリメタルゲート電極と、を備える半導体素子である。バリアー膜は、第1金属シリサイド膜上に形成されるTiN膜と、TiN膜と金属膜との間に介在されるバッファ層と、を備える。

【解決手段】半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に半導体基板側から順に積層された導電性ポリシリコン膜、第1金属シリサイド膜、バリアー膜、及び金属膜から形成されるポリメタルゲート電極と、を備える半導体素子である。バリアー膜は、第1金属シリサイド膜上に形成されるTiN膜と、TiN膜と金属膜との間に介在されるバッファ層と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体素子及びその製造方法に係り、特にポリメタルゲート電極を持つ半導体素子及びその製造方法に関する。

【背景技術】

【0002】

半導体素子が高集積化されてデザインルールが100nm以下に減少するにつれて、ゲート電極を構成するワードラインのような配線層での抵抗が大きくなって信号遅延が急増しつつある。これにより、低抵抗の配線を具現化するための努力のうち一つとして、半導体基板上に導電性ポリシリコン層、バリアー膜、及び金属膜が順に形成される積層構造を備えるポリメタルゲート電極が提案された。

【0003】

ポリメタルゲート電極を形成するに当って、これまで提案された構造では、バリアー膜として主にWNまたはWSiNを使用した(例えば、特許文献1参照)。しかし、バリアー膜としてWNまたはWSiNを使用する場合、ワードラインの抵抗は低めることができる。しかし、これらの膜は熱に対する安定性が不良であって、後続の高温熱処理工程、例えば、ワードラインパターニングした後にパターニング時に損傷した膜質を復旧するための選択的酸化工程時、約800℃またはそれ以上の高温熱処理によってバリアー膜が局部的に破壊される現象が発生する。その結果、前記導電性ポリシリコン層のSiと前記金属膜の金属とが相互反応して金属シリサイドが形成される現象が発生する。

【0004】

図1A及び図1Bは、ポリメタルゲート構造で、前記バリアー膜としてWNを使用した場合に、熱処理時に発生する問題点を確認した結果を示すSEM(Scanning Electron Microscope)イメージである。

図1Aには、Si基板上にゲート酸化膜(Gox)、ポリシリコン層(Poly−Si)、約50ÅのWNバリアー膜、そして、約400ÅのW膜が形成されている断面構造が示されている。

【0005】

図1Bには、図1Aの構造を約850℃の温度下で約40分間熱処理した結果得られた断面構造が示されている。図1Bで、ポリシリコン層とW膜との間にあるWN膜が熱処理によりW及びNに分解されて局部的に破壊され、ポリシリコン層及びW膜の大部分がタングステンシリサイド化したことが確認できる。

【0006】

したがって、ポリメタルゲート構造でバリアー膜の熱的安定性を改善できる新たな技術が必要である。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】米国特許第6,774,442号明細書

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明の目的は、前記した従来技術での問題点を解決しようとするものであって、高集積化された半導体素子に必要な低抵抗配線を具現化すると同時に熱的に安定した配線構造を持つ半導体素子を提供することである。

本発明の他の目的は、高集積化された半導体素子に必要な低抵抗配線を具現化すると同時に熱的に安定した配線構造を形成できる半導体素子の製造方法を提供することである。

【課題を解決するための手段】

【0009】

前記目的を達成するために、本発明による半導体素子は、半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に前記半導体基板側から順に積層された導電性ポリシリコン膜、第1金属シリサイド膜、バリアー膜、及び金属膜から形成されるポリメタルゲート電極と、を備え、前記バリアー膜は、前記第1金属シリサイド膜上に形成されるTiN膜と、前記TiN膜と前記金属膜との間に介在されるバッファ層と、を備える。

【0010】

前記バッファ層は、Ti、Ta、Zr、Hf及びSiから形成される群から選択される少なくとも一つの物質からなる。または、前記バッファ層は、非晶質の第2金属シリサイド膜から形成される。

【0011】

前記他の目的を達成するために、本発明による半導体素子の製造方法では、半導体基板上に導電性ポリシリコン膜及び第1金属シリサイド膜を順に形成する。前記第1金属シリサイド膜上にTiN膜及びバッファ層で構成されるバリアー膜を形成する。前記バッファ層上に金属膜を形成する。前記導電性ポリシリコン膜、第1金属シリサイド膜、バリアー膜及び金属膜をパターニングしてゲート電極を形成する。

【発明の効果】

【0012】

本発明によれば、ポリメタルゲートのバリアー膜としてTiN膜を使用することによってゲート積層構造の熱安定性を改善でき、バリアー膜として使われるTiN膜と上部の金属膜との間に前記金属膜の粒径を増大させるためのバッファ層を挿入することによって、ワードライン抵抗を低めることができる。このバッファ層として、結晶質の金属膜(例えば、Ti、Ta、Zr、Hf、Siなど)または非晶質の金属シリサイド膜が使われることができる。また、ポリシリコン膜とバリアー膜との間に金属シリサイド膜を挿入することによって、上部の金属膜と下部のポリシリコン膜との界面抵抗を低減させることができる。

【図面の簡単な説明】

【0013】

【図1A】従来技術によるポリメタルゲート構造で、バリアー膜としてWNを使用した場合の熱処理前のSEMイメージである。

【図1B】従来技術によるポリメタルゲート構造で、バリアー膜としてWNを使用した場合の熱処理後のSEMイメージである。

【図2A】本発明の望ましい実施形態による半導体素子の製造方法を説明するために、工程順序によって示す断面図である。

【図2B】本発明の望ましい実施形態による半導体素子の製造方法を説明するために、工程順序によって示す断面図である。

【図2C】本発明の望ましい実施形態による半導体素子の製造方法を説明するために、工程順序によって示す断面図である。

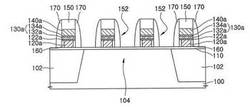

【図2D】本発明の望ましい実施形態による半導体素子の製造方法を説明するために、工程順序によって示す断面図である。

【図3】本発明による半導体素子であるゲート電極のバリアー膜を構成するTiN膜に対して熱に対する安定性を確認した結果を示すSEMイメージである。

【図4】ポリメタルゲート構造で、バリアー膜の構成物質によってゲート電極のW膜での粒径及び比抵抗を評価した例を示すグラフである。

【図5】ポリメタルゲート構造で、バリアー膜の構成物質によってゲート電極のW膜でのシート抵抗を評価した例を示すグラフである。

【図6】ポリメタルゲート構造で、バリアー膜の構造及びタングステンシリサイドコンタクトの存否による金属膜とポリシリコン膜との界面抵抗変化を評価した結果を示すグラフである。

【図7】比較例として示したポリメタルゲート構造での金属膜とポリシリコン膜との界面抵抗変化を評価した結果を示すグラフである。

【発明を実施するための形態】

【0014】

次いで、本発明の望ましい実施形態について添付図面を参照して詳細に説明する。

図2Aないし図2Dは、本発明の望ましい実施形態による半導体素子の製造方法を説明するために、工程順序によって示す断面図である。

【0015】

図2Aを参照すれば、半導体基板100にSTI(Shallow Trench Isolation)方法で素子分離領域102を形成して、前記半導体基板100に活性領域104を画定する。

【0016】

その後、前記半導体基板100上にゲート絶縁膜110を形成する。例えば、前記ゲート絶縁膜110は約50Å厚さの酸化膜から形成されることができる。

前記ゲート絶縁膜110上に導電性ポリシリコン膜120及び第1金属シリサイド膜122を順に形成する。前記導電性ポリシリコン膜120は、約500Å〜1000Åの厚さに形成できる。前記第1金属シリサイド膜122は、約50Åの厚さに形成できる。前記第1金属シリサイド膜122は、形成しようとする配線構造でオームコンタクトを形成するために挿入されたものであって、例えば、タングステン(W)シリサイド膜、モリブデン(Mo)シリサイド膜、チタン(Ti)シリサイド膜、タンタル(Ta)シリサイド膜、ハフニウム(Hf)シリサイド膜、またはコバルト(Co)シリサイド膜の少なくともいずれか一つから形成されることができる。前記第1金属シリサイド膜122は、金属(M)に対するシリコン(Si)の原子比(Si/M)が2.0〜10.0である組成を持つように形成できる。

【0017】

前記第1金属シリサイド膜122上に、TiN膜132及びバッファ層134で構成されるバリアー膜130を形成する。前記TiN膜132及びバッファ層134はそれぞれ形成しようとする配線の設計寸法によってその厚さが変わることができる。例えば、前記TiN膜132は約30Å〜300Åの厚さに形成でき、前記バッファ層134は約10Å〜200Åの厚さに形成できる。また、前記TiN膜132及びバッファ層134は、例えば、PVD(Physical Vapor Deposition:物理蒸着法)、CVD(Chemical Vapor Deposition:化学蒸着法)、またはALD(Atomic Layer Deposition:原子層蒸着法)方法によって形成でき、これら方法のみに制限されるものではない。

【0018】

望ましくは、前記バッファ層134は、結晶質のTi、Ta、Zr、Hf及びSiから形成される群から選択される少なくとも一つの物質から形成されることができる。また望ましくは、前記バッファ層134は、Wシリサイド膜、Moシリサイド膜、Tiシリサイド膜、Taシリサイド膜、Hfシリサイド膜、またはCoシリサイド膜で構成される非晶質の第2金属シリサイド膜から形成されることができる。

【0019】

前記バリアー膜130上に金属膜140を形成する。前記金属膜140は、WまたはMoからなる。

前記バリアー膜130を構成する前記TiN膜132は、その粒径が比較的小さくてその構造が柱状構造をなしているので、その上に直ちに前記金属膜140を形成すれば、金属成長が制限されて前記金属膜140内での金属粒径が小さくなることがある。これは、前記金属膜140のシート抵抗を増大させる結果を招く恐れがある。このような結果を回避するために、本発明では、前記バリアー膜130を前記TiN膜132とそれを覆う前記バッファ層134との積層構造で形成したので、前記バッファ層134上に前記金属膜140が形成される。このような構造では、前記バッファ層134によりその上での金属成長が制限されず、したがって、前記金属膜140の粒径を大きくすることで、シート抵抗を低減させることができる。

【0020】

図2Bを参照すれば、絶縁膜パターン150、例えば、窒化膜パターンを利用して前記導電性ポリシリコン膜120、第1金属シリサイド膜122、バリアー膜130及び金属膜140を異方性ドライエッチング方法によりパターニングして、前記半導体基板100側から導電性ポリシリコン膜パターン120a、第1金属シリサイド膜パターン122a、バリアー膜パターン130a及び金属膜パターン140aが順に積層されたゲート電極152を形成する。前記バリアー膜パターン130aは、TiN膜パターン132aとバッファ層パターン134aとの積層構造で構成される。

【0021】

図2Cを参照すれば、前記ゲート電極152の形成のためのエッチング工程時に損傷したゲート絶縁膜110を復旧するために選択的酸化工程を実施する。前記選択的酸化工程のために、例えば、約700〜1100℃の温度下で熱処理工程を行なうことができる。その結果、前記ゲート電極152中の導電性ポリシリコン膜パターン120aの側壁に酸化膜160が形成され、前記半導体基板100の活性領域104表面が酸化する。

【0022】

図2Dを参照すれば、前記ゲート電極152及びこれを覆っている絶縁膜パターン150をイオン注入マスクとして利用して、前記半導体基板100に低濃度イオン、例えば、N−型またはP−型イオンを注入して前記半導体基板100内にエクステンション領域(図示せず)を形成した後、前記ゲート電極152及び絶縁膜パターン150の側壁に絶縁スペーサ170を形成する。前記絶縁スペーサ170は、例えばシリコン窒化膜から形成される。その後、前記絶縁膜パターン150及び絶縁スペーサ170をイオン注入マスクとして利用して、前記半導体基板100に高濃度イオン、例えば、N+型またはP+型イオンを注入して前記半導体基板100の活性領域104内にソース/ドレーン領域(図示せず)を形成する。

【0023】

図3は、本発明による半導体素子を形成するために、ゲート電極形成のための配線構造内のバリアー膜を構成するTiN膜に対して熱に対する安定性を確認した結果を示すSEMイメージである。

より詳細に説明すれば、図3には、WNバリアー膜の代わりにTiNバリアー膜を形成したことを除いては、図1Aと同じ構造を持つ積層構造について、約850℃で約40分間熱処理した結果得られた断面構造が示されている。図3で、バリアー膜としてTiN膜を適用した場合は、ポリシリコン膜(Poly−Si)とW膜との反応が抑制されて均一なW膜が観察される。これより、TiN膜は熱に対する安定性が比較的優秀であって、高温熱処理後にも破壊されずにバリアー特性を維持することが分かる。

【0024】

ポリメタルゲート構造でバリアー膜の熱に対する安定性を確保するために、熱に対して安定性が立証されたTiN膜をバリアー膜として適用する場合は、TiN膜上に金属膜、例えば、W膜をPVD方法で形成する時にWの粒径が減少する現象が観察される。その結果、WNバリアー膜を使用する場合に比べて、配線ラインでの抵抗が約2倍以上増大して、それを改善する必要がある。

【0025】

図4は、導電性ポリシリコン膜上にW膜が形成されたポリメタルゲート構造で、前記ポリシリコン膜とW膜との間に挿入されるバリアー膜の構成物質によってゲート電極のW膜での粒径及び比抵抗を評価した例を示すグラフである。

【0026】

図4の評価のために、半導体基板側からゲート絶縁膜上にポリシリコン、タングステンシリサイド、バリアー膜、及びW膜を順に形成し、前記バリアー膜としてWNを形成した場合(“W/WN”と表示)、前記バリアー膜として半導体基板側からTiN膜及びTi膜を順に形成した場合(“W/Ti/TiN”と表示)、そして、前記バリアー膜としてTiN膜を形成した場合(“W/TiN”と表示)それぞれに対して、W膜での粒径及び比抵抗を測定した。

【0027】

図4の結果で分かるように、本発明によってバリアー膜としてTiN膜上にTi膜を形成し、その上に前記金属膜としてW膜を形成した場合、Ti膜上に蒸着されるWの粒径が増大して、W膜での比抵抗がW/WN構造でのWの比抵抗である15μΩ・cm〜20μΩ・cmレベルに減少する。

【0028】

図5は、導電性ポリシリコン膜上にW膜が形成されるポリメタルゲート構造で、前記ポリシリコン膜とW膜との間に挿入されるバリアー膜の構成物質によってゲート電極のW膜でのシート抵抗を評価した例を示すグラフである。

図5の評価のために、半導体基板側からゲート絶縁膜上にポリシリコン、タングステンシリサイド、バリアー膜、及びW膜を順に形成し、前記バリアー膜としてWNを形成した場合(“W/WN/WSi/Poly”と表示)、前記バリアー膜として半導体基板側からTiN膜及びタングステンシリサイド膜を順に形成した場合(“W/WSi/TiN/WSi/Poly”と表示)、前記バリアー膜として半導体基板側からTiN膜及びTi膜を順に形成した場合(“W/Ti/TiN/WSi/Poly”と表示)、そして、前記バリアー膜としてTiN膜を形成した場合(“W/TiN/WSi/Poly”と表示)それぞれに対して、W膜でのシート抵抗(Rs)を測定した。

【0029】

図5の結果から分かるように、バリアー膜としてTiN膜のみを形成した場合には、W膜でのRsがWN膜をバリアー膜として使用した場合より約2倍以上増大することが分かる。これは、バリアー膜としてTiN膜のみを形成した場合には、TiN膜の真上に蒸着されるWの粒径がTiNの粒径に影響されて小さくなるためである。

【0030】

一方、本発明のように、バリアー膜としてTiN膜とタングステンシリサイド膜との積層構造、またはTiN膜とTi膜との積層構造を使用した場合には、W膜でのRsがWN膜をバリアー膜として使用した場合とほぼ同等なレベルまで減少した。これは、TiN膜上に結晶質のTi膜または非晶質のタングステンシリサイド膜を形成した結果であって、W膜が非晶質膜上に形成されることによってW膜内での粒径が増大したためである。したがって、本発明による半導体素子では、ポリメタルゲート構造でポリシリコン膜と金属膜との間に挿入されるバリアー膜として、TiN膜と非晶質の金属シリサイド膜、またはTiN膜と結晶質のTi膜との積層構造を使用することによって、前記TiN膜によって熱安定性を確保すると同時に前記バッファ層によって上部金属膜の粒径を大きくして、熱に対して安定した構造及び低抵抗配線を同時に具現化できる。

【0031】

図6は、ポリメタルゲート構造で、バリアー膜の構造及びポリシリコン膜とバリアー膜との間でのタングステンシリサイドコンタクトの存否による、金属膜とポリシリコン膜との界面抵抗変化を評価した結果を示すグラフである。

図6の評価のために、半導体基板側からポリシリコン膜上にWNバリアー膜及びW膜を形成したポリメタルゲート構造(“W/WN/Poly−Si”と表示)と、半導体基板側からポリシリコン膜上にタングステンシリサイド膜、TiN膜及びTi膜が順に積層されたバリアー膜、及びW膜を形成したポリメタルゲート構造(“W/Ti/TiN/WSix/Poly−Si”と表示)を形成し、これら各構造についてW膜とポリシリコン膜との界面抵抗変化を測定した。

【0032】

本発明による構造であるW/Ti/TiN/WSix/Poly−Si構造では、Ti/TiNバリアー膜の下部にタングステンシリサイド膜を挿入することによって、W膜とポリシリコン膜との間にオームコンタクトを形成できるということが分かる。また、TiN膜上に蒸着されたTi膜によりTiN膜とタングステンシリサイド膜との界面の窒化及び酸化が抑制されて、従来構造であるW/WN/Poly−Si構造に比べて、W膜とポリシリコン膜との界面抵抗を約10−3倍以下に低減させることができる。

【0033】

図7は、比較例として示したポリメタルゲート構造での金属膜とポリシリコン膜との界面抵抗変化を評価した結果を示すグラフである。

図7には、半導体基板側からポリシリコン膜上にWNバリアー膜及びW膜を形成したポリメタルゲート構造(“W/WN/Poly−Si”と表示)と、半導体基板側からポリシリコン膜上にタングステンシリサイド膜、WNバリアー膜及びW膜を形成したポリメタルゲート構造(“W/WN/WSix/Poly−Si”と表示)とに対して測定されたW膜とポリシリコン膜との界面抵抗変化が示されている。

【0034】

図7から分かるように、WNバリアー膜を使用するポリメタルゲート構造では、WNの分解によって発生するNによりシリサイドコンタクトを形成すべく挿入されたタングステンシリサイド膜が窒化されて、W膜とポリシリコン膜との界面にオームコンタクトが形成されない。

【0035】

前記した実験結果から分かるように、本発明によれば、ポリメタルゲートのバリアー膜としてTiN膜を使用することによって、ゲート積層構造の熱安定性を改善でき、バリアー膜として使われるTiN膜と上部の金属膜との間に前記金属膜の粒径を増大させるためのバッファ層を挿入することによって、ワードライン抵抗を低めることができる。また、ポリシリコン膜とバリアー膜との間に金属シリサイド膜を挿入することによって、上部の金属膜と下部のポリシリコン膜との界面抵抗を従来の構造に比べて約10−3倍以下に低減させることができる。したがって、100nm以下のデザインルールを持つ高集積半導体素子でパフォーマンスを顕著に改善できる。

【0036】

以上、本発明を望ましい実施形態を挙げて詳細に説明したが、本発明は、前記実施形態に限定されず、本発明の技術的思想及び範囲内で当業者によりいろいろな変形及び変更が可能である。

【産業上の利用可能性】

【0037】

本発明は、半導体素子の関連技術分野に好適に用いられる。

【符号の説明】

【0038】

100 半導体基板

102 素子分離領域

104 活性領域

110 ゲート絶縁膜

120 導電性ポリシリコン膜

120a 導電性ポリシリコン膜パターン

122 第1金属シリサイド膜

122a 第1金属シリサイド膜パターン

130 バリアー膜

130a バリアー膜パターン

132 TiN膜

132a TiN膜パターン

134 バッファ層

134a バッファ層パターン

140 金属膜

140a 金属膜パターン

150 絶縁膜パターン

152 ゲート電極

170 絶縁スペーサ

【技術分野】

【0001】

本発明は、半導体素子及びその製造方法に係り、特にポリメタルゲート電極を持つ半導体素子及びその製造方法に関する。

【背景技術】

【0002】

半導体素子が高集積化されてデザインルールが100nm以下に減少するにつれて、ゲート電極を構成するワードラインのような配線層での抵抗が大きくなって信号遅延が急増しつつある。これにより、低抵抗の配線を具現化するための努力のうち一つとして、半導体基板上に導電性ポリシリコン層、バリアー膜、及び金属膜が順に形成される積層構造を備えるポリメタルゲート電極が提案された。

【0003】

ポリメタルゲート電極を形成するに当って、これまで提案された構造では、バリアー膜として主にWNまたはWSiNを使用した(例えば、特許文献1参照)。しかし、バリアー膜としてWNまたはWSiNを使用する場合、ワードラインの抵抗は低めることができる。しかし、これらの膜は熱に対する安定性が不良であって、後続の高温熱処理工程、例えば、ワードラインパターニングした後にパターニング時に損傷した膜質を復旧するための選択的酸化工程時、約800℃またはそれ以上の高温熱処理によってバリアー膜が局部的に破壊される現象が発生する。その結果、前記導電性ポリシリコン層のSiと前記金属膜の金属とが相互反応して金属シリサイドが形成される現象が発生する。

【0004】

図1A及び図1Bは、ポリメタルゲート構造で、前記バリアー膜としてWNを使用した場合に、熱処理時に発生する問題点を確認した結果を示すSEM(Scanning Electron Microscope)イメージである。

図1Aには、Si基板上にゲート酸化膜(Gox)、ポリシリコン層(Poly−Si)、約50ÅのWNバリアー膜、そして、約400ÅのW膜が形成されている断面構造が示されている。

【0005】

図1Bには、図1Aの構造を約850℃の温度下で約40分間熱処理した結果得られた断面構造が示されている。図1Bで、ポリシリコン層とW膜との間にあるWN膜が熱処理によりW及びNに分解されて局部的に破壊され、ポリシリコン層及びW膜の大部分がタングステンシリサイド化したことが確認できる。

【0006】

したがって、ポリメタルゲート構造でバリアー膜の熱的安定性を改善できる新たな技術が必要である。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】米国特許第6,774,442号明細書

【発明の概要】

【発明が解決しようとする課題】

【0008】

本発明の目的は、前記した従来技術での問題点を解決しようとするものであって、高集積化された半導体素子に必要な低抵抗配線を具現化すると同時に熱的に安定した配線構造を持つ半導体素子を提供することである。

本発明の他の目的は、高集積化された半導体素子に必要な低抵抗配線を具現化すると同時に熱的に安定した配線構造を形成できる半導体素子の製造方法を提供することである。

【課題を解決するための手段】

【0009】

前記目的を達成するために、本発明による半導体素子は、半導体基板上に形成されたゲート絶縁膜と、前記ゲート絶縁膜上に前記半導体基板側から順に積層された導電性ポリシリコン膜、第1金属シリサイド膜、バリアー膜、及び金属膜から形成されるポリメタルゲート電極と、を備え、前記バリアー膜は、前記第1金属シリサイド膜上に形成されるTiN膜と、前記TiN膜と前記金属膜との間に介在されるバッファ層と、を備える。

【0010】

前記バッファ層は、Ti、Ta、Zr、Hf及びSiから形成される群から選択される少なくとも一つの物質からなる。または、前記バッファ層は、非晶質の第2金属シリサイド膜から形成される。

【0011】

前記他の目的を達成するために、本発明による半導体素子の製造方法では、半導体基板上に導電性ポリシリコン膜及び第1金属シリサイド膜を順に形成する。前記第1金属シリサイド膜上にTiN膜及びバッファ層で構成されるバリアー膜を形成する。前記バッファ層上に金属膜を形成する。前記導電性ポリシリコン膜、第1金属シリサイド膜、バリアー膜及び金属膜をパターニングしてゲート電極を形成する。

【発明の効果】

【0012】

本発明によれば、ポリメタルゲートのバリアー膜としてTiN膜を使用することによってゲート積層構造の熱安定性を改善でき、バリアー膜として使われるTiN膜と上部の金属膜との間に前記金属膜の粒径を増大させるためのバッファ層を挿入することによって、ワードライン抵抗を低めることができる。このバッファ層として、結晶質の金属膜(例えば、Ti、Ta、Zr、Hf、Siなど)または非晶質の金属シリサイド膜が使われることができる。また、ポリシリコン膜とバリアー膜との間に金属シリサイド膜を挿入することによって、上部の金属膜と下部のポリシリコン膜との界面抵抗を低減させることができる。

【図面の簡単な説明】

【0013】

【図1A】従来技術によるポリメタルゲート構造で、バリアー膜としてWNを使用した場合の熱処理前のSEMイメージである。

【図1B】従来技術によるポリメタルゲート構造で、バリアー膜としてWNを使用した場合の熱処理後のSEMイメージである。

【図2A】本発明の望ましい実施形態による半導体素子の製造方法を説明するために、工程順序によって示す断面図である。

【図2B】本発明の望ましい実施形態による半導体素子の製造方法を説明するために、工程順序によって示す断面図である。

【図2C】本発明の望ましい実施形態による半導体素子の製造方法を説明するために、工程順序によって示す断面図である。

【図2D】本発明の望ましい実施形態による半導体素子の製造方法を説明するために、工程順序によって示す断面図である。

【図3】本発明による半導体素子であるゲート電極のバリアー膜を構成するTiN膜に対して熱に対する安定性を確認した結果を示すSEMイメージである。

【図4】ポリメタルゲート構造で、バリアー膜の構成物質によってゲート電極のW膜での粒径及び比抵抗を評価した例を示すグラフである。

【図5】ポリメタルゲート構造で、バリアー膜の構成物質によってゲート電極のW膜でのシート抵抗を評価した例を示すグラフである。

【図6】ポリメタルゲート構造で、バリアー膜の構造及びタングステンシリサイドコンタクトの存否による金属膜とポリシリコン膜との界面抵抗変化を評価した結果を示すグラフである。

【図7】比較例として示したポリメタルゲート構造での金属膜とポリシリコン膜との界面抵抗変化を評価した結果を示すグラフである。

【発明を実施するための形態】

【0014】

次いで、本発明の望ましい実施形態について添付図面を参照して詳細に説明する。

図2Aないし図2Dは、本発明の望ましい実施形態による半導体素子の製造方法を説明するために、工程順序によって示す断面図である。

【0015】

図2Aを参照すれば、半導体基板100にSTI(Shallow Trench Isolation)方法で素子分離領域102を形成して、前記半導体基板100に活性領域104を画定する。

【0016】

その後、前記半導体基板100上にゲート絶縁膜110を形成する。例えば、前記ゲート絶縁膜110は約50Å厚さの酸化膜から形成されることができる。

前記ゲート絶縁膜110上に導電性ポリシリコン膜120及び第1金属シリサイド膜122を順に形成する。前記導電性ポリシリコン膜120は、約500Å〜1000Åの厚さに形成できる。前記第1金属シリサイド膜122は、約50Åの厚さに形成できる。前記第1金属シリサイド膜122は、形成しようとする配線構造でオームコンタクトを形成するために挿入されたものであって、例えば、タングステン(W)シリサイド膜、モリブデン(Mo)シリサイド膜、チタン(Ti)シリサイド膜、タンタル(Ta)シリサイド膜、ハフニウム(Hf)シリサイド膜、またはコバルト(Co)シリサイド膜の少なくともいずれか一つから形成されることができる。前記第1金属シリサイド膜122は、金属(M)に対するシリコン(Si)の原子比(Si/M)が2.0〜10.0である組成を持つように形成できる。

【0017】

前記第1金属シリサイド膜122上に、TiN膜132及びバッファ層134で構成されるバリアー膜130を形成する。前記TiN膜132及びバッファ層134はそれぞれ形成しようとする配線の設計寸法によってその厚さが変わることができる。例えば、前記TiN膜132は約30Å〜300Åの厚さに形成でき、前記バッファ層134は約10Å〜200Åの厚さに形成できる。また、前記TiN膜132及びバッファ層134は、例えば、PVD(Physical Vapor Deposition:物理蒸着法)、CVD(Chemical Vapor Deposition:化学蒸着法)、またはALD(Atomic Layer Deposition:原子層蒸着法)方法によって形成でき、これら方法のみに制限されるものではない。

【0018】

望ましくは、前記バッファ層134は、結晶質のTi、Ta、Zr、Hf及びSiから形成される群から選択される少なくとも一つの物質から形成されることができる。また望ましくは、前記バッファ層134は、Wシリサイド膜、Moシリサイド膜、Tiシリサイド膜、Taシリサイド膜、Hfシリサイド膜、またはCoシリサイド膜で構成される非晶質の第2金属シリサイド膜から形成されることができる。

【0019】

前記バリアー膜130上に金属膜140を形成する。前記金属膜140は、WまたはMoからなる。

前記バリアー膜130を構成する前記TiN膜132は、その粒径が比較的小さくてその構造が柱状構造をなしているので、その上に直ちに前記金属膜140を形成すれば、金属成長が制限されて前記金属膜140内での金属粒径が小さくなることがある。これは、前記金属膜140のシート抵抗を増大させる結果を招く恐れがある。このような結果を回避するために、本発明では、前記バリアー膜130を前記TiN膜132とそれを覆う前記バッファ層134との積層構造で形成したので、前記バッファ層134上に前記金属膜140が形成される。このような構造では、前記バッファ層134によりその上での金属成長が制限されず、したがって、前記金属膜140の粒径を大きくすることで、シート抵抗を低減させることができる。

【0020】

図2Bを参照すれば、絶縁膜パターン150、例えば、窒化膜パターンを利用して前記導電性ポリシリコン膜120、第1金属シリサイド膜122、バリアー膜130及び金属膜140を異方性ドライエッチング方法によりパターニングして、前記半導体基板100側から導電性ポリシリコン膜パターン120a、第1金属シリサイド膜パターン122a、バリアー膜パターン130a及び金属膜パターン140aが順に積層されたゲート電極152を形成する。前記バリアー膜パターン130aは、TiN膜パターン132aとバッファ層パターン134aとの積層構造で構成される。

【0021】

図2Cを参照すれば、前記ゲート電極152の形成のためのエッチング工程時に損傷したゲート絶縁膜110を復旧するために選択的酸化工程を実施する。前記選択的酸化工程のために、例えば、約700〜1100℃の温度下で熱処理工程を行なうことができる。その結果、前記ゲート電極152中の導電性ポリシリコン膜パターン120aの側壁に酸化膜160が形成され、前記半導体基板100の活性領域104表面が酸化する。

【0022】

図2Dを参照すれば、前記ゲート電極152及びこれを覆っている絶縁膜パターン150をイオン注入マスクとして利用して、前記半導体基板100に低濃度イオン、例えば、N−型またはP−型イオンを注入して前記半導体基板100内にエクステンション領域(図示せず)を形成した後、前記ゲート電極152及び絶縁膜パターン150の側壁に絶縁スペーサ170を形成する。前記絶縁スペーサ170は、例えばシリコン窒化膜から形成される。その後、前記絶縁膜パターン150及び絶縁スペーサ170をイオン注入マスクとして利用して、前記半導体基板100に高濃度イオン、例えば、N+型またはP+型イオンを注入して前記半導体基板100の活性領域104内にソース/ドレーン領域(図示せず)を形成する。

【0023】

図3は、本発明による半導体素子を形成するために、ゲート電極形成のための配線構造内のバリアー膜を構成するTiN膜に対して熱に対する安定性を確認した結果を示すSEMイメージである。

より詳細に説明すれば、図3には、WNバリアー膜の代わりにTiNバリアー膜を形成したことを除いては、図1Aと同じ構造を持つ積層構造について、約850℃で約40分間熱処理した結果得られた断面構造が示されている。図3で、バリアー膜としてTiN膜を適用した場合は、ポリシリコン膜(Poly−Si)とW膜との反応が抑制されて均一なW膜が観察される。これより、TiN膜は熱に対する安定性が比較的優秀であって、高温熱処理後にも破壊されずにバリアー特性を維持することが分かる。

【0024】

ポリメタルゲート構造でバリアー膜の熱に対する安定性を確保するために、熱に対して安定性が立証されたTiN膜をバリアー膜として適用する場合は、TiN膜上に金属膜、例えば、W膜をPVD方法で形成する時にWの粒径が減少する現象が観察される。その結果、WNバリアー膜を使用する場合に比べて、配線ラインでの抵抗が約2倍以上増大して、それを改善する必要がある。

【0025】

図4は、導電性ポリシリコン膜上にW膜が形成されたポリメタルゲート構造で、前記ポリシリコン膜とW膜との間に挿入されるバリアー膜の構成物質によってゲート電極のW膜での粒径及び比抵抗を評価した例を示すグラフである。

【0026】

図4の評価のために、半導体基板側からゲート絶縁膜上にポリシリコン、タングステンシリサイド、バリアー膜、及びW膜を順に形成し、前記バリアー膜としてWNを形成した場合(“W/WN”と表示)、前記バリアー膜として半導体基板側からTiN膜及びTi膜を順に形成した場合(“W/Ti/TiN”と表示)、そして、前記バリアー膜としてTiN膜を形成した場合(“W/TiN”と表示)それぞれに対して、W膜での粒径及び比抵抗を測定した。

【0027】

図4の結果で分かるように、本発明によってバリアー膜としてTiN膜上にTi膜を形成し、その上に前記金属膜としてW膜を形成した場合、Ti膜上に蒸着されるWの粒径が増大して、W膜での比抵抗がW/WN構造でのWの比抵抗である15μΩ・cm〜20μΩ・cmレベルに減少する。

【0028】

図5は、導電性ポリシリコン膜上にW膜が形成されるポリメタルゲート構造で、前記ポリシリコン膜とW膜との間に挿入されるバリアー膜の構成物質によってゲート電極のW膜でのシート抵抗を評価した例を示すグラフである。

図5の評価のために、半導体基板側からゲート絶縁膜上にポリシリコン、タングステンシリサイド、バリアー膜、及びW膜を順に形成し、前記バリアー膜としてWNを形成した場合(“W/WN/WSi/Poly”と表示)、前記バリアー膜として半導体基板側からTiN膜及びタングステンシリサイド膜を順に形成した場合(“W/WSi/TiN/WSi/Poly”と表示)、前記バリアー膜として半導体基板側からTiN膜及びTi膜を順に形成した場合(“W/Ti/TiN/WSi/Poly”と表示)、そして、前記バリアー膜としてTiN膜を形成した場合(“W/TiN/WSi/Poly”と表示)それぞれに対して、W膜でのシート抵抗(Rs)を測定した。

【0029】

図5の結果から分かるように、バリアー膜としてTiN膜のみを形成した場合には、W膜でのRsがWN膜をバリアー膜として使用した場合より約2倍以上増大することが分かる。これは、バリアー膜としてTiN膜のみを形成した場合には、TiN膜の真上に蒸着されるWの粒径がTiNの粒径に影響されて小さくなるためである。

【0030】

一方、本発明のように、バリアー膜としてTiN膜とタングステンシリサイド膜との積層構造、またはTiN膜とTi膜との積層構造を使用した場合には、W膜でのRsがWN膜をバリアー膜として使用した場合とほぼ同等なレベルまで減少した。これは、TiN膜上に結晶質のTi膜または非晶質のタングステンシリサイド膜を形成した結果であって、W膜が非晶質膜上に形成されることによってW膜内での粒径が増大したためである。したがって、本発明による半導体素子では、ポリメタルゲート構造でポリシリコン膜と金属膜との間に挿入されるバリアー膜として、TiN膜と非晶質の金属シリサイド膜、またはTiN膜と結晶質のTi膜との積層構造を使用することによって、前記TiN膜によって熱安定性を確保すると同時に前記バッファ層によって上部金属膜の粒径を大きくして、熱に対して安定した構造及び低抵抗配線を同時に具現化できる。

【0031】

図6は、ポリメタルゲート構造で、バリアー膜の構造及びポリシリコン膜とバリアー膜との間でのタングステンシリサイドコンタクトの存否による、金属膜とポリシリコン膜との界面抵抗変化を評価した結果を示すグラフである。

図6の評価のために、半導体基板側からポリシリコン膜上にWNバリアー膜及びW膜を形成したポリメタルゲート構造(“W/WN/Poly−Si”と表示)と、半導体基板側からポリシリコン膜上にタングステンシリサイド膜、TiN膜及びTi膜が順に積層されたバリアー膜、及びW膜を形成したポリメタルゲート構造(“W/Ti/TiN/WSix/Poly−Si”と表示)を形成し、これら各構造についてW膜とポリシリコン膜との界面抵抗変化を測定した。

【0032】

本発明による構造であるW/Ti/TiN/WSix/Poly−Si構造では、Ti/TiNバリアー膜の下部にタングステンシリサイド膜を挿入することによって、W膜とポリシリコン膜との間にオームコンタクトを形成できるということが分かる。また、TiN膜上に蒸着されたTi膜によりTiN膜とタングステンシリサイド膜との界面の窒化及び酸化が抑制されて、従来構造であるW/WN/Poly−Si構造に比べて、W膜とポリシリコン膜との界面抵抗を約10−3倍以下に低減させることができる。

【0033】

図7は、比較例として示したポリメタルゲート構造での金属膜とポリシリコン膜との界面抵抗変化を評価した結果を示すグラフである。

図7には、半導体基板側からポリシリコン膜上にWNバリアー膜及びW膜を形成したポリメタルゲート構造(“W/WN/Poly−Si”と表示)と、半導体基板側からポリシリコン膜上にタングステンシリサイド膜、WNバリアー膜及びW膜を形成したポリメタルゲート構造(“W/WN/WSix/Poly−Si”と表示)とに対して測定されたW膜とポリシリコン膜との界面抵抗変化が示されている。

【0034】

図7から分かるように、WNバリアー膜を使用するポリメタルゲート構造では、WNの分解によって発生するNによりシリサイドコンタクトを形成すべく挿入されたタングステンシリサイド膜が窒化されて、W膜とポリシリコン膜との界面にオームコンタクトが形成されない。

【0035】

前記した実験結果から分かるように、本発明によれば、ポリメタルゲートのバリアー膜としてTiN膜を使用することによって、ゲート積層構造の熱安定性を改善でき、バリアー膜として使われるTiN膜と上部の金属膜との間に前記金属膜の粒径を増大させるためのバッファ層を挿入することによって、ワードライン抵抗を低めることができる。また、ポリシリコン膜とバリアー膜との間に金属シリサイド膜を挿入することによって、上部の金属膜と下部のポリシリコン膜との界面抵抗を従来の構造に比べて約10−3倍以下に低減させることができる。したがって、100nm以下のデザインルールを持つ高集積半導体素子でパフォーマンスを顕著に改善できる。

【0036】

以上、本発明を望ましい実施形態を挙げて詳細に説明したが、本発明は、前記実施形態に限定されず、本発明の技術的思想及び範囲内で当業者によりいろいろな変形及び変更が可能である。

【産業上の利用可能性】

【0037】

本発明は、半導体素子の関連技術分野に好適に用いられる。

【符号の説明】

【0038】

100 半導体基板

102 素子分離領域

104 活性領域

110 ゲート絶縁膜

120 導電性ポリシリコン膜

120a 導電性ポリシリコン膜パターン

122 第1金属シリサイド膜

122a 第1金属シリサイド膜パターン

130 バリアー膜

130a バリアー膜パターン

132 TiN膜

132a TiN膜パターン

134 バッファ層

134a バッファ層パターン

140 金属膜

140a 金属膜パターン

150 絶縁膜パターン

152 ゲート電極

170 絶縁スペーサ

【特許請求の範囲】

【請求項1】

半導体基板上に導電性ポリシリコン膜及び第1金属シリサイド膜を順に形成する工程と、

前記第1金属シリサイド膜上にTiN膜を形成する工程と、

前記TiN膜上にTi、Ta、Zr、Hf及びSiから形成される群から選択される少なくとも一つの物質から形成されるバッファ層を形成する工程と、

前記バッファ層上に金属膜を形成する工程と、

前記導電性ポリシリコン膜、第1金属シリサイド膜、前記TiN膜、前記バッファ層、及び前記金属膜をパターニングしてゲート電極を形成する工程と、を含む

ことを特徴とする半導体素子の製造方法。

【請求項2】

前記第1金属シリサイド膜は、金属に対するシリコンの原子比が2.0〜10.0の組成を持つように形成される

ことを特徴とする請求項1に記載の半導体素子の製造方法。

【請求項3】

前記第1金属シリサイド膜は、タングステンシリサイド膜、モリブデンシリサイド膜、チタンシリサイド膜、タンタルシリサイド膜、ハフニウムシリサイド膜、またはコバルトシリサイド膜の少なくともいずれか一つから形成される

ことを特徴とする請求項1に記載の半導体素子の製造方法。

【請求項4】

前記TiN膜及びバッファ層は、それぞれ物理蒸着法、化学蒸着法、または原子層蒸着法によって形成される

ことを特徴とする請求項1に記載の半導体素子の製造方法。

【請求項5】

前記TiN膜は、30Å〜300Åの厚さに形成され、前記バッファ層は、10Å〜200Åの厚さに形成される

ことを特徴とする請求項1に記載の半導体素子の製造方法。

【請求項6】

前記バリアー膜を形成するステップは、

前記第1金属シリサイド膜上にTiN膜を形成するステップと、

前記TiN膜上に非晶質の第2金属シリサイド膜を形成するステップと、を含む

ことを特徴とする請求項1に記載の半導体素子の製造方法。

【請求項7】

前記第2金属シリサイド膜は、タングステンシリサイド膜、モリブデンシリサイド膜、チタンシリサイド膜、タンタルシリサイド膜、ハフニウムシリサイド膜、またはコバルトシリサイド膜の少なくともいずれか一つから形成される

ことを特徴とする請求項6に記載の半導体素子の製造方法。

【請求項8】

前記TiN膜及び第2金属シリサイド膜は、それぞれ物理蒸着法、化学蒸着法、または原子層蒸着法によって形成される

ことを特徴とする請求項6に記載の半導体素子の製造方法。

【請求項9】

前記TiN膜は、30Å〜300Åの厚さに形成され、前記第2金属シリサイド膜は、10Å〜200Åの厚さに形成される

ことを特徴とする請求項6に記載の半導体素子の製造方法。

【請求項10】

前記金属膜は、タングステンまたはモリブデンから形成される

ことを特徴とする請求項1に記載の半導体素子の製造方法。

【請求項11】

前記ゲート電極を形成した後、前記ゲート電極中の前記導電性ポリシリコン膜の側壁を酸化させるステップをさらに含む

ことを特徴とする請求項1に記載の半導体素子の製造方法。

【請求項1】

半導体基板上に導電性ポリシリコン膜及び第1金属シリサイド膜を順に形成する工程と、

前記第1金属シリサイド膜上にTiN膜を形成する工程と、

前記TiN膜上にTi、Ta、Zr、Hf及びSiから形成される群から選択される少なくとも一つの物質から形成されるバッファ層を形成する工程と、

前記バッファ層上に金属膜を形成する工程と、

前記導電性ポリシリコン膜、第1金属シリサイド膜、前記TiN膜、前記バッファ層、及び前記金属膜をパターニングしてゲート電極を形成する工程と、を含む

ことを特徴とする半導体素子の製造方法。

【請求項2】

前記第1金属シリサイド膜は、金属に対するシリコンの原子比が2.0〜10.0の組成を持つように形成される

ことを特徴とする請求項1に記載の半導体素子の製造方法。

【請求項3】

前記第1金属シリサイド膜は、タングステンシリサイド膜、モリブデンシリサイド膜、チタンシリサイド膜、タンタルシリサイド膜、ハフニウムシリサイド膜、またはコバルトシリサイド膜の少なくともいずれか一つから形成される

ことを特徴とする請求項1に記載の半導体素子の製造方法。

【請求項4】

前記TiN膜及びバッファ層は、それぞれ物理蒸着法、化学蒸着法、または原子層蒸着法によって形成される

ことを特徴とする請求項1に記載の半導体素子の製造方法。

【請求項5】

前記TiN膜は、30Å〜300Åの厚さに形成され、前記バッファ層は、10Å〜200Åの厚さに形成される

ことを特徴とする請求項1に記載の半導体素子の製造方法。

【請求項6】

前記バリアー膜を形成するステップは、

前記第1金属シリサイド膜上にTiN膜を形成するステップと、

前記TiN膜上に非晶質の第2金属シリサイド膜を形成するステップと、を含む

ことを特徴とする請求項1に記載の半導体素子の製造方法。

【請求項7】

前記第2金属シリサイド膜は、タングステンシリサイド膜、モリブデンシリサイド膜、チタンシリサイド膜、タンタルシリサイド膜、ハフニウムシリサイド膜、またはコバルトシリサイド膜の少なくともいずれか一つから形成される

ことを特徴とする請求項6に記載の半導体素子の製造方法。

【請求項8】

前記TiN膜及び第2金属シリサイド膜は、それぞれ物理蒸着法、化学蒸着法、または原子層蒸着法によって形成される

ことを特徴とする請求項6に記載の半導体素子の製造方法。

【請求項9】

前記TiN膜は、30Å〜300Åの厚さに形成され、前記第2金属シリサイド膜は、10Å〜200Åの厚さに形成される

ことを特徴とする請求項6に記載の半導体素子の製造方法。

【請求項10】

前記金属膜は、タングステンまたはモリブデンから形成される

ことを特徴とする請求項1に記載の半導体素子の製造方法。

【請求項11】

前記ゲート電極を形成した後、前記ゲート電極中の前記導電性ポリシリコン膜の側壁を酸化させるステップをさらに含む

ことを特徴とする請求項1に記載の半導体素子の製造方法。

【図1A】

【図1B】

【図2A】

【図2B】

【図2C】

【図2D】

【図3】

【図4】

【図5】

【図6】

【図7】

【図1B】

【図2A】

【図2B】

【図2C】

【図2D】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−102219(P2013−102219A)

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願番号】特願2013−18318(P2013−18318)

【出願日】平成25年2月1日(2013.2.1)

【分割の表示】特願2006−113558(P2006−113558)の分割

【原出願日】平成18年4月17日(2006.4.17)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願日】平成25年2月1日(2013.2.1)

【分割の表示】特願2006−113558(P2006−113558)の分割

【原出願日】平成18年4月17日(2006.4.17)

【出願人】(390019839)三星電子株式会社 (8,520)

【氏名又は名称原語表記】Samsung Electronics Co.,Ltd.

【住所又は居所原語表記】129,Samsung−ro,Yeongtong−gu,Suwon−si,Gyeonggi−do,Republic of Korea

【Fターム(参考)】

[ Back to top ]