Fターム[4M104GG09]の内容

Fターム[4M104GG09]に分類される特許

1 - 20 / 4,748

ヘテロ接合電界効果型トランジスタおよびその製造方法

半導体装置及び半導体装置の製造方法

半導体装置の製造方法

薄膜トランジスタ及びその製造方法、並びに薄膜トランジスタを備えた表示装置、スパッタリングターゲット材

半導体装置およびその製造方法

トランジスタ、表示装置および電子機器

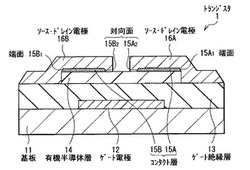

【課題】良好な歩留りで製造可能なトランジスタ、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層に電気的に接続された一対のソース・ドレイン電極と、前記一対のソース・ドレイン電極それぞれと前記半導体層との間のキャリア移動経路に設けられ、その端面が前記ソース・ドレイン電極に覆われたコンタクト層と、を備えたトランジスタ。

(もっと読む)

半導体装置およびその製造方法ならびに表示装置および電子機器

【課題】配線層の膜応力を低減し、製造歩留まりを向上することが可能な半導体装置およびその製造方法並びに表示装置および電子機器を提供する。

【解決手段】本技術の半導体装置は、一方向に延在する複数の第1配線層と、第1配線層の間に設けられた第1配線層よりも膜厚が薄いゲート電極と、第1配線層およびゲート電極上に形成された絶縁膜と、絶縁膜上の前記ゲート電極に対応する位置にチャネル領域を有する半導体層と、半導体層上に設けられた層間膜と、層間膜上に形成されると共に、層間膜に設けられた貫通孔を介して半導体層と接続された第2配線層とを備えている。

(もっと読む)

半導体装置とその製造方法

【課題】ゲート高さが低いため製造容易で、ゲート−コンタクト間の容量を抑制し、ゲート−コンタクト間の短絡を抑制した半導体装置を提供する。

【解決手段】半導体装置の製造方法は基板上にFin型半導体層を形成する。Fin型半導体層に交差するダミーゲートが形成される。Fin型半導体層にソースおよびドレインが形成される。ダミーゲート上に層間絶縁膜を堆積した後、ダミーゲートの上面を露出させる。ダミーゲートを除去してゲートトレンチを形成する。ゲートトレンチ内のFin型半導体層の上部をリセスする。ゲートトレンチ内のFin型半導体層の表面にゲート絶縁膜を形成する。ゲート電極をゲートトレンチ内に充填する。ゲート電極をエッチングバックすることによってゲート電極を形成する。ゲート電極の上面の高さはソースおよびドレインにおけるFin型半導体層の上面の高さ以下かつゲートトレンチ内のFin型半導体層の上面の高さ以上である。

(もっと読む)

電力用半導体装置およびその製造方法

【課題】フィールドプレート電極を有するトレンチゲート構造を備えた電力用半導体装置においてゲート−ソース間容量を低減する。

【解決手段】電力用半導体装置は、第1導電形の第1の半導体層2、フィールド絶縁膜6、フィールドプレート電極7、第1の絶縁膜8、導電体9、第2の絶縁膜11、ゲート絶縁膜10、及びゲート電極12を備える。フィールドプレート電極7は、フィールド絶縁膜6を介して第1の半導体層2のトレンチ5内に設けられる。第1の絶縁膜8は、フィールドプレート電極7上に設けられ、フィールド絶縁膜6とともにフィールドプレート電極7を取り囲む。導電体9は、第1の絶縁膜8上に設けられ、フィールドプレート電極7とは絶縁される。ゲート電極12は、フィールド絶縁膜6の上端上に設けられ第2の絶縁膜11を介して導電体に隣接し、ゲート絶縁膜10を介してトレンチ5内に設けられる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であり、高い電気特性を有する半導体装置を歩留まりよく提供する。

【解決手段】酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、ゲート電極上の導電膜と、酸化物半導体膜及びゲート絶縁膜の側面に接するソース電極及びドレイン電極と、を有し、ソース電極及びドレイン電極の上面の高さは、ゲート電極の上面の高さより低く、導電膜、ソース電極及びドレイン電極は、同一の金属元素を有する半導体装置である。また、ゲート電極の側面を覆う側壁絶縁膜を形成してもよい。

(もっと読む)

トランジスタ、トランジスタの製造方法、表示装置および電子機器

【課題】歩留り良く製造可能なトランジスタ、トランジスタの製造方法、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層上のエッチングストッパ層と、前記半導体層上の、少なくとも前記エッチングストッパ層の両側に設けられた一対のコンタクト層と、前記半導体層に前記一対のコンタクト層を介して電気的に接続されると共に前記絶縁層に接するソース・ドレイン電極と、を備えたトランジスタ。

(もっと読む)

半導体素子及びその製造方法

【課題】半導体素子及びその製造方法を提供する。

【解決手段】高電圧領域及び低電圧領域を有する半導体基板100と、高電圧領域に形成され、第1活性領域110-I、第1ソース/ドレイン領域114-I、第1ゲート絶縁膜130及び第1ゲート電極202-Iを有する高電圧トランジスタTR-Iと、低電圧領域に形成され、第2活性領域110-II、第2ソース/ドレイン領域114-II、第2ゲート絶縁膜310及び第2ゲート電極320を有する低電圧トランジスタTR-IIとを備え、第2ソース/ドレイン領域は、第1ソース/ドレイン領域より薄い厚さを有することを特徴とする半導体素子。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板上の複数の半導体層のうちの1つを正確に選択する。

【解決手段】実施形態に係わる半導体装置は、第1乃至第3の半導体層12−1〜12−3と、第1乃至第3の半導体層12−1〜12−3のうちの1つを選択するレイヤー選択トランジスタ15(LST)とを備える。第1のノーマリーオン領域17−1は、第1の半導体層12−1内において第1乃至第3のゲート電極16−1〜16−3に隣接するチャネルをノーマリーオンチャネルにし、第2のノーマリーオン領域17−2は、第2の半導体層12−2内において第2乃至第4のゲート電極16−2〜16−4に隣接するチャネルをノーマリーオンチャネルにし、第3のノーマリーオン領域17−3は、第3の半導体層12−3内において第3乃至第5のゲート電極16−3〜16−5に隣接するチャネルをノーマリーオンチャネルにする。

(もっと読む)

配線の形成方法、電子素子、および表示装置

【課題】物理的な版を必要とせず、微細な導電パターンを形成でき、パターン変更に対して柔軟に対応できる配線の形成方法を提供する。

【解決手段】本発明では、基板上に、エネルギー付与によって臨界表面張力が変化する材料を含有する濡れ性変化層を形成する工程と、前記濡れ性変化層に選択的にレーザ光を照射して、前記濡れ性変化層の臨界表面張力が高くなるように変化させた高表面エネルギー領域部を前記濡れ性変化層に形成する工程と、前記高表面エネルギー領域部に導電性インクを塗布し、前記高表面エネルギー領域部上に配線を形成する工程と、を有し、前記濡れ性変化層と前記高表面エネルギー領域部とには段差がなく、前記配線は前記高表面エネルギー領域部上に形成されていることを特徴とする配線の形成方法が提供される。

(もっと読む)

半導体装置の製造方法

【課題】接続孔部分における電気的特性のばらつきを低減することにより、半導体装置の信頼性および製造歩留まりを向上させることのできる技術を提供する。

【解決手段】成膜装置のドライクリーニング処理用のチャンバ57に備わるウエハステージ57a上に半導体ウエハSWを置いた後、還元ガスを供給して半導体ウエハSWの主面上をドライクリーニング処理し、続いて180℃に維持されたシャワーヘッド57cにより半導体ウエハSWを100から150℃の第1の温度で熱処理する。次いで半導体ウエハSWをチャンバ57から熱処理用のチャンバへ真空搬送した後、そのチャンバ57において150から400℃の第2の温度で半導体ウエハSWを熱処理することにより、半導体ウエハSWの主面上に残留する生成物を除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】低電流領域でのオン電圧を低減することができる、SiC−IGBTを備える半導体装置およびその製造方法を提供すること。

【解決手段】エミッタ電極26と、エミッタ電極26に接続されたエミッタ領域41と、エミッタ領域41に対してSiC半導体層23の裏面25側にエミッタ領域41に接して形成されたチャネル領域39と、チャネル領域39に対してSiC半導体層23の裏面25側にチャネル領域39に接して形成されたSiCベース層33と、SiCベース層33に対してSiC半導体層23の裏面25側にSiCベース層33に接して形成されたコレクタ領域37と、コレクタ領域37に接続されたコレクタ電極27とを含む、SiC−IGBT9に対してMOSFET11を並列に接続する。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】ゲート絶縁膜の膜減り及びダメージを抑え、微細なトランジスタを歩留まり良く作製する。

【解決手段】絶縁表面上の半導体膜と、半導体膜上のゲート絶縁膜と、ゲート絶縁膜上の、第1の金属膜および第1の金属膜上の第2の金属膜を有するゲート電極と、ゲート絶縁膜上に形成され、かつ第1の金属膜の側面と接し、第1の金属膜と同一の金属元素を有する金属酸化物膜と、を有し、第2の金属膜より第1の金属膜のほうが、イオン化傾向が大きい半導体装置である。

(もっと読む)

機能性デバイスの製造方法並びに薄膜トランジスタ及び圧電式インクジェットヘッド

【課題】従来よりも大幅に少ない原材料及び製造エネルギーを用いて、かつ、従来よりも短工程で製造することが可能な機能性デバイスの製造方法を提供する。

【解決手段】熱処理することにより機能性固体材料となる機能性液体材料を準備する第1工程と、基材上に機能性液体材料を塗布することにより、機能性固体材料の前駆体組成物層を形成する第2工程と、前駆体組成物層を80℃〜200℃の範囲内にある第1温度に加熱することにより、前駆体組成物層の流動性を予め低くしておく第3工程と、前駆体組成物層を80℃〜300℃の範囲内にある第2温度に加熱した状態で前駆体組成物層に対して型押し加工を施すことにより、前駆体組成物層に型押し構造を形成する第4工程と、前駆体組成物層を第2温度よりも高い第3温度で熱処理することにより、前駆体組成物層から機能性固体材料層を形成する第5工程とをこの順序で含む機能性デバイスの製造方法。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性の高い半導体装置、及び該半導体装置の作製方法を提供する。半導体装置を歩留まりよく作製し、高生産化を達成する。

【解決手段】ゲート電極層、ゲート絶縁膜、酸化物半導体膜が順に積層され、酸化物半導体膜に接するソース電極層及びドレイン電極層が設けられたトランジスタを有する半導体装置において、エッチング工程により、ソース電極層及びドレイン電極層を形成後、酸化物半導体膜表面及び該近傍に存在するエッチング工程起因の不純物を除去する工程を行う。

(もっと読む)

半導体装置およびその製造方法

【課題】チャネル移動度の低下およびパンチスルーの発生が抑制され、かつ効率的に製造することができる半導体装置およびその製造方法を提供する。

【解決手段】MOSFET1は、{0001}面に対するオフ角が50°以上65°以下である側壁面20Aを有するトレンチ20が形成された基板10と、酸化膜30と、ゲート電極40とを備えている。基板10は、ソース領域14と、ボディ領域13と、ソース領域14との間にボディ領域13を挟むように形成されたドリフト領域12とを含む。ソース領域14およびボディ領域13はイオン注入により形成されている。ボディ領域13においてソース領域14とドリフト領域12との間に挟まれた内部領域13Aの主表面10Aに垂直な方向における厚みは、1μm以下である。ボディ領域13の不純物濃度は、3×1017cm−3以上である。

(もっと読む)

1 - 20 / 4,748

[ Back to top ]