Fターム[4M104BB19]の内容

Fターム[4M104BB19]の下位に属するFターム

CoSi (1,014)

NiSi (1,464)

PtSi (542)

PdSi (202)

高融点金属のシリサイド (2,215)

Fターム[4M104BB19]に分類される特許

1 - 20 / 389

ヘテロ接合電界効果型トランジスタおよびその製造方法

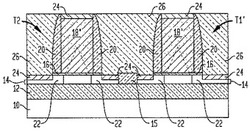

横方向に可変の仕事関数を有するゲート電極を含む半導体構造体

【課題】 横方向に可変の仕事関数を有するゲート電極を含む半導体構造体を提供する。

【解決手段】 CMOS構造体などの半導体構造体が、横方向に可変の仕事関数を有するゲート電極を含む。横方向に可変の仕事関数を有するゲート電極は、角度傾斜イオン注入法又は逐次積層法を用いて形成することができる。横方向に可変の仕事関数を有するゲート電極は、非ドープ・チャネルの電界効果トランジスタ・デバイスに向上した電気的性能をもたらす。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、シリコン層上に、抵抗値が低く、かつ平坦性の良好なニッケルモノシリサイド層を形成可能な半導体装置の製造方法を提供することを課題とする。

【解決手段】基板に形成されたシリコン層を覆ように白金を含むニッケル層を堆積する工程であって、シリコン層に近い部分では遠い部分と比較して結晶性が低くなるように、白金を含むニッケル層を堆積する工程S05と、基板を加熱することで、シリコン層と白金を含むニッケル層との界面にニッケルモノシリサイド層を形成する工程S07と、を有する。

(もっと読む)

積層配線、該積層配線を用いた半導体装置及びその製造方法

【課題】マイクロクリスタルシリコン薄膜と金属薄膜との過剰なシリサイド化反応を抑制して、マイクロクリスタルシリコン薄膜の膜剥れを防止する。

【解決手段】半導体装置20の配線として備えられ、マイクロクリスタルシリコン薄膜8と該薄膜上に形成された金属薄膜9とから成る積層配線であって、マイクロクリスタルシリコン薄膜8の結晶組織を構成している結晶粒には、半導体装置の製造時の熱処理で生じた金属薄膜9とのシリサイド化反応に起因して膜厚方向に成長した柱状の結晶粒が含まれ、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である柱状の結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の6%以上15%以下となるように形成されている。

(もっと読む)

半導体装置の製造方法

【課題】一定のドレイン電圧及びゲート電圧に対して得られるドレイン電流を増大することの出来る半導体装置の製造方法を提供する。

【解決手段】チャンネル領域と、ソース領域及びドレイン領域と、前記ソース領域及びドレイン領域にそれぞれ電気的に接続する合計二つの第1の電極と、前記チャンネル領域上にゲート絶縁膜を介して設けられた第2の電極とを備えた半導体装置の製造に際し、前記ゲート絶縁膜を、酸素の含有量を1ppb以下にした水素添加超純水にIPAを添加した洗浄液を用いて、酸素含有量1ppb以下の窒素雰囲気でしかも遮光した状態で表面の洗浄を行ない、かつ等方性酸化または窒化で形成することにより、前記チャンネル領域と前記ゲート絶縁膜との界面の平坦度を、前記ソース領域から前記ドレイン領域に向かう方向での長さ2nmにおけるピーク・トゥ・バレイ値が0.3nm以下となるようにするとともに、前記第1の電極から前記チャンネル領域までの抵抗率を4Ω・μm以下とした。

(もっと読む)

半導体装置およびその製造方法

【課題】ショットキー障壁の高さおよび幅を容易に制御すると共に寄生抵抗が低く、且つ短チャネル効果を効果的に抑制する。

【解決手段】金属ソース・ドレイン電極(ニッケルシリサイド)6とP型シリコン基板1との間に、セシウム含有領域5を形成している。こうして、金属ソース・ドレイン電極6近傍のセシウムをイオン化して正孔に対するエネルギー障壁高さを大きくし、金属ソース・ドレイン電極6とP型シリコン基板1との間のリーク電流を著しく低減する。また、チャネルと金属ソース・ドレイン電極6との間のショットキー障壁の高さおよび幅を実効的に小さくして寄生抵抗を著しく低減する。したがって、金属シリサイドの厚み(深さ)をイオン注入による制約なしに決定でき、極めて浅いソース・ドレインを形成して良好な短チャネル効果特性を得ることができる。

(もっと読む)

半導体装置

【課題】電極抵抗および界面抵抗の低下を実現する熱安定性の高いバリアメタル構造を備えた半導体装置を提供すること。

【解決手段】実施形態の半導体装置は、半導体基板1の上に形成されたポリシリコン膜2と、前記ポリシリコン膜上に形成された金属のシリサイド膜10と、を備える。実施形態の半導体装置は、前記シリサイド膜の上に形成された前記金属の酸化膜4と、前記酸化膜の上に形成されたタングステン或いはモリブデンを含む膜5と、を備える。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高性能な不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1の方向に積み重ねられる第1及び第2のメモリセルMCを有し、第2の方向に延びるフィン型積層構造Fin0〜Fin3と、フィン型積層構造Fin0〜Fin3の第2の方向の一端に接続され、第3の方向に延びる梁5とを備える。フィン型積層構造Fin0〜Fin3及び梁5は、それぞれ、第1の方向に積み重ねられる第1及び第2の半導体層2a,2bを備え、梁5は、第3の方向の一端に第1及び第2の半導体層2a,2bに対するコンタクト部を有し、かつ、梁5とフィン型積層構造Fin0〜Fin3の接続部からコンタクト部まで延びる低抵抗領域8を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲートラストプロセスの工程数を削減しつつ、所望の信頼性及び特性が得られるメタルゲート電極を備えたMISFETを実現できるようにする。

【解決手段】各ゲート溝の少なくとも底面上にゲート絶縁膜112及び保護膜113が順次形成されている。一方のゲート溝内の保護膜113の上には第1の金属含有膜114a及び第2の金属含有膜114bが順次形成されており、他方のゲート溝内の保護膜113の上には第2の金属含有膜114bが形成されている。一方のゲート溝内の保護膜113の厚さと比べて、他方のゲート溝内の保護膜113の厚さは薄い。

(もっと読む)

半導体基板製品の製造方法、これに用いられる薄膜除去液

【課題】白金(Pt)化合物の薄膜を、他の部材を過度に酸化・腐食することなしに除去する半導体基板製品の製造方法、これに用いられる薄膜除去液を提供する。

【解決手段】白金化合物の薄膜を有する半導体基板を準備する工程と、薄膜除去液を準備する工程と、前記半導体基板に前記薄膜除去液を適用して前記白金化合物の薄膜を除去する工程とを含む半導体基板製品の製造方法であって、前記薄膜除去液が、ハロゲン分子、ハロゲンイオン、及び水を組み合わせて含む半導体基板製品の製造方法。

(もっと読む)

半導体デバイス及びその製造方法

【課題】グラフェンの特性を生かしつつ、高耐圧デバイスや紫外発光・受光デバイスを実現する。

【解決手段】半導体デバイスを、2次元構造のグラフェン電極2、3と、グラフェン電極のグラフェン端に結合した2次元構造のボロンナイトライド半導体層5とを備えるものとする。

(もっと読む)

半導体装置の製造方法

【課題】高温化下でも安定な高信頼性を有する配線を容易に精度良く形成する方法を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板上方に窒化チタンからなる第1の絶縁層を形成し、第1の絶縁層に複数の溝を形成し、溝の底面及び側壁下部を覆う部分が溝の側壁上部を覆う部分よりも厚くなるように、溝の底面及び側壁を覆うバリアメタルを形成し、溝のバリアメタル上に金属膜を埋め込み、複数の配線を形成し、第1の絶縁層を除去して、隣り合う複数の配線の間に配線に接するような空隙を形成し、複数の配線の上面に、金属又は酸化物からなるキャップ膜を形成し、複数の配線の上面及び側壁を覆うようにシリコンナイトライドカーバイド膜又は窒化ボロン膜からなる拡散防止膜を形成し、複数の配線の上面を覆い、且つ、複数の配線間に空隙が形成されるように、第2の絶縁層を形成する。

(もっと読む)

半導体装置、金属膜の製造方法及び半導体装置の製造方法

【課題】高集積化することができる半導体装置、金属膜の製造方法及び半導体装置の製造方法を提供することである。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板に形成され、ヒ素を含むヒ素拡散層と、前記ヒ素拡散層上に形成された金属膜と、を備える。前記金属膜は、タングステン、チタン、ルテニウム、ハフニウム及びタンタルからなる群より選択された少なくとも1種の金属、並びにヒ素を含む。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、内部にオミックパターン電極を備え、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフ動作すると共に高耐圧及び高電流で動作可能な、半導体素子及び製造方法を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間され、窒化物半導体層30にショットキー接合されるソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、ドレイン電極50と離間されるように誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】オン抵抗を低め、高電流で動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上部に配設され、内部に2次元電子ガスチャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間して配設され、窒化物半導体層30にショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成され、ドレイン電極50とソース電極60との間にリセスを形成する誘電層40と、ドレイン電極50と離間して誘電層40上及びリセスに配設され、一部が誘電層40を挟んでソース電極60のドレイン方向へのエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

配線構造、表示装置、および半導体装置

【課題】Cu合金層と半導体層との間に通常設けられるバリアメタル層を省略しても優れた低接触抵抗を発揮し得、さらに半導体層との密着性に優れており、且つ電気抵抗率が低減された配線構造を提供すること。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、Cu合金層とを備えた配線構造であって、前記Cu合金層は、基板側から順に、合金成分としてMnと、X(Xは、Ag、Au、C、W、Ca、Mg、Al、SnおよびNiよりなる群から選択される少なくとも一種)を含有する第一層と、純Cu、またはCuを主成分とするCu合金であって前記第一層よりも電気抵抗率の低いCu合金からなる第二層、とを含む積層構造である。

(もっと読む)

薄膜トランジスタ装置およびその製造方法

【課題】十分なキャパシタ容量が得られ、リーク電流や寄生容量を抑制した薄膜トランジスタ装置およびその製造方法を提供する。

【解決手段】薄膜トランジスタを備え、そのゲート電極111、ソース電極131、ドレイン電極132、バス配線、画素電極133、ゲート絶縁膜121、層間絶縁膜122、半導体層141の全部もしくは一部が塗布法もしくは印刷法で形成されてなり、ゲート絶縁膜121および/もしくは層間絶縁膜122が連続膜から構成され、連続膜が薄膜部と厚膜部から構成されてなる。

(もっと読む)

半導体装置

【課題】集積回路の動作速度の向上に有利な技術を提供する。

【解決手段】n型トランジスタおよびp型トランジスタがシリコンの(551)面に形成された半導体装置において、前記n型トランジスタの拡散領域に接触するシリサイド層の厚さが前記p型トランジスタの拡散領域に接触するシリサイド層の厚さよりも薄い。

(もっと読む)

1 - 20 / 389

[ Back to top ]