半導体装置

【課題】電極抵抗および界面抵抗の低下を実現する熱安定性の高いバリアメタル構造を備えた半導体装置を提供すること。

【解決手段】実施形態の半導体装置は、半導体基板1の上に形成されたポリシリコン膜2と、前記ポリシリコン膜上に形成された金属のシリサイド膜10と、を備える。実施形態の半導体装置は、前記シリサイド膜の上に形成された前記金属の酸化膜4と、前記酸化膜の上に形成されたタングステン或いはモリブデンを含む膜5と、を備える。

【解決手段】実施形態の半導体装置は、半導体基板1の上に形成されたポリシリコン膜2と、前記ポリシリコン膜上に形成された金属のシリサイド膜10と、を備える。実施形態の半導体装置は、前記シリサイド膜の上に形成された前記金属の酸化膜4と、前記酸化膜の上に形成されたタングステン或いはモリブデンを含む膜5と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、半導体装置に関する。

【背景技術】

【0002】

従来、ポリ・メタルゲート電極構造において、電極となる金属の下部には、ポリシリコンとの拡散バリア性を確保する為に、窒化チタンや窒化タングステン等の金属が成膜されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2008−166686号公報

【特許文献2】特開2008−91835号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

従来技術では、電極の抵抗値やポリシリコン/金属界面抵抗が大きくなるという問題がある。

【0005】

本発明の一つの実施形態は、電極抵抗および界面抵抗の低下を実現する熱安定性の高いバリアメタル構造を備えた半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明の一つの実施形態の半導体装置は、半導体基板の上に形成されたポリシリコン膜と、前記ポリシリコン膜上に形成された金属のシリサイド膜と、を備える。実施形態の半導体装置は、前記シリサイド膜の上に形成された前記金属の酸化膜と、前記酸化膜の上に形成されたタングステン或いはモリブデンを含む膜と、を備える。

【図面の簡単な説明】

【0007】

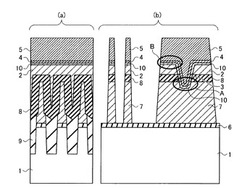

【図1】図1(a)(b)は、第1の実施形態にかかる半導体装置の製造方法の一工程を示す図である。

【図2】図2(a)(b)は、第1の実施形態にかかる半導体装置の製造方法の一工程を示す図である。

【図3】図3は、第1の実施形態にかかる半導体装置の製造方法の一工程を示す図である。

【図4】図4(a)(b)は、第2の実施形態にかかる半導体装置の製造方法の一工程を示す図である。

【図5】図5は、実施形態にかかる各金属酸化膜の生成エネルギーを示した図である。

【図6】図6(a)(b)は、第1および第2の実施形態にかかる半導体装置の構造を示す図である。

【図7】図7(a)(b)は、第3の実施形態にかかる半導体装置の製造方法の一工程を示す図である。

【図8】図8(a)(b)は、第3の実施形態にかかる半導体装置の構造を示す図である。

【発明を実施するための形態】

【0008】

以下に添付図面を参照して、実施形態にかかる半導体装置およびその製造方法を詳細に説明する。なお、これらの実施形態により本発明が限定されるものではない。

【0009】

(第1の実施形態)

まず、図1(a)に示すように半導体基板(シリコン基板)1上にトンネル絶縁膜6、ポリシリコン膜(浮遊ゲート)7、インターポリ絶縁膜(中間絶縁膜)8、ポリシリコン膜2と順次形成した状態で、堆積したポリシリコン膜2の上に、スパッタ法を用いてチタン(Ti)膜3を5nm成膜する。続いて半導体基板1を酸素雰囲気下で200〜300℃で加熱する。この結果、図1(b)に示すように、チタン膜3の表面に膜厚が3.5nm以上と自然酸化膜よりも厚い非晶質かつ導電性を有する酸化チタン(TiOx)膜4が形成される。金属酸化膜である酸化チタン膜4は、金属元素としてチタンを選択してそれを酸化した膜であるが、選択する金属元素はチタンに限る必要は無い。

【0010】

シリコン/電極タングステン間の拡散防止膜として機能させる為には、金属酸化膜の生成エネルギーが酸化シリコン(SiO2)の生成熱(−910kJ/mol)や酸化タングステン(WO3)の生成熱(−843kJ/mol)よりも低く安定して存在する事が必要である。各金属酸化膜の生成エネルギーを示した図5に示すように、チタン以外にジルコニウム(Zr)、ハフニウム(Hf)、バナジウム(V)、ニオブ(Nb)、タンタル(Ta)、スカンジウム(Sc)、イットリウム(Y)、クロム(Cr)の酸化物を用いてもよい。従って、上記金属元素としてはこれらの元素のうちどれか1種類を含んでいるものでもかまわない。

【0011】

次に、図2(a)に示すように酸化チタン膜4の上にスパッタ法もしくはCVD法を用いて電極となるタングステン(W)膜5を、膜厚50nmとなるように成膜した。続いて、タングステン膜5の上に、露光技術を用いて電極のハードマスクパターンをフォトマスクより転写し(図示せず)、RIE(Reactive Ion Etching)技術を用いてタングステン膜5以下の層を電極構造に加工することにより、図2(b)に示すように電極となるタングステン膜5の下層にバリアメタルとしての酸化金属膜(酸化チタン膜4)を有するポリ・メタルゲート電極が作製される。

【0012】

さらに、図2(b)の状態で、例えば900℃で10秒のRTA(Rapid Thermal Annealing)を行うことにより、チタン膜3がシリサイド化され、図3に示すようにTiシリサイド(TiSix)層10が形成される。なおここで、チタン膜3の全てがシリサイド化されず、一部がチタンのまま残存することもある。図2(b)の工程までに不揮発性半導体記憶装置のメモリセルおよび選択ゲートの構造を作成しておけば、このシリサイド工程により図6に示すような構造が形成される。なお、ゲート形状加工とRTAの順番は逆でもかまわない。図6(a)がビット線方向に垂直な断面を示し、図6(b)がワード線方向に垂直な断面を示す。図6(a)に示すようにビット線方向の各構造は素子分離層9にて隔てられている。図6(b)の左側に示したのがセル部で、右側に示したのが選択ゲート部である。

【0013】

図6(b)の左側のメモリセルにおける制御ゲートとなる電極部分(ポリシリコン膜2/Tiシリサイド層10/酸化チタン膜4/タングステン膜5)並びに右側の選択ゲートにおける部分A(ポリシリコン膜7/Tiシリサイド層10/酸化チタン膜4/タングステン膜5)および部分B(ポリシリコン膜2/Tiシリサイド層10/酸化チタン膜4/タングステン膜5)についてポリ・メタル構造が形成されている。上述したように酸化チタン膜4の生成エネルギーの安定性により、この構造はこの後の熱工程によってもミキシングを生じない安定した構造であり、ポリシリコン−タングステン間の拡散バリア性を確保して、界面におけるタングステンシリサイドの形成を防ぐことができる。さらに、インターポリ絶縁膜8を貫通する開口が形成されたコンタクト形成部としての部分Aにおいて、Tiシリサイド層10の存在によりポリシリコン膜(浮遊ゲート)7とタングステン膜5とのコンタクト抵抗を低い値に確保することができる。これに対し、本実施形態で形成した(チタン膜3/酸化チタン膜4)層に代えてバリアメタルとして窒化タングステン(WN)を成膜すると、後の熱工程で窒化タングステン膜中の窒素がポリシリコンを窒化する事によりSiNが形成され、ポリシリコン/金属界面抵抗が上昇するという問題が生ずる。しかし、本実施形態においてはRTAにより形成されるTiシリサイド層10によって低抵抗化が図れる。

【0014】

本実施形態のように酸化チタン膜4の上に成膜した50nmのタングステン膜5の比抵抗は、15.8[μΩ・cm]である。これに対し、例えばバリアメタルとして一般的なチタン系バリア層である窒化チタン(TiN)を成膜すると、その上の電極となる金属の結晶性は、窒化チタンの結晶性を引き継いで微細な結晶粒となる為、電子の粒界散乱の影響が増大して電極の抵抗値が上昇するという問題がある。窒化チタン上に成膜した膜厚50nmのタングステン膜の比抵抗は、28.8[μΩ・cm]と本実施形態の場合に比べて80%増の高抵抗膜となる。即ち、本実施形態の構造を備えることによりポリ・メタル電極を低抵抗化することが可能となる。

【0015】

本実施形態の構造を用いる事でタングステン膜5の比抵抗が下がるのは上記したように、下地の結晶性の違いが原因であると考えられる。酸化チタン膜4の上に成膜したタングステン膜5は、酸化チタン膜4が非晶質である為に下地の影響を受け難い状態で形成される。そのため、タングステン膜5の平均結晶粒径は54.3nmと窒化チタン膜上に形成されるタングステン膜の平均結晶粒径である21.1nmに比べて大きくなっていた。この結果、タングステン膜5の中を流れる電子は、粒界散乱の影響を受け難くなり、タングステン膜5の比抵抗が低くなったと考えられる。なお、上記では電極材料としてタングステンを用いたが、タングステンの代わりにモリブデンを用いても同様な効果が得られる。

【0016】

(第2の実施形態)

本実施形態においては、半導体基板1上にトンネル絶縁膜6、ポリシリコン膜(浮遊ゲート)7、インターポリ絶縁膜8、ポリシリコン膜2と順次形成した状態で、堆積したポリシリコン膜2の上に、スパッタ法を用いてチタン(Ti)膜3を5nm成膜するところまでは図1(a)と同様である。その後、図4(a)に示すように、例えば、スパッタ室中に酸素やオゾン、水等の酸素原子を有する酸化ガスを導入し、反応性スパッタ法を用いて酸化金属膜である酸化チタン膜4を自然酸化膜よりも厚く膜厚が3.5nm以上となるように成膜する。なお、図1(a)のチタンのスパッタ成膜の途中から酸化ガスを導入して金属膜/酸化金属膜の積層構造を形成するように膜中の酸素濃度を半導体基板1の垂直方向に自在に変えて図4(a)の構造を形成しても良い。

【0017】

その後、図4(b)に示すように酸化チタン膜4の上にスパッタ法もしくはCVD法を用いて電極となるタングステン(W)膜5を成膜する。その後の工程は図2(b)及び図3に示したのと同様であり、第1の実施形態と同様な構造を備えた図6に示したポリ・メタル電極構造を作製することが出来る。なお、本実施形態においても電極材料としてタングステンの代わりにモリブデンを用いてもかまわない。

【0018】

(第3の実施形態)

本実施形態においては、図7(a)に示すように半導体基板1上にトンネル絶縁膜6、ポリシリコン膜(浮遊ゲート)7、インターポリ絶縁膜8と順次形成した後、その上にTiN膜11を形成する。その後選択ゲートのコンタクト形成部の開口を形成し、その上から、第1または第2の実施形態と同様な手法でチタン膜3および酸化チタン膜4を開口部を含めコンフォーマルに形成する(図7(b))。その後タングステン膜5を成膜し、例えば900℃で10秒のRTAおよびゲート形状の加工のためのRIEを行うことにより図8に示すような構造が形成される。図8において図6と同一符号の部位は同一の構成を示す。本実施形態においてはRTAにより、図7(b)においてポリシリコン膜7に接したチタン膜3がシリサイド化され、図8(b)に示すようにTiシリサイド(TiSix)層10が形成される。なおここで、ポリシリコン膜7に接したチタン膜3の全てがシリサイド化されず、一部がチタンのまま残存することもある。また、ゲート形状の加工とRTAの順番は逆でもかまわない。

【0019】

図8(a)がビット線方向に垂直な断面を示し、図8(b)がワード線方向に垂直な断面を示す。図8(b)の左側に示したのがセル部で、右側に示したのが選択ゲート部である。本実施形態においては、図8(b)の右側の選択ゲートにおける部分C(ポリシリコン膜7/Tiシリサイド層10/酸化チタン膜4/タングステン膜5)についてポリ・メタル構造が形成される。なお、他の(TiN膜11/チタン膜3/酸化チタン膜4/タングステン膜5)の積層部分はいわゆるメタル・メタルゲート電極構造になっている。

【0020】

本実施形態においても、部分Cは拡散バリア性を有する熱安定性を備えた構造であり、コンタクト抵抗を低い値に確保することができる。また、メタル・メタルゲート電極構造の部分においてはタングステン膜5の比抵抗の低減効果により低抵抗化が図れる。なお、本実施形態においても電極材料としてタングステンの代わりにモリブデンを用いてもかまわない。

【0021】

以上説明したように上記実施形態により、ポリシリコン/電極タングステン(またはモリブデン)間に拡散防止性と熱安定性を兼ね備えた構造を備えたポリ・メタルゲート電極構造及び、メタル・メタルゲート電極構造を作製する事が可能となる。なお、上記実施形態においては、ポリ・メタルゲート電極及び、メタル・メタルゲート電極を例にして説明したが、ゲート電極以外の箇所にも上記実施形態の構造は適用可能である事は言うまでも無い。

【0022】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0023】

1 半導体基板、2 ポリシリコン膜、3 チタン膜、4 酸化チタン膜、5 タングステン膜、6 トンネル絶縁膜、7 ポリシリコン膜(浮遊ゲート)、8 インターポリ絶縁膜、9 素子分離層、10 Tiシリサイド層。

【技術分野】

【0001】

本発明の実施形態は、半導体装置に関する。

【背景技術】

【0002】

従来、ポリ・メタルゲート電極構造において、電極となる金属の下部には、ポリシリコンとの拡散バリア性を確保する為に、窒化チタンや窒化タングステン等の金属が成膜されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2008−166686号公報

【特許文献2】特開2008−91835号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

従来技術では、電極の抵抗値やポリシリコン/金属界面抵抗が大きくなるという問題がある。

【0005】

本発明の一つの実施形態は、電極抵抗および界面抵抗の低下を実現する熱安定性の高いバリアメタル構造を備えた半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明の一つの実施形態の半導体装置は、半導体基板の上に形成されたポリシリコン膜と、前記ポリシリコン膜上に形成された金属のシリサイド膜と、を備える。実施形態の半導体装置は、前記シリサイド膜の上に形成された前記金属の酸化膜と、前記酸化膜の上に形成されたタングステン或いはモリブデンを含む膜と、を備える。

【図面の簡単な説明】

【0007】

【図1】図1(a)(b)は、第1の実施形態にかかる半導体装置の製造方法の一工程を示す図である。

【図2】図2(a)(b)は、第1の実施形態にかかる半導体装置の製造方法の一工程を示す図である。

【図3】図3は、第1の実施形態にかかる半導体装置の製造方法の一工程を示す図である。

【図4】図4(a)(b)は、第2の実施形態にかかる半導体装置の製造方法の一工程を示す図である。

【図5】図5は、実施形態にかかる各金属酸化膜の生成エネルギーを示した図である。

【図6】図6(a)(b)は、第1および第2の実施形態にかかる半導体装置の構造を示す図である。

【図7】図7(a)(b)は、第3の実施形態にかかる半導体装置の製造方法の一工程を示す図である。

【図8】図8(a)(b)は、第3の実施形態にかかる半導体装置の構造を示す図である。

【発明を実施するための形態】

【0008】

以下に添付図面を参照して、実施形態にかかる半導体装置およびその製造方法を詳細に説明する。なお、これらの実施形態により本発明が限定されるものではない。

【0009】

(第1の実施形態)

まず、図1(a)に示すように半導体基板(シリコン基板)1上にトンネル絶縁膜6、ポリシリコン膜(浮遊ゲート)7、インターポリ絶縁膜(中間絶縁膜)8、ポリシリコン膜2と順次形成した状態で、堆積したポリシリコン膜2の上に、スパッタ法を用いてチタン(Ti)膜3を5nm成膜する。続いて半導体基板1を酸素雰囲気下で200〜300℃で加熱する。この結果、図1(b)に示すように、チタン膜3の表面に膜厚が3.5nm以上と自然酸化膜よりも厚い非晶質かつ導電性を有する酸化チタン(TiOx)膜4が形成される。金属酸化膜である酸化チタン膜4は、金属元素としてチタンを選択してそれを酸化した膜であるが、選択する金属元素はチタンに限る必要は無い。

【0010】

シリコン/電極タングステン間の拡散防止膜として機能させる為には、金属酸化膜の生成エネルギーが酸化シリコン(SiO2)の生成熱(−910kJ/mol)や酸化タングステン(WO3)の生成熱(−843kJ/mol)よりも低く安定して存在する事が必要である。各金属酸化膜の生成エネルギーを示した図5に示すように、チタン以外にジルコニウム(Zr)、ハフニウム(Hf)、バナジウム(V)、ニオブ(Nb)、タンタル(Ta)、スカンジウム(Sc)、イットリウム(Y)、クロム(Cr)の酸化物を用いてもよい。従って、上記金属元素としてはこれらの元素のうちどれか1種類を含んでいるものでもかまわない。

【0011】

次に、図2(a)に示すように酸化チタン膜4の上にスパッタ法もしくはCVD法を用いて電極となるタングステン(W)膜5を、膜厚50nmとなるように成膜した。続いて、タングステン膜5の上に、露光技術を用いて電極のハードマスクパターンをフォトマスクより転写し(図示せず)、RIE(Reactive Ion Etching)技術を用いてタングステン膜5以下の層を電極構造に加工することにより、図2(b)に示すように電極となるタングステン膜5の下層にバリアメタルとしての酸化金属膜(酸化チタン膜4)を有するポリ・メタルゲート電極が作製される。

【0012】

さらに、図2(b)の状態で、例えば900℃で10秒のRTA(Rapid Thermal Annealing)を行うことにより、チタン膜3がシリサイド化され、図3に示すようにTiシリサイド(TiSix)層10が形成される。なおここで、チタン膜3の全てがシリサイド化されず、一部がチタンのまま残存することもある。図2(b)の工程までに不揮発性半導体記憶装置のメモリセルおよび選択ゲートの構造を作成しておけば、このシリサイド工程により図6に示すような構造が形成される。なお、ゲート形状加工とRTAの順番は逆でもかまわない。図6(a)がビット線方向に垂直な断面を示し、図6(b)がワード線方向に垂直な断面を示す。図6(a)に示すようにビット線方向の各構造は素子分離層9にて隔てられている。図6(b)の左側に示したのがセル部で、右側に示したのが選択ゲート部である。

【0013】

図6(b)の左側のメモリセルにおける制御ゲートとなる電極部分(ポリシリコン膜2/Tiシリサイド層10/酸化チタン膜4/タングステン膜5)並びに右側の選択ゲートにおける部分A(ポリシリコン膜7/Tiシリサイド層10/酸化チタン膜4/タングステン膜5)および部分B(ポリシリコン膜2/Tiシリサイド層10/酸化チタン膜4/タングステン膜5)についてポリ・メタル構造が形成されている。上述したように酸化チタン膜4の生成エネルギーの安定性により、この構造はこの後の熱工程によってもミキシングを生じない安定した構造であり、ポリシリコン−タングステン間の拡散バリア性を確保して、界面におけるタングステンシリサイドの形成を防ぐことができる。さらに、インターポリ絶縁膜8を貫通する開口が形成されたコンタクト形成部としての部分Aにおいて、Tiシリサイド層10の存在によりポリシリコン膜(浮遊ゲート)7とタングステン膜5とのコンタクト抵抗を低い値に確保することができる。これに対し、本実施形態で形成した(チタン膜3/酸化チタン膜4)層に代えてバリアメタルとして窒化タングステン(WN)を成膜すると、後の熱工程で窒化タングステン膜中の窒素がポリシリコンを窒化する事によりSiNが形成され、ポリシリコン/金属界面抵抗が上昇するという問題が生ずる。しかし、本実施形態においてはRTAにより形成されるTiシリサイド層10によって低抵抗化が図れる。

【0014】

本実施形態のように酸化チタン膜4の上に成膜した50nmのタングステン膜5の比抵抗は、15.8[μΩ・cm]である。これに対し、例えばバリアメタルとして一般的なチタン系バリア層である窒化チタン(TiN)を成膜すると、その上の電極となる金属の結晶性は、窒化チタンの結晶性を引き継いで微細な結晶粒となる為、電子の粒界散乱の影響が増大して電極の抵抗値が上昇するという問題がある。窒化チタン上に成膜した膜厚50nmのタングステン膜の比抵抗は、28.8[μΩ・cm]と本実施形態の場合に比べて80%増の高抵抗膜となる。即ち、本実施形態の構造を備えることによりポリ・メタル電極を低抵抗化することが可能となる。

【0015】

本実施形態の構造を用いる事でタングステン膜5の比抵抗が下がるのは上記したように、下地の結晶性の違いが原因であると考えられる。酸化チタン膜4の上に成膜したタングステン膜5は、酸化チタン膜4が非晶質である為に下地の影響を受け難い状態で形成される。そのため、タングステン膜5の平均結晶粒径は54.3nmと窒化チタン膜上に形成されるタングステン膜の平均結晶粒径である21.1nmに比べて大きくなっていた。この結果、タングステン膜5の中を流れる電子は、粒界散乱の影響を受け難くなり、タングステン膜5の比抵抗が低くなったと考えられる。なお、上記では電極材料としてタングステンを用いたが、タングステンの代わりにモリブデンを用いても同様な効果が得られる。

【0016】

(第2の実施形態)

本実施形態においては、半導体基板1上にトンネル絶縁膜6、ポリシリコン膜(浮遊ゲート)7、インターポリ絶縁膜8、ポリシリコン膜2と順次形成した状態で、堆積したポリシリコン膜2の上に、スパッタ法を用いてチタン(Ti)膜3を5nm成膜するところまでは図1(a)と同様である。その後、図4(a)に示すように、例えば、スパッタ室中に酸素やオゾン、水等の酸素原子を有する酸化ガスを導入し、反応性スパッタ法を用いて酸化金属膜である酸化チタン膜4を自然酸化膜よりも厚く膜厚が3.5nm以上となるように成膜する。なお、図1(a)のチタンのスパッタ成膜の途中から酸化ガスを導入して金属膜/酸化金属膜の積層構造を形成するように膜中の酸素濃度を半導体基板1の垂直方向に自在に変えて図4(a)の構造を形成しても良い。

【0017】

その後、図4(b)に示すように酸化チタン膜4の上にスパッタ法もしくはCVD法を用いて電極となるタングステン(W)膜5を成膜する。その後の工程は図2(b)及び図3に示したのと同様であり、第1の実施形態と同様な構造を備えた図6に示したポリ・メタル電極構造を作製することが出来る。なお、本実施形態においても電極材料としてタングステンの代わりにモリブデンを用いてもかまわない。

【0018】

(第3の実施形態)

本実施形態においては、図7(a)に示すように半導体基板1上にトンネル絶縁膜6、ポリシリコン膜(浮遊ゲート)7、インターポリ絶縁膜8と順次形成した後、その上にTiN膜11を形成する。その後選択ゲートのコンタクト形成部の開口を形成し、その上から、第1または第2の実施形態と同様な手法でチタン膜3および酸化チタン膜4を開口部を含めコンフォーマルに形成する(図7(b))。その後タングステン膜5を成膜し、例えば900℃で10秒のRTAおよびゲート形状の加工のためのRIEを行うことにより図8に示すような構造が形成される。図8において図6と同一符号の部位は同一の構成を示す。本実施形態においてはRTAにより、図7(b)においてポリシリコン膜7に接したチタン膜3がシリサイド化され、図8(b)に示すようにTiシリサイド(TiSix)層10が形成される。なおここで、ポリシリコン膜7に接したチタン膜3の全てがシリサイド化されず、一部がチタンのまま残存することもある。また、ゲート形状の加工とRTAの順番は逆でもかまわない。

【0019】

図8(a)がビット線方向に垂直な断面を示し、図8(b)がワード線方向に垂直な断面を示す。図8(b)の左側に示したのがセル部で、右側に示したのが選択ゲート部である。本実施形態においては、図8(b)の右側の選択ゲートにおける部分C(ポリシリコン膜7/Tiシリサイド層10/酸化チタン膜4/タングステン膜5)についてポリ・メタル構造が形成される。なお、他の(TiN膜11/チタン膜3/酸化チタン膜4/タングステン膜5)の積層部分はいわゆるメタル・メタルゲート電極構造になっている。

【0020】

本実施形態においても、部分Cは拡散バリア性を有する熱安定性を備えた構造であり、コンタクト抵抗を低い値に確保することができる。また、メタル・メタルゲート電極構造の部分においてはタングステン膜5の比抵抗の低減効果により低抵抗化が図れる。なお、本実施形態においても電極材料としてタングステンの代わりにモリブデンを用いてもかまわない。

【0021】

以上説明したように上記実施形態により、ポリシリコン/電極タングステン(またはモリブデン)間に拡散防止性と熱安定性を兼ね備えた構造を備えたポリ・メタルゲート電極構造及び、メタル・メタルゲート電極構造を作製する事が可能となる。なお、上記実施形態においては、ポリ・メタルゲート電極及び、メタル・メタルゲート電極を例にして説明したが、ゲート電極以外の箇所にも上記実施形態の構造は適用可能である事は言うまでも無い。

【0022】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0023】

1 半導体基板、2 ポリシリコン膜、3 チタン膜、4 酸化チタン膜、5 タングステン膜、6 トンネル絶縁膜、7 ポリシリコン膜(浮遊ゲート)、8 インターポリ絶縁膜、9 素子分離層、10 Tiシリサイド層。

【特許請求の範囲】

【請求項1】

半導体基板の上に形成されたポリシリコン膜と、

前記ポリシリコン膜上に形成された、チタン、ジルコニウム、ハフニウム、バナジウム、ニオブ、タンタル、スカンジウム、イットリウム、クロムのうち少なくとも1種類の元素を含む金属のシリサイド膜と、

前記シリサイド膜の上に形成された前記金属の非晶質の酸化膜と、

前記酸化膜の上に形成されたタングステン或いはモリブデンを含む膜と、

を備えることを特徴とする半導体装置。

【請求項2】

半導体基板の上に形成されたポリシリコン膜と、

前記ポリシリコン膜上に形成された金属のシリサイド膜と、

前記シリサイド膜の上に形成された前記金属の酸化膜と、

前記酸化膜の上に形成されたタングステン或いはモリブデンを含む膜と、

を備えることを特徴とする半導体装置。

【請求項3】

前記金属は、チタン、ジルコニウム、ハフニウム、バナジウム、ニオブ、タンタル、スカンジウム、イットリウム、クロムのうち少なくとも1種類の元素を含む

ことを特徴とする請求項2に記載の半導体装置。

【請求項4】

前記半導体基板の上に、トンネル絶縁膜、浮遊ゲート膜、中間絶縁膜、ポリシリコン電極膜が順次形成されており、

前記ポリシリコン電極膜の上に、前記シリサイド膜、前記酸化膜、前記タングステン或いはモリブデンを含む膜が順次形成されている

ことを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

【請求項5】

前記半導体基板の上に、トンネル絶縁膜、ポリシリコン浮遊ゲート膜、中間絶縁膜が順次形成されており、前記中間絶縁膜の一部に前記ポリシリコン浮遊ゲート膜まで貫通する開口部が形成されており、

前記開口部における前記ポリシリコン浮遊ゲート膜の上に、前記シリサイド膜、前記酸化膜、前記タングステン或いはモリブデンを含む膜が順次形成されている

ことを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

【請求項1】

半導体基板の上に形成されたポリシリコン膜と、

前記ポリシリコン膜上に形成された、チタン、ジルコニウム、ハフニウム、バナジウム、ニオブ、タンタル、スカンジウム、イットリウム、クロムのうち少なくとも1種類の元素を含む金属のシリサイド膜と、

前記シリサイド膜の上に形成された前記金属の非晶質の酸化膜と、

前記酸化膜の上に形成されたタングステン或いはモリブデンを含む膜と、

を備えることを特徴とする半導体装置。

【請求項2】

半導体基板の上に形成されたポリシリコン膜と、

前記ポリシリコン膜上に形成された金属のシリサイド膜と、

前記シリサイド膜の上に形成された前記金属の酸化膜と、

前記酸化膜の上に形成されたタングステン或いはモリブデンを含む膜と、

を備えることを特徴とする半導体装置。

【請求項3】

前記金属は、チタン、ジルコニウム、ハフニウム、バナジウム、ニオブ、タンタル、スカンジウム、イットリウム、クロムのうち少なくとも1種類の元素を含む

ことを特徴とする請求項2に記載の半導体装置。

【請求項4】

前記半導体基板の上に、トンネル絶縁膜、浮遊ゲート膜、中間絶縁膜、ポリシリコン電極膜が順次形成されており、

前記ポリシリコン電極膜の上に、前記シリサイド膜、前記酸化膜、前記タングステン或いはモリブデンを含む膜が順次形成されている

ことを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

【請求項5】

前記半導体基板の上に、トンネル絶縁膜、ポリシリコン浮遊ゲート膜、中間絶縁膜が順次形成されており、前記中間絶縁膜の一部に前記ポリシリコン浮遊ゲート膜まで貫通する開口部が形成されており、

前記開口部における前記ポリシリコン浮遊ゲート膜の上に、前記シリサイド膜、前記酸化膜、前記タングステン或いはモリブデンを含む膜が順次形成されている

ことを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−38341(P2013−38341A)

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願番号】特願2011−175253(P2011−175253)

【出願日】平成23年8月10日(2011.8.10)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願日】平成23年8月10日(2011.8.10)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]