Fターム[4M104BB23]の内容

半導体の電極 (138,591) | 電極材料 (41,517) | 遷移金属のシリサイド (5,826) | PdSi (202)

Fターム[4M104BB23]に分類される特許

1 - 20 / 202

半導体装置および半導体装置の製造方法

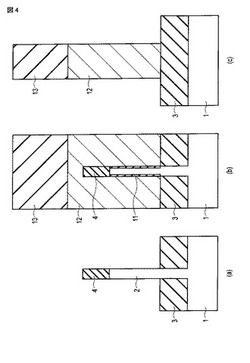

【課題】 寄生抵抗を低減可能な半導体装置を提供する。

【解決手段】 半導体装置は、第1半導体層の表面に沿って延びる突起(2)を有する第1半導体層(1)を含む。ゲート電極(12)は、突起の表面をゲート絶縁膜を挟んで覆う。第2半導体層(28, 45)は、突起のゲート電極により覆われる部分と別の部分の側面上に形成され、溝(31, 52)を有する。ソース/ドレイン領域(30, 46)は、第2半導体層内に形成される。シリサイド膜(33)は、溝内の表面を含め第2半導体層の表面を覆う。導電性のプラグ(37)は、シリサイド膜と接する。

(もっと読む)

半導体装置の製造方法

【課題】一定のドレイン電圧及びゲート電圧に対して得られるドレイン電流を増大することの出来る半導体装置の製造方法を提供する。

【解決手段】チャンネル領域と、ソース領域及びドレイン領域と、前記ソース領域及びドレイン領域にそれぞれ電気的に接続する合計二つの第1の電極と、前記チャンネル領域上にゲート絶縁膜を介して設けられた第2の電極とを備えた半導体装置の製造に際し、前記ゲート絶縁膜を、酸素の含有量を1ppb以下にした水素添加超純水にIPAを添加した洗浄液を用いて、酸素含有量1ppb以下の窒素雰囲気でしかも遮光した状態で表面の洗浄を行ない、かつ等方性酸化または窒化で形成することにより、前記チャンネル領域と前記ゲート絶縁膜との界面の平坦度を、前記ソース領域から前記ドレイン領域に向かう方向での長さ2nmにおけるピーク・トゥ・バレイ値が0.3nm以下となるようにするとともに、前記第1の電極から前記チャンネル領域までの抵抗率を4Ω・μm以下とした。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】SiC基板を用いて形成され、金属シリサイド膜と金属電極との密着性の向上する半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、炭化珪素と、炭化珪素上に形成され、第1の層、第1の層よりも低い炭素比率を有する第2の層を備える金属シリサイドと、金属シリサイド上に形成される金属電極を備え、第2の層が第1の層上に形成され、第2の層が金属電極に接し、第2の層中の金属シリサイドの平均粒径が、第1の層中の金属シリサイドの平均粒径よりも大きい。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ソース領域に3C−SiC構造のSiCを用いて低い寄生抵抗を実現し、高い性能を備える半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、第1のn型炭化珪素層と、第1のn型炭化珪素層よりもn型不物濃度の低い第2のn型炭化珪素層を有する半導体基板と、第2のn型炭化珪素層に形成される第1のp型不純物領域と、第2のn型炭化珪素層に形成される4H−SiC構造の第1のn型不純物領域と、第2のn型炭化珪素層に形成され、第1のn型不純物領域よりも深さの浅い3C−SiC構造の第2のn型不純物領域と、第2のn型炭化珪素層、第1のp型不純物領域、第1のn型不純物領域の表面にまたがるゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、第1のn型不純物領域上に形成され、底面部と側面部を備え、少なくとも側面部で第1のn型不純物領域との間に第2のn型不純物領域を挟む金属シリサイド層と、を備える。

(もっと読む)

半導体装置の製造方法

【課題】SiC基板上に形成されたデバイスに対して、低温の熱工程にて良好なオーミック特性を備える電極を実現する半導体装置の製造方法を提供する。

【解決手段】実施の形態の半導体装置の製造方法は、炭化珪素(SiC)で形成されるn型不純物領域上およびp型不純物領域上に金属シリサイド膜を形成し、n型不純物領域上の金属シリサイド膜中にリン(P)をイオン注入し、第1の熱処理を行い、p型不純物領域上の金属シリサイド膜中にアルミニウム(Al)をイオン注入し、第1の熱処理よりも低温の第2の熱処理を行う

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】高性能な不揮発性半導体記憶装置を提供する。

【解決手段】実施形態に係わる不揮発性半導体記憶装置は、第1の方向に積み重ねられる第1及び第2のメモリセルMCを有し、第2の方向に延びるフィン型積層構造Fin0〜Fin3と、フィン型積層構造Fin0〜Fin3の第2の方向の一端に接続され、第3の方向に延びる梁5とを備える。フィン型積層構造Fin0〜Fin3及び梁5は、それぞれ、第1の方向に積み重ねられる第1及び第2の半導体層2a,2bを備え、梁5は、第3の方向の一端に第1及び第2の半導体層2a,2bに対するコンタクト部を有し、かつ、梁5とフィン型積層構造Fin0〜Fin3の接続部からコンタクト部まで延びる低抵抗領域8を有する。

(もっと読む)

半導体装置とその製造方法

【課題】 単純で容易な実装手段によりMOSFETの閾値電圧を制御することが可能な半導体装置とその製造方法を提供する。

【解決手段】 一実施形態によれば、電界効果トランジスタは、STI(浅いトレンチ分離)を含んでいる半導体基板402と、p−FET401及びn−FET403と、p−FET401が形成される基板の窪み内のシリコン・ゲルマニウム層800と、n−FET部上とシリコン・ゲルマニウム層上に設けられた、ハフニウム化合物とレアアース化合物を含むゲート誘電体414, 432と、ゲート誘電体414, 432上にそれぞれ配置された互いに同じ材料を含むゲート電極416, 434とを具備している。

(もっと読む)

半導体装置及びその製造方法

【課題】微細配線を簡易に低抵抗化する。

【解決手段】実施形態に係わる半導体装置は、第1の方向に積み重ねられる第1乃至第3の半導体層3a,3b,3cを有し、第2の方向に延びるフィン型積層構造を有する。第1のレイヤーセレクトトランジスタTaは、第1のゲート電極10aを有し、第1の半導体層3aでノーマリオン状態である。第2のレイヤーセレクトトランジスタTbは、第2のゲート電極10bを有し、第2の半導体層3bでノーマリオン状態である。第3のレイヤーセレクトトランジスタTcは、第3のゲート電極10cを有し、第3の半導体層3cでノーマリオン状態である。第1の半導体層3aのうちの第1のゲート電極10aにより覆われた領域、第2の半導体層3bのうちの第2のゲート電極10bにより覆われた領域及び第3の半導体層3cのうちの第3のゲート電極10cにより覆われた領域は、それぞれ金属シリサイド化される。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】高耐圧及び高電流の動作が可能な半導体素子及びその製造方法を提案する。

【解決手段】内部に2次元電子ガス(2DEG)チャンネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50の方向に突出した多数のパターン化された突起61を備え、内部に窒化物半導体層30にオーミック接合されるオーミックパターン65を含むソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上に、且つ、パターン化された突起61を含んでソース電極60上の少なくとも一部に亘って形成された誘電層40と、一部が、誘電層40を間に置いてソース電極60のパターン化された突起61部分及びドレイン方向のエッジ部分の上部に形成されたゲート電極70と、を含んでなる。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフまたはエンハンスメントモード動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、該窒化物半導体層30にオミック接合されたドレイン電極50と、該ドレイン電極50と離間して配設され、該窒化物半導体層30にショットキー接合されたソース電極60と、該ドレイン電極50と該ソース電極60との間の窒化物半導体層30上及び該ソース電極60の少なくとも一部上にかけて形成された誘電層40と、該ドレイン電極50と離間して誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】FETのソース領域にショットキー電極を形成し、内部にオミックパターン電極を備え、ゲート電極をソース電極の一部領域と窒化物半導体領域の一部に形成することによって、ノーマリ−オフ動作すると共に高耐圧及び高電流で動作可能な、半導体素子及び製造方法を提供する。

【解決手段】内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間され、窒化物半導体層30にショットキー接合されるソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成された誘電層40と、ドレイン電極50と離間されるように誘電層40上に配設され、一部が誘電層40を挟んでソース電極60のドレイン方向のエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

窒化物半導体素子及びその製造方法

【課題】オン抵抗を低め、高電流で動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上部に配設され、内部に2次元電子ガスチャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間して配設され、窒化物半導体層30にショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成され、ドレイン電極50とソース電極60との間にリセスを形成する誘電層40と、ドレイン電極50と離間して誘電層40上及びリセスに配設され、一部が誘電層40を挟んでソース電極60のドレイン方向へのエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】応力等のストレスによる、素子の特性変動や、PN接合破壊などの信頼性劣化を防ぐことが可能な半導体装置、および半導体装置の製造方法を提供する。

【解決手段】サリサイド構造の半導体装置の高濃度ソース・ドレイン領域とゲート電極表面に形成される金属シリサイドを複数のアイランド状金属シリサイドからなる構成とする。これにより、全面に形成された金属シリサイド層よりも、シリコンと金属シリサイド層間の応力を緩和することができ、シリコンと金属シリサイド層間の応力等のストレスによる、素子の特性変動や、PN接合破壊などの信頼性劣化を防ぐことができる。

(もっと読む)

半導体装置の製造方法

【課題】微細化を達成するとともに、ゲート電極等の信頼性を確保する半導体装置の製造方法を提供する。

【解決手段】N型MISトランジスタ及びP型MISトランジスタのそれぞれのゲート形成領域において、N型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第1の金属含有膜F1を、P型MISトランジスタのゲート形成領域の凹部内に形成されたゲート絶縁膜F0上に第3の金属含有膜F3を形成し、第1の金属含有膜F1上及び第3の金属含有膜F3上に第2の金属含有膜F2を形成し、N型MISトランジスタのゲート絶縁膜F0に接する第1の金属含有膜F1の仕事関数がP型MISトランジスタのゲート絶縁膜F0に接する第3の金属含有膜F3の仕事関数よりも小さい。

(もっと読む)

半導体装置

【課題】集積回路の動作速度の向上に有利な技術を提供する。

【解決手段】n型トランジスタおよびp型トランジスタがシリコンの(551)面に形成された半導体装置において、前記n型トランジスタの拡散領域に接触するシリサイド層の厚さが前記p型トランジスタの拡散領域に接触するシリサイド層の厚さよりも薄い。

(もっと読む)

シリサイド化金属ゲートの形成のための方法

【課題】シリサイド化金属ゲートと、シリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物と、同ゲート構造物を製造する方法と、を提供する。

【解決手段】シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を提供する。詳しくは、広義に、第一の厚さを有する第一のシリサイド金属のシリサイド化金属ゲートと、隣接する第二の厚さを有する第二の金属のシリサイド化ソース領域およびドレイン領域とを含み、第二の厚さは第一の厚さより薄く、シリサイド化ソース領域およびドレイン領域は少なくともシリサイド化金属ゲートを含むゲート領域の端に位置合わせした半導体構造物を提供する。さらに、シリサイド化金属ゲートと、シリサイド化金属ゲートに接するシリサイド化ソース領域およびドレイン領域とを備える進歩したゲート構造物を製造する方法も提供する。

(もっと読む)

半導体装置

【課題】小数キャリアの注入量により少数キャリアを引き抜くための時間を適宜設定可能な構成とし、重金属拡散等の技術を利用することなく、低VF特性と、短Trr、低Qrrを、デバイスの使用目的及び態様等に応じて最適化する。

【解決手段】半導体基板31の上に形成された低不純物濃度の第1導電型である第1半導体層32と、第2導電型であるガードリング33と、第2導電型である複数の島状の第3半導体層35と、第1半導体層32の上面の一部の領域に形成された第1のバリアメタル45と、第1半導体層32及び複数の第3半導体層35の上に形成された第1のバリアメタル42の第1のバリアハイト41より高い第2バリアメタル43、45を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の劣化及び素子のばらつきを抑制しつつ、所望の閾値電圧を実現する。

【解決手段】実施形態による複数の閾値電圧を有する半導体装置500は、基板502と、第1の閾値電圧を有する基板上の第1のトランジスタ510と、第2の閾値電圧を有する基板上の第2のトランジスタ530とを具備する。第1のトランジスタは、基板の第1のチャネル領域上に形成された第1の界面層516と、第1の界面層上に形成された第1のゲート誘電体層518と、第1のゲート誘電体層上に形成された第1のゲート電極520,522とを具備する。第2のトランジスタは、基板の第2のチャネル領域上に形成された第2の界面層536と、第2の界面層上に形成された第2のゲート誘電体層538と、第2のゲート誘電体層上に形成された第2のゲート電極540,542とを具備する。第2の界面層は第1の界面層内になくかつSi、O及びNと異なる添加元素を有する。第1及び第2の閾値電圧は異なる。第1及び第2のトランジスタは同一の導電型である。

(もっと読む)

半導体装置

【課題】低いバリアハイトのバリアメタルを用いても伝導度変調を起させるように、別に第2のバリアメタル7を設けた構成とすることにより、ドリフト抵抗を低減し、ショットキーバリアダイオードの順方向電圧降下の低減を実現する。

【解決手段】ショットキーバリアダイオード1は、N−エピタキシャル層3と接合する第1のバリアメタル6はバリアハイトの低いメタルを用いるとともに、N−エピタキシャル及びP+ガードリング4にわたって上面にバリアハイトの高い第2のバリアメタル7を設ける構成としたので、微小電流領域は低VF特性のカーブとし、高電流領域ではP+ガードリング4からの小数キャリアの注入を積極的にさせて低VF特性のカーブとし、順方向電圧降下の低減する。

(もっと読む)

相補型金属酸化物半導体(CMOS)構造物

【課題】ゲート誘電体の上に複数のシリサイド金属ゲートが作製される相補型金属酸化物半導体集積化プロセスを提供する。

【解決手段】形成されるシリサイド金属ゲート相の変化を生じさせるポリSiゲートスタック高さの変化という欠点のないCMOSシリサイド金属ゲート集積化手法が提供される。集積化手法は、プロセスの複雑さ最小限に保ち、それによって、CMOSトランジスタの製造コストを増加させない。

(もっと読む)

1 - 20 / 202

[ Back to top ]