Fターム[5F140BF13]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極 (19,255) | 2層目材料 (3,048)

Fターム[5F140BF13]の下位に属するFターム

Fターム[5F140BF13]に分類される特許

1 - 20 / 77

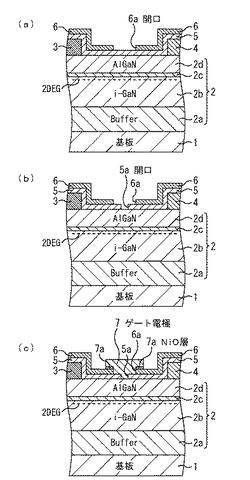

化合物半導体装置及びその製造方法

【課題】高電圧動作時においても電流コラプス現象を十分に抑制し、高耐圧及び高出力を実現する信頼性の高い化合物半導体装置を得る。

【解決手段】HEMTは、化合物半導体層2と、開口を有し、化合物半導体層2上を覆う保護膜と、開口を埋め込み、化合物半導体層2上に乗り上げる形状のゲート電極7とを有しており、保護膜は、酸素非含有の下層絶縁膜5と、酸素含有の上層絶縁膜6との積層構造を有しており、開口は、下層絶縁膜5に形成された第1の開口5aと、上層絶縁膜6に形成された第1の開口5aよりも幅広の第2の開口6aとが連通してなる。

(もっと読む)

半導体装置

【課題】RCATの電流駆動能力を向上させることが可能な半導体装置を提供する。

【解決手段】半導体基板11は、ゲート溝13を有している。拡散層12は、ゲート溝13の上部に対応する半導体基板11の表面領域に形成されている。ゲート絶縁膜14は、ゲート溝の壁面に形成されている。ゲート電極15は、ゲート溝13の内部及びゲート溝13の外部に形成されている。圧縮応力を有する膜16は、ゲート溝13の外部のゲート電極15の全面に形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】ダミーゲート電極の除去により形成されたゲート溝へのゲート電極材料の埋め込み性を改善することにより、適切な閾値電圧を持つ電界効果型トランジスタを備えた半導体装置を容易に実現できるようにする。

【解決手段】ゲート電極111bは、それぞれ金属又は導電性金属化合物からなる第1導電膜108b、第2導電膜109b及び第3導電膜110bが下から順に形成された積層構造を有し、ゲート電極111aは、第2導電膜109a及び第3導電膜110aが下から順に形成された積層構造を有する。第1導電膜108bの仕事関数と第2導電膜109a、109bの仕事関数とは異なっている。第1導電膜108bは板状に形成されており、第2導電膜109a、109bは凹形状に形成されている。

(もっと読む)

高有効仕事関数で電極を堆積する方法

【課題】半導体処理の方法が提供される。

【解決手段】いくつかの実施形態によれば、高い有効仕事関数を有する電極が形成される。この電極は、トランジスタのゲート電極であってもよく、導電材料の第1の層を堆積し、第1の層を水素含有ガスに露出し、第1の層に導電材料の第2の層を堆積することにより、high−kゲート誘電体に形成されてもよい。第1の層は、基板がプラズマ又はプラズマ発生ラジカルに露出されないプラズマ無しプロセス(non−plasma process)を用いて堆積される。第1の層が露出される水素含有ガスは、励起された水素種を含んでもよく、これは水素含有プラズマの一つであってもよく、水素含有ラジカルであってもよい。第2の層を堆積する前に、第1の層もまた、酸素に露出されてもよい。ゲートスタックのゲート電極の仕事関数は、いくつかの実施形態において約5eV又はそれ以上であってもよい。

(もっと読む)

ナノ多孔質薄膜、およびその製造方法

【課題】細孔の周囲を囲む細孔壁の材料が膜厚方向に任意に制御されたナノ多孔質薄膜、およびその製造方法を提供することにある。

【解決手段】本発明によるナノ多孔質構造を有するナノ多孔質薄膜は、膜厚方向に沿って複数の層領域を有し、前記複数の層領域は、第一の細孔を有する第一の層領域と第二の細孔を有する第二の層領域とを含み、前記第一の細孔と前記第二の細孔は貫通し、前記第一の層領域と前記第二の層領域とを構成する材料が異なることを特徴とする。

(もっと読む)

半導体集積回路装置の製造方法

【課題】高誘電率ゲート絶縁膜を用いたCMIS型半導体集積回路において、短チャネル長、且つ狭チャネル幅のデバイス領域では、ソースドレイン領域の活性化アニールによって、高誘電率ゲート絶縁膜とシリコン系基板部との界面膜であるILの膜厚が増加することによって、閾値電圧の絶対値が増加するという問題がある。

【解決手段】本願の一つの発明は、MISFETを有する半導体集積回路装置の製造方法において、MISFETのゲートスタック及びその周辺構造を形成した後、半導体基板表面を酸素吸収膜で覆い、その状態でソースドレインの不純物を活性化するためのアニールを実行し、その後、当該酸素吸収膜を除去するものである。

(もっと読む)

半導体装置およびその製造方法

【課題】素子分離用ゲート電極のみのしきい値電圧を高くすることができ、素子分離用ゲート電極の底部にチャネルが形成されない半導体装置を提供する。

【解決手段】半導体基板1に形成された複数の活性領域と、これら活性領域同士を区画する素子分離領域と、活性領域内を複数の素子領域に区画する第1素子分離用トレンチ32Aと、隣接する第1素子分離用トレンチ32A間に設けられ、第1素子分離用トレンチ32Aの深さよりも浅く形成されたゲートトレンチ31Aと、絶縁膜25を介して第1素子分離用トレンチ32A内に形成された素子分離用電極32と、ゲート絶縁膜26Aを介してゲートトレンチ31A内に形成されたゲート電極31と、を具備してなり、素子分離用電極32底部に成膜されている絶縁膜25の膜厚が、ゲート電極31の底部に成膜されているゲート絶縁膜26Aの膜厚よりも厚いことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】Geをチャネル材料に用いても、素子特性の劣化を抑制することを可能にする。

【解決手段】Geを含むp型半導体領域上にゲート絶縁膜を形成する工程と、前記ゲート絶縁膜上にゲート電極を形成する工程と、前記半導体領域の、前記ゲート電極の両側に位置する第1および第2領域に、有機金属錯体および酸化剤を交互に供給して金属酸化物を堆積する工程と、前記金属酸化物の上に金属膜を堆積する工程と、熱処理を行うことにより、前記半導体領域および前記金属酸化物と、前記金属膜とを反応させて前記第1および第2領域に金属半導体化合物層を形成するとともに前記金属半導体化合物層と前記半導体領域との界面に金属偏析層を形成する工程と、を備えている。

(もっと読む)

半導体装置、及びその製造方法

【課題】高品質な半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板と、基板上に形成される半導体領域、半導体領域内に形成され、互いに分離されているソース領域及びドレイン領域、半導体領域内に形成され、ソース領域及びドレイン領域を分離するチャネル領域、チャネル領域上に形成され、1×1019atoms/cm2よりも大きいピーク濃度で、Si、O、またはNとは異なる少なくとも一つの要素を有する界面酸化層、及び界面酸化層上に形成され、実質的に界面酸化層に隣接する深さでhigh―k/界面酸化層接合面を有するhigh―k絶縁層を有するMOS(metal-oxide-semiconductor)トランジスタを備え、少なくとも一つの要素のピーク濃度の少なくとも一つの深さは、実質的にhigh―k/界面酸化層接合面よりも下に位置する。

(もっと読む)

半導体装置及びその製造方法

【課題】金属電極と該金属電極の上に形成されたシリコン電極とを有するゲート電極を備えた電界効果型トランジスタを実現する際に、金属電極とシリコン電極との界面に生じる界面抵抗を低減できるようにする。

【解決手段】半導体装置は、半導体基板100における第1の活性領域103aに形成されたP型の電界効果型トランジスタを備えている。第1の電界効果型トランジスタは、第1の活性領域103aの上に形成された第1のゲート絶縁膜106aと、第1のゲート絶縁膜106aの上に形成された第1のゲート電極115aとを有している。第1のゲート電極115aは、第1のゲート絶縁膜106aの上に形成された第1の金属電極107aと、該第1の金属電極107aの上に形成された第1の界面層110aと、該第1の界面層110aの上に形成された第1のシリコン電極111aとを有している。

(もっと読む)

DRAMアクセス・トランジスタ及び形成方法

【課題】自己整列リセス・ゲート構造及び形成方法の提供。

【解決手段】最初に,絶縁用のフィールド酸化物領域20を半導体基板10内に形成する。半導体基板の上に形成された絶縁層内に複数のコラムを画定し,それに続いて,薄い犠牲酸化物層を半導体基板の露出領域の上に形成するが,フィールド酸化物領域の上には形成しない。次に,各コラムの側壁上,並びに犠牲酸化物層及びフィールド酸化物領域の一部分の上に誘電体を設ける。第1エッチングを行い,それにより,半導体基板内に第1組のトレンチを,またフィールド酸化物領域内に複数のリセスを形成する。第2エッチングを行い,それにより,コラムの側壁上に残っている誘電体残留部を除去し,かつ第2組のトレンチを形成する。次に,第2組のトレンチ内及びリセス内にポリシリコンを堆積させ,それにより,リセス導電性ゲートを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化が進んだ場合であっても、適切なしきい値電圧を有するpチャネルMOSFETを含む半導体装置を製造する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板101上に、SiO2またはSiONを含む第1ゲート絶縁層104を形成する第1ゲート絶縁層形成ステップと、第1ゲート絶縁層104上に、金属酸化物を含む第2ゲート絶縁層105を形成する第2ゲート絶縁層形成ステップと、第2ゲート絶縁層105上に、金属を含む第1電極106aを形成する第1電極形成ステップと、形成された積層構造に、複数回のミリセカンドアニール処理を行うことで、第2ゲート絶縁層105および第1電極106aの少なくとも一方に含まれる4族、5族または13族の元素を、第1ゲート絶縁層104と第2ゲート絶縁層105との界面に拡散させるアニールステップとを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】接合リーク電流が低減されるとともに、セル容量への書き込み・読み出しに十分な電流駆動能力を確保することが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板1に形成された複数の埋め込みゲート型MOSトランジスタ2を有し、半導体基板1には素子分離領域と活性領域とが形成されており、ゲートトレンチの内部に形成され、少なくとも一部がワード線として設けられるとともに、その他の残部が、活性領域を複数の素子領域に分離する素子分離として設けられる埋め込みゲート電極31A、31Bと、ソース・ドレイン拡散層15、45とが備えられ、埋め込みゲート電極31A、31Bは、上部電極31aと下部電極31bとの積層構造とされ、且つ、半導体基板1の上面側のソース・ドレイン拡散層15、45側に配置される上部電極31aが、下部電極31bに比べて、仕事関数の低いゲート材料からなる。

(もっと読む)

半導体装置およびその製造方法

【課題】適切な仕事関数を有する金属ゲート電極を備え、トランジスタ特性のばらつきが抑えられた半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1001と、半導体基板1001内に形成された第1導電型の第1の活性領域1003と、第1の活性領域1003上に形成された第1のゲート絶縁膜1030aと第1のゲート電極1032aとを有し、第1の活性領域1003上に形成された第1チャネル型の第1のMISFET1050とを備える。第1のゲート電極1032aは、第1のゲート絶縁膜1030a上に形成され、金属原子を含む第1の下部ゲート電極1011aと、炭素の単体を含む材料、または分子中に炭素を含む材料からなる第1の酸化防止膜1012aと、第1の上部ゲート電極1013aとを有している。

(もっと読む)

積層膜の形成方法

【課題】 各膜の組成が異なる積層膜を、極めて効率よく、しかも酸化等の不都合が生じることなく形成することができる積層膜の形成方法を提供すること。

【解決手段】 処理室内に基板1を配置し、処理室に、少なくとも、金属カルボニルを含有する原料を含む成膜原料を導入し、CVDにより基板1上に金属カルボニル中の金属を含む複数の膜6a、6bを含む積層膜を形成する積層膜の形成方法であって、上記積層膜に含まれる膜は、同一処理室内で、原料種および/または成膜条件を異ならせて連続成膜され、上記膜の組成が異なる積層膜を形成する。

(もっと読む)

自己整合コンタクト

トランジスタは、基板と、基板上の一対のスペーサと、基板上且つスペーサ対間のゲート誘電体層と、ゲート誘電体層上且つスペーサ対間のゲート電極層と、ゲート電極層上且つスペーサ対間の絶縁キャップ層と、スペーサ対に隣接する一対の拡散領域とを有する。絶縁キャップ層は、ゲートにセルフアラインされるエッチング停止構造を形成し、コンタクトエッチングがゲート電極を露出させることを防止し、それにより、ゲートとコンタクトとの間の短絡を防止する。絶縁キャップ層は、セルフアラインコンタクトを実現し、パターニング限界に対して一層ロバストな、より幅広なコンタクトを最初にパターニングすることを可能にする。  (もっと読む)

(もっと読む)

FinFETとトライゲートデバイス用のラップアラウンド型コンタクト

サブストレートとサブストレートの上に形成された半導体ボディを有する半導体デバイスである。半導体ボディはソース領域とドレイン領域を有している。ソース領域、ドレイン領域、またはその組み合わせは、第一の側面、第二の側面、及び上面を有している。第一の側面は第二の側面と向かい合っており、上面は底面と向かい合っている。ソース領域、ドレイン領域、またはその組み合わせは、実質的に全ての第一の側面の上に、実質的に全ての第二の側面の上に、そして上面の上に、形成されたメタル層を有している。  (もっと読む)

(もっと読む)

半導体装置

【課題】 半導体装置に関し、ソース・ドレイン領域を実効的に埋込Si混晶層で構成する際の電気的特性を向上する

【解決手段】 一導電型シリコン基体と、一導電型シリコン基体上に設けたゲート絶縁膜と、ゲート絶縁膜の上に設けたゲート電極とゲート電極の両側の一導電型シリコン基体に設けた逆導電型エクステンション領域と、逆導電型エクステンション領域に接するとともに、一導電型シリコン基体に形成された凹部に埋め込まれた逆導電型Si混晶層とを備えた半導体装置であって、逆導電型Si混晶層が、第1不純物濃度Si混晶層/第2不純物濃度Si混晶層/第3不純物濃度Si混晶層を有し、第2不純物濃度を第1不純物濃度及び第3不純物濃度よりも高くする。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、最適な仕事関数を有するメタルゲート電極を持つ半導体装置及びその製造方法に関する。

【解決手段】n チャネルMIS トランジスタを含む半導体装置であり、n チャネルMIS トランジスタは、基板上に形成されたp 型半導体領域、p 型半導体領域に形成されたソース領域102及びドレイン領域104、ソース領域102及びドレイン領域104間のp 型半導体領域上に形成されたゲート絶縁膜106、ゲート絶縁膜106上に形成された金属層108及び化合物層110からなる積層構造を持つゲート電極を有する。金属層108は2 nm未満の厚さ及び4.3 eV以下の仕事関数を有し、化合物層110は4.4 eVを越える仕事関数を有しかつAl及び金属層108とは異なる金属を含んでいる。

(もっと読む)

高kゲート誘電体のための、不純物酸素を捕捉する半導体構造および該構造を形成する方法(高kゲート誘電体のための捕捉金属スタック)

【課題】CMOS集積過程での高温処理の後であっても一定の閾値電圧を維持する高kゲート誘電体の提供。

【解決手段】高kゲート誘電体30と、下部金属層40、捕捉金属層50、および上部金属層60を含む金属ゲート構造とのスタックを提供する。該捕捉金属層は、次の2つの基準、1)Si+2/yMxOy→2x/yM+SiO2の反応によるギブス自由エネルギの変化が正である金属(M)であること、2)酸化物形成に対する酸素原子あたりのギブス自由エネルギが、下部金属層の金属および上部金属層の金属より大きな負である金属であること、を満たす。これらの基準を満たす捕捉金属層は、酸素原子がゲート電極を通って高kゲート誘電体に向け拡散するときに該酸素原子を捕捉する。さらに、該捕捉金属層は、高kゲート誘電体の下の酸化ケイ素界面層の厚さを遠隔から低減する。この結果、ゲート誘電体全体の等価酸化膜厚(EOT)の変動が抑制される。

(もっと読む)

1 - 20 / 77

[ Back to top ]