Fターム[5F140CB00]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 素子分離構造 (5,334)

Fターム[5F140CB00]の下位に属するFターム

フィールド絶縁膜 (844)

チャネルストッパ (158)

溝掘り構造 (2,469)

電極による分離 (23)

ガードリング (41)

ウェル (1,381)

他の領域と素子分離領域との関係 (377)

Fターム[5F140CB00]に分類される特許

1 - 20 / 41

半導体装置の製造方法、半導体装置

【課題】SiCが用いられる半導体層中において、簡易な工程で再現性よく埋め込み絶縁層を形成する。

【解決手段】単結晶のSiC12の表面の温度を局所的に急激に上昇させ、その後で急激に冷却することによって、単結晶を局所的に非晶質化層30を形成することができる。この非晶質層30は、元の単結晶SiCの導電型や抵抗率に関わらず、高抵抗層(絶縁層)となる。このため、こうした非晶質層を埋め込み絶縁層と同様に使用することができる。このためには、(1)レーザー光を効率的に吸収する層100を局所的に半導体層の上に形成してからレーザー光を照射する、(2)レーザー光を局所的に半導体層に照射する、という2つの手段のいずれかを用いることができる。

(もっと読む)

半導体装置

【課題】チャネル形成領域に対しトランジスタの電流駆動能力を向上させる方向に応力をかけ、さらに電流駆動能力が向上し、性能が向上された半導体装置を提供する。

【解決手段】半導体基板1aの活性領域1cが素子分離絶縁膜2で区画され、チャネル形成領域、ゲート絶縁膜、ゲート電極8a、ソース・ドレイン領域及び被覆応力膜を有するNTrを有し、ソース・ドレイン領域の両側部に位置する素子分離絶縁膜2aの表面は、ソース・ドレイン領域の表面より低い位置に形成されており、ゲート電極8a、活性領域1c、及び表面がソース・ドレイン領域の表面より低い位置に形成された素子分離絶縁膜2aを被覆して、チャネル形成領域に対し引張応力を印加する被覆応力膜が形成されている構成とする。

(もっと読む)

半導体装置

【課題】チャネル形成領域に対しトランジスタの電流駆動能力を向上させる方向に応力をかけ、さらに電流駆動能力が向上し、性能が向上された半導体装置を提供する。

【解決手段】半導体基板(1a,1b)の活性領域(1c,1d)が素子分離絶縁膜(2,6a)で区画され、チャネル形成領域、ゲート絶縁膜、ゲート電極(8a,8b)、ソース・ドレイン領域及び被覆応力膜を有するNTrとPTrを有し、活性領域におけるゲート長方向が<100>方向であり、素子分離絶縁膜としてNTrにおけるソース・ドレイン領域の両端部に第1の引張応力膜6aが形成され、ソース・ドレイン領域の両端部以外に第1の圧縮応力膜2が形成され、PTrの素子分離絶縁膜は第1の圧縮応力膜2が形成され、被覆応力膜としてNTrに第2の引張応力膜が形成され、PTrに第2の圧縮応力膜が形成されている構成とする。

(もっと読む)

半導体装置およびその製造方法

【課題】シリコンエピタキシャル層の支えの喪失を防止した、局所SOI構造の形成方法の提供。

【解決手段】SiGe混晶層31SG1〜31SG4とシリコンエピタキシャル層31ES1,31ES2,31ES3および31ES4が積層された構造において、

それぞれ、Nウェル31NW及びPウェル31PWがSiGe混晶層31SG1〜31SG4側に突き出る構造を形成し、SiGe混晶層31SG1〜31SG4をエッチングにより除去する際に、支えとなるようにする。

(もっと読む)

半導体素子、半導体素子の製造方法、およびトランジスタ回路

【課題】高電子移動度トランジスタの耐圧を高くする。

【解決手段】第1の高電子移動度トランジスタ4と、負の閾値電圧を有する第2の高電子移動度トランジスタ6とを有し、第2の高電子移動度トランジスタ6のソースS2は、第1の高電子移動度トランジスタ4のゲートG1に接続され、第2の高電子移動度トランジスタ6のゲートG2は、第1の高電子移動度トランジスタ4のソースS1に接続されている。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】バッファ層の結晶成長時に高抵抗化の不純物をドーピングすることなく上層の化合物半導体の結晶品質を保持するも、バッファ層を高抵抗化してオフリーク電流を確実に抑制し、信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2の裏面から、化合物半導体積層構造2の少なくともバッファ層2aに不純物、例えばFe,C,B,Ti,Crのうちから選ばれた少なくとも1種類を導入し、バッファ層2aの抵抗値を高くする。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】ゲート電極の電界集中を緩和して耐圧の更なる向上を実現することに加え、デバイス動作速度を向上させ、アバランシェ耐量が大きく、サージに対して強く、例えばインバータ回路等に適用する場合に外部のダイオードを接続することを要せず、ホールが発生しても安定動作を得ることができる信頼性の高い高耐圧の化合物半導体装置を実現する。

【解決手段】化合物半導体積層構造2に形成された電極用リセス2Cを、ゲート絶縁膜6を介して電極材料で埋め込むようにゲート電極7を形成すると共に、化合物半導体積層構造2に形成されたフィールドプレート用リセス2Dをp型半導体で埋め込み、化合物半導体積層構造2とp型半導体層8aで接触するフィールドプレート8を形成する。

(もっと読む)

半導体装置

【課題】半導体基板に向かって流れ込む回生電流又は寄生バイポーラトランジスタのオン電流を、チップサイズを増大させることなく低減できるLDMOSトランジスタの実現が課題となる。

【解決手段】N+型ドレイン層13等が形成されたN型エピタキシャル層5からなるN型層5aを、N型エピタキシャル層5の表面からN+型埋め込み層2まで延在するP型ドレイン分離層6で取り囲む。P型ドレイン分離層6とP型素子分離層3に囲まれたN型エピタキシャル層5からなるN型層5bにその表面から内部に延在するP型コレクタ層7を形成する。これにより第1導電型のドレイン分離層6をエミッタ、前記第2導電型の分離層5bをベース、前記コレクタ層7をコレクタとする寄生バイポーラトランジスタを形成しサージ電流を接地ラインに流す。

(もっと読む)

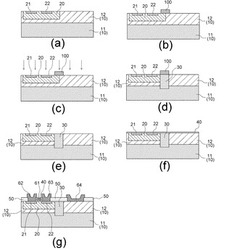

歪チャネルを有するMOSトランジスタを製造する方法

【課題】歪チャネルを有するMOS トランジスタを製造するための比較的簡単な方法を提供する。

【解決手段】歪チャネルを有するMOS トランジスタ(M) を製造する方法は、(a) 半導体基板(10)の表面に、ソース領域及びドレイン領域とMOS トランジスタを囲む絶縁領域(22)に部分的に延びる絶縁された犠牲ゲートとを備えたMOS トランジスタを形成するステップと、(b) 犠牲ゲートの上面と略同一の高さの上面を有する絶縁層を形成するステップと、(c) 犠牲ゲートを除去するステップと、(d) 露出した絶縁領域(22)の少なくとも上部分をエッチングしてトレンチを形成するステップと、(e) 半導体基板(10)を歪ませることが可能な材料(24)をトレンチに充填するステップと、(f) 犠牲ゲートの除去によって空いた空間にMOS トランジスタの絶縁ゲート(12)を形成するステップとを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】低容量且つ高温特性が良好な素子分離領域を有する高速なMIS電界効果トランジスタを提供する。

【解決手段】半導体基板1にウエル領域2が設けられ、ウエル領域2内には上部、下部及び側面にシリコン酸化膜3を有し、内部が空孔4に形成されたトレンチ素子分離領域が選択的に設けられ、トレンチ素子分離領域により画定されたウエル領域2が設けられた半導体基板1上にゲート酸化膜9を介してゲート電極10が設けられ、ゲート電極10の側壁にサイドウォール11が設けられ、ウエル領域2が設けられた半導体基板1には、ゲート電極10に自己整合して低濃度のソースドレイン領域(6、7)及びサイドウォール11に自己整合して高濃度のソースドレイン領域(5、8)が設けられ、高濃度のソースドレイン領域にはそれぞれバリアメタル14を有する導電プラグ15を介してバリアメタル17を有する配線18が接続されている構造からなるMIS電界効果トランジスタ。

(もっと読む)

誘電体分離型半導体集積装置、及び半導体集積装置の製造方法

【課題】微細なMOS素子と共存する。

【解決手段】支持基板5と、埋込シリコン酸化膜6と、第1高濃度不純物層9及び低不純物濃度層とからなる活性層15、とで構成されるSOI基板を適用した誘電体分離型半導体集積装置10において、高耐圧半導体素子形成領域を囲んで形成される素子分離領域は、多重溝100と、多重溝の側壁に設けた第1酸化膜105と、第1酸化膜と隣接して多重溝側壁に沿って形成された第2高濃度不純物層110と、第2高濃度不純物層の略上部にLOCOS酸化膜50を介して配設された低抵抗層P2と、前記低抵抗層に積層された第2酸化膜70,75,80と、を備えて構成され、低抵抗層は、第2高濃度不純物層、あるいはドレイン電極と略同電位であり、第2酸化膜の表面でエミッタ電極が前記高耐圧半導体素子形成領域から隣接領域へ引き出されている。

(もっと読む)

半導体装置

【課題】オン耐圧および電流能力を維持し、オフ耐圧を向上させる半導体装置を提供する。

【解決手段】高耐圧横型MOSFET20では、n++ドレイン領域7は、n-ドリフト領域3に直線状に延びている。n+バッファ領域6は、n++ドレイン領域7を囲んでいる。ゲート電極11、n++ソース領域5およびpベース領域4は、n+バッファ領域6側からこの順に、n+バッファ領域6を挟むように、ストライプ形状に形成されている。n半導体領域8は、n+バッファ領域6の終端コーナー部を覆うように形成されている。また、n半導体領域8は、n-ドリフト領域3の深さ方向に、n+バッファ領域6の下の領域を占めるように形成されている。高耐圧横型MOSFET20は、分離トレンチ14および分離シリコン領域により、高耐圧横型MOSFET20に隣接するデバイスと電気的に分離されている。

(もっと読む)

半導体装置の製造方法

【課題】所望のシリサイド膜を形成しつつ、半導体装置の生産性を向上することが可能な半導体装置の製造方法を提供する。

【解決手段】第1の圧力の不活性雰囲気中において、第1の加熱温度の第1の加熱処理により、ソース・ドレイン拡散層のシリコンとソース・ドレイン拡散層上の金属とを反応させて、ソース・ドレイン拡散層の上部をシリサイド化してシリサイド膜を形成し、第2の圧力の酸化性雰囲気において、第2の加熱温度の第2の加熱処理により、素子分離絶縁膜の上の金属膜の少なくとも表面を選択的に酸化して、金属酸化膜を形成し、第1の加熱温度および第2の加熱温度よりも高い第3の加熱温度の第3の加熱処理により、シリサイド膜のシリコンの濃度を増加し、素子分離絶縁膜上の金属酸化膜および金属膜の未反応部分を選択的に除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、分離領域の形成領域を狭めつつ、MOSトランジスタの動作耐圧を向上させ難いという問題があった。

【解決手段】本発明の半導体装置では、P型の埋込層9が這い上がり、P型の拡散層12が這い下がり、両拡散層9、12が連結することで、MOSトランジスタ3のバックゲート領域が構成される。この構造により、分離領域1のP型の拡散層13の横方向拡散幅が抑制され、分離領域の形成領域及びMOSトランジスタのデバイスサイズが低減される。その一方で、バックゲート領域での寄生抵抗が低減し、MOSトランジスタの動作耐圧が向上する。

(もっと読む)

半導体装置、半導体装置の製造方法およびスイッチ回路

【課題】トランジスタのリーク電流の低減。

【解決手段】半導体材料の表面に沿って互いに隣接する、シリサイド化される金属を含有する複数の電気素子要素と、複数の電気素子要素を覆い、電気素子要素に含まれる金属が実質的にシリサイド化しない温度で薄膜形成したシリコンを含む保護絶縁膜と、を備える半導体装置が提供される。上記半導体装置において、保護絶縁膜は、シリコンおよび窒素を含有できる。保護絶縁膜は、260℃以下の温度で薄膜形成した窒化シリコン膜であってよく、好ましくは100℃以下の温度で薄膜形成した窒化シリコン膜である。

(もっと読む)

半導体装置

【課題】起動回路と周辺回路とを併せて集積化し得る半導体装置を提供する。

【解決手段】領域411においては、素子分離領域により規定されるドレイン領域121にボディ領域が形成され、ボディ領域にN型のソース領域が形成される。ドレイン領域121とN型のソース領域との間に第1のゲート電極20が配置される。素子分離領域は開口部133が形成されたループ状部と、開口部133を介してドレイン領域121に接続された延在領域122を規定する部分とを備える。延在領域122に、N型のソース引出領域が形成される。内部回路412においては、ドレイン領域121にP型のボディ領域が形成され、P型のボディ領域にN型のソース領域が形成され、ドレイン領域121とN型のソース領域との間に第2のゲート電極331が形成される。

(もっと読む)

半導体装置

【課題】従来の半導体装置では、製造条件のばらつきにより、保護素子よりも先に被保護素子がオン動作し、過電圧から被保護素子が保護し難いという問題があった。

【解決手段】本発明の半導体装置では、保護素子1とMOSトランジスタ15との構成の一部を共用する。そして、保護素子1を構成するN型の拡散層8とMOSトランジスタ15を構成するN型の拡散層19を同一工程で形成するが、N型の拡散層8の拡散幅W3が、N型の拡散層19の拡散幅W4よりも広くなる。この構造により、出力端子に過電圧が印加された際に、MOSトランジスタ15よりも保護素子1の方が先にオン動作し、アバランシェ電流からMOSトランジスタ15が保護される。

(もっと読む)

半導体装置及びその製造方法

【課題】STIの圧縮応力を減少し、チャネル方向とチャネル幅方向の応力を印加することにより、駆動能力を増大したCMOS半導体装置とその製造方法を提供する。

【解決手段】半導体装置は、NMOSFET用活性領域AR1、PMOSFET用活性領域AR2を画定する素子分離溝STと、素子分離溝の下部のみを埋め、その上に凹部を画定する酸化シリコン膜OXと、NMOSFET領域AR1に形成されたNMOSFETと、PMOSFET領域AR2に形成されたPMOSFETと、NMOSFET構造を覆い、NMOSFET用活性領域AR1の周囲における凹部上及びPMOSFET用活性領域AR2のゲート幅方向外側における凹部上に延在して形成された引張応力膜TSFと、PMOSFET構造を覆い、PMOSFET用活性領域AR2のチャネル長方向外側における凹部上に延在して形成された圧縮応力膜CSFとを有する。

(もっと読む)

半導体集積回路

【課題】半導体集積回路のソフトエラーの発生を抑制する技術を提供する。

【解決手段】半導体集積回路装置を構成するMISFET(2)を以下のように構成する。そのMISFET(2)は、第一導電型のドレイン拡散層(4)とソース拡散層(3)、およびゲート電極(5)、第一導電型と反対導電型の第二導電型の基板(8)/ウエル(9)から構成される。そして、そのMISFET(2)において、ドレイン拡散層(4)の周囲少なくとも2辺の素子分離面に対向する位置に、第一導電型と同導電型の第一の拡散層(11)(12)を、素子分離絶縁膜(6)を介して所定間隔で2箇所以上設け、ソース拡散層近傍またはソース拡散層に接触するように、第二導電型の第二の拡散層(16)を設ける。

(もっと読む)

半導体装置とその製造方法

【課題】 ヘテロ接合を有する半導体装置において、素子領域から電流がリークすることを抑制する。

【解決手段】 半導体装置100は、バンドギャップを異にする窒化物半導体層6、10が積層されている半導体積層部11を有しており、半導体積層部11が素子領域100aと素子領域100aの周囲に形成されている素子分離領域100bを備えている。素子領域100aは、素子分離領域100bにより他の領域から絶縁されている。半導体装置100は、素子領域100a内の半導体積層部11の表面に、主電極に接続する一対の電極群24,16を形成する電極群形成工程と、素子分離領域100b内の半導体積層部11の表面に、スパッタ法を用いてスパッタ層12を形成するスパッタ工程を備えている。

(もっと読む)

1 - 20 / 41

[ Back to top ]