Fターム[5F140CB01]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | 素子分離構造 (5,334) | フィールド絶縁膜 (844)

Fターム[5F140CB01]に分類される特許

1 - 20 / 844

半導体装置の製造方法

半導体装置の製造方法

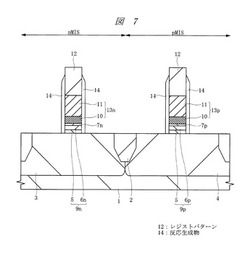

【課題】半導体装置の信頼性を向上させることができる技術を提供する。特に、ゲート電極をメタル材料で構成する電界効果トランジスタを有する半導体装置において、安定した動作特性を得ることのできる技術を提供する。

【解決手段】レジストパターン12をマスクとしたドライエッチングにより、ゲート電極13nまたはゲート電極13pを形成した後、酸素および水素を含むプラズマ雰囲気中においてアッシング処理を施すことにより、レジストパターン12を除去し、ゲート電極13nまたはゲート電極13pの側面に付着した反応生成物14を酸化する。その後、洗浄処理を施して、反応生成物14を除去する。

(もっと読む)

半導体装置の製造方法

【課題】特性の良好な半導体装置を製造する。

【解決手段】本発明は、MISFETを有する半導体装置の製造方法であって、(a)半導体基板の上方に、シリコン膜と絶縁膜CPとの積層膜を形成する工程と、(b)積層膜をパターニングすることによりゲート電極GE1とその上部に配置された絶縁膜CPとの積層体を形成する工程と、(c)積層体の側壁にサイドウォール膜SWを形成する工程と、(d)絶縁膜CPを除去する工程と、(e)サイドウォール膜SWおよびゲート電極GE1の合成体の両側の半導体基板中および前記ゲート電極GE1中にヒ素(As)を注入する工程と、を有する。かかる製法によれば、ヒ素(As)のイオン注入によるゲート電極GE1の体積膨張、特に、横方向への膨らみを低減することができ、ゲート電極とコンタクトプラグとの短絡を低減できる。

(もっと読む)

横型素子を有する半導体装置

【課題】耐圧バラツキを抑制し、歩留りを向上させることが可能となる横型素子を有する半導体装置を提供する。

【解決手段】横型FWDなどの横型素子に備えられるSRFP21について、の不純物濃度を1×1018cm-3以上となるようにする。このように、横型FWD7などに備えられるSRFP21について、の不純物濃度を1×1018cm-3以上とすることにより、耐圧バラツキを抑制することが可能となり、的確に目標とする耐圧を得ることができる製品とすることが可能になる。したがって、製品の歩留りを向上させることが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】スイッチング素子として利用される高耐圧かつ低オン抵抗な半導体装置を安価に提供する。

【解決手段】第1導電型の不純物を含有し、互いに対向する第1の主面と第2の主面とを有する半導体基板と、第2導電型の不純物を第1の濃度で含有し、前記半導体基板の前記第1の主面に露出するように形成された第1の拡散領域と、前記第2導電型の不純物を前記第1の濃度よりも高い第2の濃度で含有し、前記半導体基板の前記第1の主面に露出するように前記第1の拡散領域の側方に形成された第2の拡散領域と、前記第1導電型の不純物を含有し、前記半導体基板の前記第1の主面に露出するように前記第1の拡散領域の上方に形成された第3の拡散領域と、前記第2の拡散領域と絶縁膜を介して対向する制御電極と、を備え、前記第1の拡散領域と前記第2の拡散領域とは、前記制御電極に印加される電圧に応じて制御される電流の主経路を形成する。

(もっと読む)

化合物半導体装置及びその製造方法

【課題】電流コラプスを抑制しながらノーマリオフ動作を実現することができる化合物半導体装置及びその製造方法を提供する。

【解決手段】化合物半導体装置の一態様には、基板1と、基板1上方に形成された化合物半導体積層構造7と、化合物半導体積層構造上方に形成されたゲート電極11g、ソース電極11s及びドレイン電極11dと、が設けられている。化合物半導体積層構造7には、電子走行層3と、電子走行層3上方に形成された電子供給層5を含む窒化物半導体層と、が設けられている。窒化物半導体層の表面のIn組成は、平面視でゲート電極11gとソース電極11sとの間に位置する領域及びゲート電極11gとドレイン電極11dとの間に位置する領域において、ゲート電極11gの下方よりも低くなっている。

(もっと読む)

横型半導体装置及びその製造方法

【課題】既存のCMOS製造工程に対して工程の追加や変更を行うことなく、素子に要求される耐圧に応じて横型半導体装置が有するLocos酸化膜を最適に制御することができる、横型半導体装置の製造方法を提供する。

【解決手段】半導体基板(100、101)上のLocos形成領域に、遮蔽部及び開口部が所定の幅及び間隔で設けられたパターン(113a、113b)を有するマスク(113)を形成する(工程3a、3b)。マスク(113)を用いた熱酸化処理を施してLocos形成領域を酸化させ、半導体基板(100、101)のドリフト領域上に厚さが異なる(115a、155b)Locos酸化膜(105a、105b)を同時に形成する(工程4a、4b)。

(もっと読む)

半導体装置の製造方法

【課題】良好な特性の確保、素子サイズの増加の回避、及び製造プロセスの簡素化を実現できる半導体装置の製造方法を提供する。

【解決手段】Si基板111の主面に、LOCOS酸化膜112bを含む酸化膜112を形成する工程と、Si基板111の主面の側に、ソース・ゲート形成領域113aとドレイン形成領域113bとを形成する工程と、レジスト116をマスクとして、Si基板111の主面の側のLOCOS酸化膜112bで覆われていないトレンチ114を通してイオン117注入を行い、イオン注入層118を形成する工程と、LOCOS酸化膜112b上及びソース・ゲート形成領域113a上を部分的に覆うようにゲート電極119を形成する工程とを有し、イオン注入層118のゲート電極119側の端部とゲート電極119のイオン注入層118側の端部との間に間隔121が存在するように、各工程を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】プロセス条件の見直しを最小限に抑制しつつ電気的特性を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、半導体構造11の上面領域に形成された島状の絶縁膜20と、絶縁膜20の上面領域に配列された複数の凸状絶縁部23と、これら凸状絶縁部23と絶縁膜20とを被覆する層間絶縁膜26とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】 寄生ダイオードの逆回復時間を短縮でき、スイッチング損失の低減が図れるLDMOSトランジスタを低コストで提供する。

【解決手段】 LDMOSトランジスタT1が、p型半導体基板1内にp型ボディ領域2とp型埋め込み拡散領域3とn型ドリフト領域6を、ボディ領域2内にn型ソースコンタクト領域4とp型ボディコンタクト領域5を、ドリフト領域6内にn型ドレインコンタクト領域7を、ソースコンタクト領域7とドリフト領域6間のボディ領域2の上方にゲート絶縁膜8を、ゲート絶縁膜8上にゲート電極9を夫々備えて形成され、ドリフト領域6とボディ領域2は相互に接触し、埋め込み拡散領域3が、ボディ領域2の底面と接触するボディ領域2よりも深い位置に、半導体基板1の表面に平行な方向に、少なくともボディ領域2からドレインコンタクト領域7のボディ領域2から最も離間した遠方端の下方まで延在している。

(もっと読む)

横型の絶縁ゲート型バイポーラトランジスタを備えた半導体装置

【課題】オン電圧の低減と、破壊耐量確保、高速スイッチングを同時に実現できる横型IGBTを提供する。

【解決手段】エミッタ側にn型バリア層15を形成することで、ホールのバリアとして機能させ、コレクタ側から注入されたホールがエミッタ側のチャネルpウェル層6に流れ出てホール濃度が低下することを防止する。これにより、エミッタ近傍のn-型ドリフト層2内のキャリア濃度を上げることが可能となり、オン電圧の低減が可能となる。また、コレクタ側において、コレクタ電極12のうちp+型層4aと接触している部分をオーミック接触、p型層4bと接触している部分をショットキー接触とする。このショットキー接触とされた部分において、コレクタ側からのホールの注入が抑制され、蓄積キャリアを低減して、寄生バイポーラトランジスタがオンし難くなるようにできる。よって、低オン電圧を維持しながらスイッチング耐圧を確保することが可能となる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置のトランジスタのシリコンピラー上部に活性領域を設ける際に、エピタキシャル成長により前記シリコンピラー上部に形成されるシリコン膜の高さが、前記トランジスタ毎にばらつくことを防ぎ、前記シリコン膜への導電型ドーパントの注入深さを均一にする半導体装置の製造方法を提供する。

【解決手段】基板の主面に柱状のシリコンピラーを形成するシリコンピラー形成工程と、前記シリコンピラーを覆うように第1の絶縁膜を形成する第1絶縁膜形成工程と、前記第1の絶縁膜を上面から除去し、前記シリコンピラー上部の上面及び側面を露出させる第1絶縁膜除去工程と、前記シリコンピラー上部の上面及び側面にエピタキシャル成長法によりシリコン膜を形成するシリコン膜形成工程とを有する。

(もっと読む)

半導体装置の製造方法

【課題】レジストパターンの下地層への悪影響を及ぼすことなくスカムを最適に除去する半導体装置の製造方法を提供する。

【解決手段】半導体基板1の上に酸化膜5cを形成し、前記酸化膜5c上にフォトレジスト8を塗布し、前記フォトレジスト8を露光し、露光された前記フォトレジスト8を現像することにより前記フォトレジス8トに開口部8aを形成し、前記フォトレジスト8をマスクとして、前記酸化膜5cを酸素プラズマ処理し、前記酸素プラズマ処理の後、前記酸化膜5cと前記フォトレジスト8に希釈フッ酸を供給し、前記希釈フッ酸を供給する工程の後、前記フォトレジスト8をマスクとして前記酸化膜5cを通して記半導体基板1に一導電型不純物をイオン注入する工程を含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極とチャネル層との間の障壁層に低抵抗領域を備えた構成において、ゲートリーク電流を防止することによりドレイン電流の最大値の向上を図ることが可能な半導体装置を提供する。

【解決手段】化合物半導体で構成されたチャネル層14と、チャネル層14上に設けられた上部障壁層15とを備え、上部障壁層15における表面層には、不純物を含有することにより周囲よりも低抵抗に保たれた低抵抗領域15gが設けられている。また、この低抵抗領域15gを挟んだ位置において上部障壁層15に接続されたソース電極17sおよびドレイン電極17dを備えている。さらに、低抵抗領域15g上に設けられたゲート絶縁膜18と、このゲート絶縁膜18を介して低抵抗領域15g上に設けられたゲート電極19とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】回路素子の素子特性の変動を抑制すること。

【解決手段】半導体基板110には、拡散領域111を有する抵抗素子(回路素子)R1が形成されている。拡散領域111を含む半導体基板110の上には、層間絶縁膜161が形成される。拡散領域111のシリサイド層(コンタクト部)111aは、コンタクトプラグ162を介して層間絶縁膜161上の配線と接続される。拡散領域111の上には、コンタクトホール163を形成するためのエッチングストッパ膜152が形成されている。このエッチングストッパ膜152は、拡散領域111上の保護絶縁膜131に対応する部分が除去され、開口が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】エピタキシャル成長後に不純物を導入するためのイオン注入工程を省略する。また、エピタキシャル成長層の厚さがばらついた場合であっても、ピラー部にまで不純物が導入されることによるトランジスタ特性の変動を防止する。

【解決手段】基板の主面にシリコンピラーを形成した後、シリコンピラーの下の基板内に、シリコンピラーと逆導電型の第1の拡散層を形成する。シリコンピラーの側面にゲート絶縁膜を介してゲート電極を形成する。次に、シリコンピラーの上面上に不純物を含むシリコンをエピタキシャル成長させることで、シリコンピラーと逆導電型の第2の拡散層を形成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】フィンがバルク半導体上に形成されている場合においても、電流駆動力増大を図りつつ、オフリーク電流を低減させる。

【解決手段】フィン型半導体層1の両側面には、チャネル領域7のポテンシャルを制御するゲート電極4が配置され、チャネル領域7には、フィン型半導体層1のソース層2側から根元BM側にかけてポテンシャルバリアPB1、PB2が形成されている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】閾値電圧のバラつきを抑制する溝トランジスタを提供する。

【解決手段】図1に示すように、表面に少なくとも一つ以上の溝部250を有している半導体基板40と、溝部250の側壁を覆うように形成されたゲート絶縁膜20と、溝部250に埋めこまれているゲート電極10と、半導体基板40の表面に形成され、ゲート電極10を介して互いに対向しているソースおよびドレイン150と、を含み、溝部250の側壁には、複数の凸凹100が形成されている。

(もっと読む)

半導体装置の製造方法、半導体装置、SOI基板の製造方法およびSOI基板

【課題】SOI基板のチャージ蓄積による不良を抑制する。

【解決手段】まず、シード基板100の一面に、シード基板100の表面と同一面を形成するように、開口部220を有する絶縁層200を形成する(絶縁層形成工程)。次いで、シード基板100の一面に接するように、支持基板300を貼り合せる(貼り合せ工程)。次いで、シード基板100または支持基板300の一方を薄板化することにより、当該薄板化基板からなる半導体層120を形成する(半導体層形成工程)。以上の工程により、SOI基板を準備する。次いで、半導体層120に半導体素子60を形成する(半導体素子形成工程)。

(もっと読む)

半導体装置およびその製造方法

【課題】nチャネル型MISFETのしきい値を調整する目的でLaなどが導入された高誘電率膜を含むゲート絶縁膜と、その上部のメタルゲート電極との積層構造を有する半導体装置において、ゲート電極のゲート幅を縮小した際、基板側からメタルゲート電極の底面に酸化種が拡散してnチャネル型MISFETの仕事関数が上昇することを防ぐ。

【解決手段】HfおよびLn含有絶縁膜5bとその上部のメタルゲート電極である金属膜9との間に、酸化種の拡散を防ぐためにAl含有膜8cを形成する。

(もっと読む)

1 - 20 / 844

[ Back to top ]