Fターム[4M104EE17]の内容

半導体の電極 (138,591) | 絶縁膜(特徴のあるもの) (8,323) | 材質 (4,070) | 窒化シリコン (1,346)

Fターム[4M104EE17]に分類される特許

1 - 20 / 1,346

電界効果トランジスタ

半導体装置およびその製造方法

電界効果トランジスタ

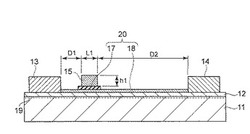

【課題】耐圧および電流コラプス抑制性能をさらに向上できる電界効果トランジスタを提供する。

【解決手段】この電界効果トランジスタによれば、ゲート絶縁膜20を、ストイキオメトリなシリコン窒化膜よりもシリコンの比率が高いシリコン窒化膜で作製されたコラプス抑制膜18と上記コラプス抑制膜18上に形成されたSiO2絶縁膜17とを有する複層構造とすることにより、耐圧を向上できるだけでなく、電流コラプスも抑制できる。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】微細な構造であり、高い電気特性を有する半導体装置を歩留まりよく提供する。

【解決手段】酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極と、ゲート電極上の導電膜と、酸化物半導体膜及びゲート絶縁膜の側面に接するソース電極及びドレイン電極と、を有し、ソース電極及びドレイン電極の上面の高さは、ゲート電極の上面の高さより低く、導電膜、ソース電極及びドレイン電極は、同一の金属元素を有する半導体装置である。また、ゲート電極の側面を覆う側壁絶縁膜を形成してもよい。

(もっと読む)

半導体装置とその製造方法

【課題】ゲート高さが低いため製造容易で、ゲート−コンタクト間の容量を抑制し、ゲート−コンタクト間の短絡を抑制した半導体装置を提供する。

【解決手段】半導体装置の製造方法は基板上にFin型半導体層を形成する。Fin型半導体層に交差するダミーゲートが形成される。Fin型半導体層にソースおよびドレインが形成される。ダミーゲート上に層間絶縁膜を堆積した後、ダミーゲートの上面を露出させる。ダミーゲートを除去してゲートトレンチを形成する。ゲートトレンチ内のFin型半導体層の上部をリセスする。ゲートトレンチ内のFin型半導体層の表面にゲート絶縁膜を形成する。ゲート電極をゲートトレンチ内に充填する。ゲート電極をエッチングバックすることによってゲート電極を形成する。ゲート電極の上面の高さはソースおよびドレインにおけるFin型半導体層の上面の高さ以下かつゲートトレンチ内のFin型半導体層の上面の高さ以上である。

(もっと読む)

トランジスタ、表示装置および電子機器

【課題】良好な歩留りで製造可能なトランジスタ、表示装置および電子機器を提供する

【解決手段】ゲート電極と、絶縁層を間にして前記ゲート電極に対向する半導体層と、

前記半導体層に電気的に接続された一対のソース・ドレイン電極と、前記一対のソース・ドレイン電極それぞれと前記半導体層との間のキャリア移動経路に設けられ、その端面が前記ソース・ドレイン電極に覆われたコンタクト層と、を備えたトランジスタ。

(もっと読む)

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極

、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し

、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が

除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供

給し、酸素原子が供給された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜

上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である

。

(もっと読む)

半導体装置

【課題】酸化物半導体を用いたトランジスタを有する信頼性の高い半導体装置を提供する。

【解決手段】ガラス基板上に設けられたボトムゲート構造のスタガ型トランジスタを有する半導体装置において、ゲート電極層上に組成を異なる第1のゲート絶縁膜及び第2のゲート絶縁膜が順に積層されたゲート絶縁膜を設ける。又は、ボトムゲート構造のスタガ型トランジスタにおいて、ガラス基板とゲート電極層との間に保護絶縁膜を設ける。第1のゲート絶縁膜と第2のゲート絶縁膜との界面、又はゲート電極層とゲート絶縁膜との界面における、ガラス基板中に含まれる金属元素の濃度を、5×1018atoms/cm3以下(好ましくは1×1018atoms/cm3以下)とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】半導体装置の特性の向上を図る。

【解決手段】本発明の半導体装置は、(a)素子分離領域STIにより囲まれた半導体領域3よりなる活性領域Acに配置されたMISFETと、(b)活性領域Acの下部に配置された絶縁層BOXとを有する。さらに、(c)活性領域Acの下部において、絶縁層BOXを介して配置されたp型の半導体領域1Wと、(d)p型の半導体領域1Wの下部に配置されたp型と逆導電型であるn型の第2半導体領域2Wと、を有する。そして、p型の半導体領域1Wは、絶縁層BOXの下部から延在する接続領域CAを有し、p型の半導体領域1Wと、MISFETのゲート電極Gとは、ゲート電極Gの上部から接続領域CAの上部まで延在する一体の導電性膜であるシェアードプラグSP1により接続されている。

(もっと読む)

窒化物半導体装置

【課題】電極のコンタクト抵抗や逆方向リーク電流を低減できる窒化物半導体装置を提供する。

【解決手段】窒化物半導体層103と、窒化物半導体層103よりもバンドギャップが大きい窒化物半導体層104との接合体が少なくとも1つ基板101上に積層されている。窒化物半導体層104の上面から窒化物半導体層103における窒化物半導体層104との界面よりも下側までの範囲に位置する部分の前記接合体の両側端にテーパ部108及び109が形成されている。テーパ部108の側面上には窒化物半導体層103とショットキー接触するようにアノード電極106が形成されており、テーパ部109の側面上には窒化物半導体層103とオーミック接触するようにカソード電極107が形成されている。各テーパ部108及び109の側面が基板101の主面に対してなす角度は、20度以上で且つ75度以下である。

(もっと読む)

電界効果トランジスタおよびその製造方法

【課題】耐圧を向上できる電界効果トランジスタを提供する。

【解決手段】GaN系HFETは、ゲート絶縁膜17をなす半絶縁膜の抵抗率ρが、電流密度が6.25×10−4(A/cm2)であるとき、3.9×109Ωcmであった。抵抗率ρ=3.9×109Ωcmの半絶縁膜によるゲート絶縁膜15を備えたことで、1000Vの耐圧が得られた。ゲート絶縁膜の抵抗率が、1×1011Ωcmを超えると耐圧が急減し、ゲート絶縁膜の抵抗率が、1×107Ωcmを下回るとゲートリーク電流が増大する。

(もっと読む)

ポリメタルゲート電極を持つ半導体素子の製造方法

【課題】TiN膜及びバッファ層から形成されるバリアー膜を備えるポリメタルゲート電極を持つ半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に半導体基板側から順に積層された導電性ポリシリコン膜、第1金属シリサイド膜、バリアー膜、及び金属膜から形成されるポリメタルゲート電極と、を備える半導体素子である。バリアー膜は、第1金属シリサイド膜上に形成されるTiN膜と、TiN膜と金属膜との間に介在されるバッファ層と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】コンタクトプラグに接続される配線間隔の縮小を可能にする半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板に第1の領域と第2の領域とを定義し、第1の領域に第1のサイズを持つ第1の素子を形成し、第2の領域に、第1のサイズとは異なる第2のサイズを持つ第2の素子を形成し、第1の素子及び第2の素子を覆うように半導体基板上に第1の層間絶縁膜を形成し、第1の領域上の第1の層間絶縁膜を貫通し第1の素子の一部を露出させる第1のコンタクトホールを形成し、第2の領域上の第1の層間絶縁膜を貫通し第2の素子の一部を露出させる第2のコンタクトホールを形成し、第1のコンタクトホール及び第2のコンタクトホールをそれぞれ埋める第1のコンタクトプラグ及び第2のコンタクトプラグを同時に形成する。

(もっと読む)

保護素子、半導体装置及び半導体装置の製造方法

【課題】ヘテロ接合を利用した新規な保護素子を提供すること。

【解決手段】 半導体装置10の保護部36は、配線下層11Bと、配線下層11Bとは異なるバンドギャップを有する配線上層13を有している。配線上層13は、第1部位41と中間部位43と第2部位45を含んでいる。配線上層13と配線下層11Bの接合面に形成される2次元電子ガス層が、第1部位41と中間部位43の間で分離されており、第2部位45と中間部位43の間で分離されている。第1部位41と配線下層11Bの接合面に形成される2次元電子ガスが、ドレイン電極21に電気的に接続されている。第2部位45と配線下層11Bの接合面に形成される2次元電子ガスが、ソース電極28に電気的に接続されている。中間部位43と配線下層11Bの接合面に形成される2次元電子ガスが、ゲート電極25に電気的に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

半導体装置の製造方法

【課題】特性の良好な半導体装置を製造する。

【解決手段】本発明は、MISFETを有する半導体装置の製造方法であって、(a)半導体基板の上方に、シリコン膜と絶縁膜CPとの積層膜を形成する工程と、(b)積層膜をパターニングすることによりゲート電極GE1とその上部に配置された絶縁膜CPとの積層体を形成する工程と、(c)積層体の側壁にサイドウォール膜SWを形成する工程と、(d)絶縁膜CPを除去する工程と、(e)サイドウォール膜SWおよびゲート電極GE1の合成体の両側の半導体基板中および前記ゲート電極GE1中にヒ素(As)を注入する工程と、を有する。かかる製法によれば、ヒ素(As)のイオン注入によるゲート電極GE1の体積膨張、特に、横方向への膨らみを低減することができ、ゲート電極とコンタクトプラグとの短絡を低減できる。

(もっと読む)

半導体装置およびその製造方法

【課題】隣接するSOI領域とバルクシリコン領域とが短絡することを防止する。

【解決手段】一つの活性領域内にSOI領域およびバルクシリコン領域が隣接する半導体装置において、それぞれの領域の境界にダミーゲート電極8を形成することにより、BOX膜4上のSOI膜5の端部のひさし状の部分の下部の窪みにポリシリコン膜などの残渣が残ることを防ぐ。また、前記ダミーゲート電極8を形成することにより、それぞれの領域に形成されたシリサイド層14同士が接触することを防ぐ。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電界が局所的に集中することを抑制して、高耐圧化した半導体装置を提供する。

【解決手段】第1導電型の第1ドリフト領域140は、平面視でソース領域110から離間して設けられている。第1導電型の第2ドリフト領域150は、平面視で第1ドリフト領域140のうちソース領域110と反対側の領域に接している。第1導電型のドレイン領域120は、平面視で第1ドリフト領域140から離間しているとともに、平面視で第2ドリフト領域150のうち第1ドリフト領域140と反対側の領域に接している。チャネル領域130上には、ゲート絶縁層200およびゲート電極400が設けられている。第1フィールドプレート絶縁層300は、半導体基板100上に設けられ、少なくとも平面視で第1ドリフト領域140と第2ドリフト領域150の一部と重なるように設けられている。第1フィールドプレート電極420は、第1フィールドプレート絶縁層300上に接している。

(もっと読む)

半導体装置

【課題】配線抵抗に伴う電圧降下や信号遅延によるトランジスタへの信号の書き込み不良

を防止した半導体装置を提供することを課題の一つとする。例えば、表示装置の画素に設

けたトランジスタへの書き込み不良が引き起こす階調不良などを防止し、表示品質の高い

表示装置を提供することを課題の一つとする。

【解決手段】配線抵抗が低い銅を含む配線に、バンドギャップが広く、且つキャリア濃度

が低い高純度化された酸化物半導体を接続してトランジスタを作製すればよい。バンドギ

ャップが広い酸化物半導体を用いて、トランジスタのオフ電流を低減するだけでなく、キ

ャリア濃度が低い高純度化された酸化物半導体を用いて正のしきい値電圧を有し、所謂ノ

ーマリーオフ特性のトランジスタとして、オフ電流とオン電流の比を大きくできる。

(もっと読む)

第III族金属窒化物−絶縁半導体ヘテロ構造電界効果トランジスタ

【課題】ヘテロ構造電界効果トランジスタに関して、電流崩壊、ゲートリークおよび高温信頼性などの課題を解消する。

【解決手段】高電子移動度トランジスタ(HEMT)、金属−絶縁半導体電界効果トランジスタ(MISFET)あるいはこれらの組み合わせなどの集積回路(IC)デバイスの装置、方法およびシステムであって、該ICデバイスは、基板102上で形成されたバッファ層104と、アルミニウム(Al)と窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つを含み、バッファ層104上に形成されたバリア層106と、窒素(N)とインジウム(In)またはガリウム(Ga)の少なくとも1つとを含み、バリア層106上に形成されたキャップ108層と、キャップ層108に直接連結され、その層上に形成されたゲート118と、を含む。

(もっと読む)

1 - 20 / 1,346

[ Back to top ]