Fターム[5F140BG07]の内容

絶縁ゲート型電界効果トランジスタ (137,078) | ゲート電極及び側壁の製造 (21,161) | ゲート側壁構造及び配置 (6,762)

Fターム[5F140BG07]の下位に属するFターム

ゲート側壁 (2,045)

2重ゲート側壁 (909)

3重以上のゲート側壁 (335)

ゲート側壁材料 (3,458)

Fターム[5F140BG07]に分類される特許

1 - 15 / 15

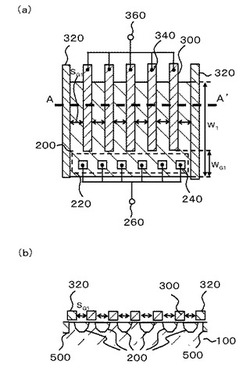

半導体装置及び半導体装置の検査方法

【課題】狭いゲート電極間にコンタクトを配置することなく、オーバーラップ容量を測定する。

【解決手段】この半導体装置は、下記のような第1TEGパターン(不図示)を備えている。第1TEGパターンは、素子分離領域500と、素子分離領域500に形成された開口部(不図示)と、開口部上に設けられ、互いに平行に延伸した複数のゲート電極300と、開口部のゲート電極300で覆われていない部分に形成された拡散領域200と、を備えている。ここで、ゲート電極300の一方の端部は、開口部の外縁よりも内側に配置されている。また、第1コンタクト240は、ゲート電極300の一方の端部と、開口部の外縁の間に位置して、拡散領域200に接続している。一方、第2コンタクト340は、ゲート電極300に接続している。

(もっと読む)

半導体装置及びその製造方法

【課題】下地絶縁膜の膜厚精度の向上とトランジスタ特性の変動抑制との両立が図られたMISトランジスタを備えた半導体装置、及びその製造方法を提供する。

【解決手段】半導体装置は、半導体基板100における活性領域103a上に形成されたゲート絶縁膜108aと、ゲート絶縁膜108a上に形成されたゲート電極111aとを有するMISトランジスタ170を備えている。ゲート絶縁膜108aは、活性領域103a上に形成された板状の下層ゲート絶縁膜210aと、下層ゲート絶縁膜210a上に形成された断面形状が凹状の上層ゲート絶縁膜211aとを有する。下層ゲート絶縁膜210aは、活性領域103a上に形成された下地絶縁膜104aと、第1の高誘電率絶縁膜106aとで構成され、上層ゲート絶縁膜211aは、第1の高誘電率絶縁膜106a上に形成された第2の高誘電率絶縁膜107aで構成される。

(もっと読む)

電界効果トランジスタ

【課題】急峻なS値特性を有するとともに、ソース/ドレイン領域が同じ導電型となる対称構造を有する電界効果トランジスタを提供する。

【解決手段】本実施形態による電界効果トランジスタは、半導体層と、前記半導体層に離間して設けられたソース領域およびドレイン領域と、前記ソース領域と前記ドレイン領域との間の前記半導体層上に設けられたゲート絶縁膜と、前記ゲート絶縁膜上に設けられたゲート電極と、前記ソース領域および前記ドレイン領域側の前記ゲート電極の少なくとも一方の側面に設けられた高誘電体のゲート側壁と、を備え、前記ソース領域および前記ドレイン領域は前記ゲート電極の対応する側面から離れている。

(もっと読む)

半導体装置およびその製造方法

【課題】微細化しても高い性能を実現可能な半導体装置を提供する。

【解決手段】実施の形態の半導体装置は、半導体基板と、半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の両側に形成された第1のゲート側壁と、半導体基板上に形成され、ゲート電極との間に第1のゲート側壁を挟むソース・ドレイン半導体層と、を備える。さらに、ゲート電極の両側に、第1のゲート側壁上およびソース・ドレイン半導体層上に形成され、第1のゲート側壁との境界がゲート電極の側面で終端し、第1のゲート側壁よりもヤング率が小さく、かつ、低誘電率の第2のゲート側壁、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】工数を大幅に増加せず且つ高誘電体からなるゲート絶縁膜にダメージを与えることがない、仕事関数変更用金属不純物膜の効果を有する半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板101と、半導体基板101の上部に形成されたp型活性領域110と、p型活性領域110の上に形成されたゲート絶縁膜150と、ゲート絶縁膜150の上に形成されたゲート電極106とを有している。ゲート絶縁膜150は、二酸化シリコンよりも大きい誘電率を有する高誘電体膜103と、高誘電体膜103の上に形成され、炭素を含む炭素含有膜104とを有している。高誘電体膜103及び炭素含有膜104は、第1の金属としてランタン又はマグネシウムを含み、ゲート電極106は、第2の金属を含む。

(もっと読む)

半導体装置と論理回路およびその製造方法

【課題】インパクトイオン化MISFETに関して、微細素子において二つの入力によりAND型論理素子動作することを可能とし、素子バラツキを低減することを可能とし、消費電力を低減することを可能とする半導体装置を提供する。

【解決手段】第1導電型または真性である半導体領域の表面上に形成された二つの独立した第一および第二のゲート電極への両者への入力により反転層が形成された場合に、インパクトイオン化によるスイッチング動作が可能となることを特徴とする、半導体装置である。

(もっと読む)

静電放電保護装置、半導体装置及び静電放電保護装置の製造方法

【課題】バラスト抵抗の抵抗値の変動を抑制することのできる静電放電保護装置、半導体装置及び静電放電保護装置の製造方法を提供することにある。

【解決手段】基板40上にゲート酸化膜41を介してゲート電極42を形成した。このゲート電極42を挟んで基板40中のソース形成領域S及びドレイン形成領域Dに、n−型拡散領域44S,44Dをそれぞれ形成し、そのn−型拡散領域44S,44Dの下にn+型拡散領域45S,45Dをそれぞれ形成した。n−型拡散領域44Dの表面に、ゲート電極42のサイドウォール43からシリサイドブロック領域52分だけ離間してドレイン電極51を形成した。このドレイン電極51の真下領域であってn+型拡散領域45Dの下端と深さ方向において重なるかたちでp+型拡散領域55を形成した。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の微細化が進行しても、素子分離絶縁膜の応力がチャネルに与える影響を抑え、集積回路の設計において半導体特性をパラメタライズすることができる半導体装置を得ること。

【解決手段】半導体基板10上に所定のパターンで形成された素子分離絶縁膜11と、素子分離絶縁膜11で区画される半導体基板10表面の所定の位置に形成されるゲート絶縁膜22,32とゲート電極23,33とを含むゲート構造21,31と、ゲート構造21,31の線幅方向両側の半導体基板10表面に形成されるソース/ドレイン領域25,35と、を備え、ゲート構造21,31と素子分離絶縁膜11との間の半導体基板10表面は、ヤング率が半導体基板10よりも小さい材料からなる。

(もっと読む)

半導体記憶装置

【課題】微細化が進展しても、データ書き込み時には閾値が低く、“1”データ保持時には閾値が高くすることができ、良好なデータ書き込み特性および良好なデータ保持特性の両立を図ることが可能な半導体記憶装置を提供する。

【解決手段】ゲート電極G1の側壁には側壁絶縁膜35が形成される。n型拡散層36の表面にはビット線コンタクト51が形成され、n型拡散層27は、埋め込みストラップ41、及びポリシリコン電極22Aを介してストレージノード電極22に接続されている。側壁絶縁膜35は、トレンチキャパシタ側、即ちストレージノード電極22側の厚さが、ビット線コンタクト51側の厚さよりも大きくされている。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極上に応力絶縁膜を設けた半導体装置において、MISトランジスタの駆動能力が低下することを防止する。

【解決手段】半導体基板100上における第1の活性領域100bに形成された第1のMISトランジスタを有する半導体装置であって、第1のMISトランジスタは、第1の活性領域100b上に形成された第1のゲート絶縁膜103bと、第1のゲート絶縁膜103b上に形成された第1のゲート電極104bと、第1のゲート電極104bにおける上面及びゲート長方向の側面上に形成され、第1のMISトランジスタのチャネルに対して第1の応力をゲート長方向に働かせる第1の応力絶縁膜111bと、第1のゲート電極104bにおけるゲート幅方向の側面上に形成された第1の下地絶縁膜112とを備え、第1のゲート電極104bにおけるゲート幅方向の側面上には、第1の応力絶縁膜111bが形成されていない。

(もっと読む)

半導体装置

【課題】 本発明は、小さいヒステリシスを有する半導体装置を提供することを目的とする。

【解決手段】 本発明の半導体装置は、Geを主成分として含むチャネル領域を有する半導体基板と、チャネル領域上に形成され、Zr、HfおよびLa系元素からなる群から選ばれる金属元素MおよびSiを含む酸化物を有するゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、チャネル領域をゲート長方向に挟むソース・ドレイン領域と、を備えることを特徴とする。

(もっと読む)

ゲートスペーサー構造と低抵抗チャネル連結部とを備えた電界効果トランジスタ

【課題】ゲート電極とソース/ドレイン領域の間のオーバラップ容量を低減し製造プロセスにより設定されるチャネル連結部の抵抗も低減した電界効果トランジスタ構造を提供する。

【解決手段】電界効果トランジスタのスペーサー構造242p、242nには、束縛された電荷キャリアが部分的に濃縮されており、移動可能な電荷キャリアの濃縮帯13n、13pが該スペーサー構造の下の半導体基板1の中に生じる。この濃縮帯13n、13pは、各ソース/ドレイン領域61、62と、ゲート電極21の電位によって制御されているチャネル領域63との間のチャネル連結部の抵抗を低減し、ゲート電極21と各ソース/ドレイン領域61、62との間のオーバーラップ容量を低減する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極の厚さ以外の調整によりサイドウォールの幅を高精度に制御することができる半導体装置の製造方法を提供する。

【解決手段】まず、P型シリコン基板101素子形成領域103にゲート酸化膜105、ゲート電極106、低濃度N型拡散層107を形成し、絶縁膜を堆積して異方性エッチングすることによりサイドウォール109を形成する。続いて、素子形成領域104にゲート酸化膜201、ゲート電極202、低濃度N型拡散層203を形成し、絶縁膜を堆積して異方性エッチングすることによりサイドウォール205を形成する。サイドウォール109用の絶縁膜とサイドウォール205用の絶縁膜とを別の工程で堆積し且つこれら絶縁膜の膜厚を個別に調整することにより、サイドウォール109,205の幅L1,L2を任意の値に設定できる。その後、イオン注入により、高濃度不純物領域206,207を自己整合的に形成する。

(もっと読む)

半導体素子およびその製造方法

【課題】素子の微細化が可能でスイッチング性能の高い立体構造を有する電界効果型トランジスタである半導体素子を提供する。

【解決手段】ソース領域と、前記ソース領域の上部に配置された半導体機能層と及び、前記半導体機能層の上部に配置されたドレイン領域とを備え、前記半導体機能層は、前記ソース領域に対してほぼ垂直に配列した、複数の柱状あるいは円筒状の半導体物質からなる第1の部材と、前記第1の部材を取り囲み、前記ソース領域と絶縁体を介して配置された第2の部材から構成され、前記第2の部材はゲート領域と、絶縁体領域とから構成されており、前記第1の部材の平均直径が1nm以上30nm以下であり、前記第1の部材の平均間隔が3nm以上50nm以下であり、前記半導体層の酸素を除く主成分がシリコン、またはゲルマニウム、またはシリコンとゲルマニウムの混合物のいずれかである半導体素子を用いる。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 ホットキャリア耐性が高いFETを備える半導体装置および半導体装置の製造方法を提供する。

【解決手段】 シリコン基板102とシリコン基板102上に形成されるLDD構造のMOSFET110とを備える半導体装置100において,MOSFET110のLDD部は,相互に注入エネルギが異なる2度以上のイオン注入により形成されることを特徴としている。したがって,ホットキャリアの発生位置をシリコン基板102の深部に移動させ,MOSFET110のホットキャリア耐性が向上する。

(もっと読む)

1 - 15 / 15

[ Back to top ]