Fターム[4M104FF26]の内容

Fターム[4M104FF26]の下位に属するFターム

基板の凹部 (569)

合金化による潜り込み (29)

ダイレクトコンタクト (46)

Fターム[4M104FF26]に分類される特許

141 - 155 / 155

半導体装置および半導体装置の製造方法

【課題】 異なるゲート長またはゲート幅を有し、フルシリサイド化されたゲート電極を備えた半導体装置を提供する。

【解決手段】 半導体装置100は、半導体基板5と、半導体基板上に形成された第1のゲート絶縁膜51と、半導体基板上に形成された第2のゲート絶縁膜52と、第1のゲート絶縁膜上に形成され、フルシリサイド化された第1のゲート電極11と、第2のゲート絶縁膜上に形成され、フルシリサイド化された第2のゲート電極12であって、半導体基板の表面を占める面積が第1のゲート電極よりも大きく、なおかつ、第1のゲート電極よりも厚みが薄い第2のゲート電極12とを備えている。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 ガードリングからのリーク電流を低減することができるショットキーダイオードなどの半導体装置および半導体装置の製造方法を提供する。

【解決手段】 N型のSiCからなる高濃度層3と、高濃度層3上に積層されN型のSiCからなり高濃度層3よりも不純物濃度が低いドリフト層4と、ドリフト層4上に積層されN型のSiCからなりドリフト層4よりも不純物濃度が低い低濃度層6aと、低濃度層6a上に形成され低濃度層6aとショットキー接触したバリアメタル膜8と、P型のSiCからなり低濃度層6a内に埋設されている部位、低濃度層6aから露出している部位、その露出している部位の一部であってバリアメタル膜8の周辺部と接している部位を有するガードリング領域5とを有することを特徴とする。

(もっと読む)

絶縁ゲート電界効果トランジスタの製造方法および絶縁ゲート電界効果トランジスタ

【課題】ゲート長の短縮に対応して最適な接合深さのエクステンション部を形成できなくなってきている。

【解決手段】ゲートスタック7と側壁絶縁膜9からなる所定の幅のスペーサをマスクとする不純物のイオン注入と活性化アニールにより、2つのソース・ドレイン領域10をPウェル3に形成する。側壁絶縁膜9を除去し、これより薄い隔壁絶縁膜11を形成することによって、このスペーサの幅方向両側を後退させる。これによりスペーサのエッジと2つのソース・ドレイン領域10のエッジとを幅方向両側で離す。この状態で、後退したスペーサの幅方向両側に露出し2つのソース・ドレイン領域10を含むウェル領域に選択的なエピタキシャル成長により半導体材料を成長させ、後退したスペーサにより分離する2つのエクステンション部12を形成する。この製法においては、イオン注入の活性化アニールによりエクステンション部12内の不純物がPウェル3内に熱拡散しない。

(もっと読む)

半導体集積回路装置の製造方法

【課題】0.15μm世代以下のMISFETの高速動作を実現することのできる技術を提供する。

【解決手段】ゲート電極10nおよびサイドウォールスペーサ15をマスクとして、基板1の法線方向からn型不純物をイオン注入し、ソース、ドレイン拡散領域11bを形成した後、基板1の法線方向に対して所定の角度を有する斜め打ち込みでn型不純物をイオン注入し、基板1の表面から深さ20〜40nm程度の位置にソース、ドレイン拡張領域11aよりも相対的に不純物濃度の高いn型半導体領域16を形成する。

(もっと読む)

液晶表示装置

【課題】効率よく放熱することが可能な薄膜トランジスタを備えた液晶表示装置を提供する。

【解決手段】基板上にマトリクス状に配置された複数の画素PXによって構成された表示部と、基板上の表示部の外側領域に設けられ、表示部を駆動するための駆動回路と、を備える液晶表示装置10であって、それぞれに切欠部132aを有した一対の拡散層を備えるポリシリコン半導体層132と、拡散層のそれぞれの上面及び切欠部に沿った端面に接触する第1電極136及び第2電極138と、第1電極136と第2電極138との間の電流をオンオフする電圧が加えられる第3電極134と、を備える薄膜トランジスタを具備した液晶表示装置10。

(もっと読む)

半導体装置、SRAMおよび半導体装置の製造方法

【課題】 狭い活性領域にコンタクト部を配設する工程を、容易に行うことができる半導体装置および半導体装置等を提供する。

【解決手段】 本発明に係る半導体装置は、SOI基板10、活性領域3a、第一の絶縁膜(完全分離絶縁膜)3b、第二の絶縁膜(部分分離絶縁膜)3c、およびコンタクト部4を備えている。ここで、活性領域3aは、SOI層3の表面内に形成されている。また、第一の絶縁膜3bは、活性領域3aの一方の側面に形成されており、かつ、SOI層3の表面から埋め込み絶縁膜2にかけて形成されている。また、第二の絶縁膜3cは、活性領域3aの他方の側面において形成されており、かつ、SOI層3の表面から、埋め込み絶縁膜2に至らない所定の深さにかけて形成されている。また、コンタクト部4は、平面視において、活性領域3aの中心より第一の絶縁膜3bが存する側に配設されている。

(もっと読む)

半導体装置及びその製造方法

【課題】 サイドウォールのエッチングを抑えて、加工マージンを確保する。

【解決手段】 ゲート電極の側壁にサイドウォールを有するトランジスタを覆うように、下から順番に第1のシリコン窒化膜、第1のシリコン酸化膜、第2のシリコン窒化膜及び第2のシリコン酸化膜を形成する。トランジスタのソース・ドレイン領域とゲート電極の両方にまたがる領域に開口を有するフォトレジストをマスクとし、第2のシリコン窒化膜をエッチングストッパとして第2のシリコン酸化膜をドライエッチングし、第2のシリコン窒化膜をドライエッチングし、第1のシリコン窒化膜をエッチングストッパとして第1のシリコン酸化膜をドライエッチングし、第1のシリコン窒化膜をドライエッチングして、コンタクトホールを形成する。コンタクトホールに導電物質を埋め込むことにより、トランジスタのソース・ドレイン領域とゲート電極の両方に達するシェアードコンタクトを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】 基板浮遊効果を抑制することのできる半導体装置およびその製造方法を提供する。

【解決手段】 絶縁層と、前記絶縁層の上方に形成された半導体層と、前記半導体層の上方に形成されたゲート絶縁層と、前記ゲート絶縁層の上方に形成されたゲート電極と、前記半導体層に形成されたソース領域およびドレイン領域と、前記ゲート絶縁層の下方に形成されたボディ領域と、前記半導体層において、前記ボディ領域に対して前記ソース領域側に形成され、かつ、前記ボディ領域とショットキー接合する複数のショットキー接合領域と、を含む。

(もっと読む)

横型MOSトランジスタ

【課題】 配線抵抗及び配線容量を低減するとともに、チップ面積を削減する。

【解決手段】 SOI基板30は、シリコン基板31の上にシリコン酸化膜32が形成され、このシリコン酸化膜32の上にN−型シリコン層33が形成されて構成される。ドレイン領域35は、シリコン層33の表面からシリコン酸化膜32まで到達して形成される。ドレイン電極42は、SOI基板30の裏面に電気的接触して形成される。導電体プラグ41は、ドレイン領域35の表面からドレイン領域35およびシリコン酸化膜32を貫通してシリコン基板31中に延在して、ドレイン領域35およびシリコン基板31に電気的接触して形成される。

(もっと読む)

トランジスタ

【課題】 製造工程を複雑化させずに良好なトランジスタ特性を保持できる上、小型化が可能なトランジスタを提供する。

【解決手段】 ベース電極(15)とエミッタ電極(17)とが同一面内において互いに分離して形成され、複数のエミッタ領域(13)は、ほぼ均等に分散して配置され、ベース電極(15)及びエミッタ電極(17)には、ワイヤーボンディング用の領域として、それぞれベースボンディングパッド領域(18)及びエミッタボンディングパッド領域(19)が設けられ、ベースボンディングパッド領域(18)及びエミッタボンディングパッド領域(19)のそれぞれの直下には、複数のエミッタ領域(13)の一部とベース層(12)との接合箇所が配置されていることを特徴とするトランジスタ(1)とする。

(もっと読む)

薄膜トランジスタの製法およびそれによって得られた薄膜トランジスタ

【課題】ソースおよびドレインの形成にかかるコストを低減することができる薄膜トランジスタの製法およびそれによって得られた薄膜トランジスタを提供する。

【解決手段】基板1上に薄膜トランジスタを形成する方法であって、ソースS1 およびドレインD1 の形成が、上記基板1上に形成されたSi多結晶膜からなるチャネルC1 の表面のソースS1 およびドレインD1 形成予定部分に、PまたはBを含有するSiGe薄膜を成長させることにより行われる。

(もっと読む)

液晶用マトリクス基板およびその製造方法

【課題】 表示品位が高く、周辺回路とのコンタクト性に優れた液晶表示装置を構成するマトリックス基板およびその製造方法を実現する。

【解決手段】 複数の液晶セルを形成するためのマトリクス回路が形成されている液晶用マトリクス基板において、液晶パネルを組み立てるときに貼り合わせ面となる表面に島状に、第1の導電材からなる絵素電極12と、第2の導電材からなる端子電極13とを形成する。このとき、第1の導電材は、第2の導電材よりも透過性が高く、かつ、導電性が低いものを使用する。

(もっと読む)

半導体装置

【課題】 集積度の向上が容易な半導体装置を提供する。

【解決手段】 活性領域4aには、nMOSトランジスタ10の1対のソース/ドレイン領域11、11が形成されている。1対のソース/ドレイン領域11、11に挟まれる半導体基板の領域上にゲート酸化膜を介してゲート電極層13が形成されている。ゲート電極層13は、活性領域4a上および素子分離構造上の双方に延在し、かつ素子分離構造上にコンタクトパッド部13aを有し、かつ活性領域4aとコンタクトパッド13aとの平面的な間隔S1が0.5μm未満である。

(もっと読む)

エッチング条件の設定方法、半導体装置の製造方法、及び半導体装置

【課題】 少ない労力でビアホール等を形成するときのエッチング条件が適切か否かを確認できるようにする。

【解決手段】 基準部、該基準部より低地である低地部、及び前記基準部より高地である高地部を有する半導体基板1上に、導電膜2及び層間絶縁膜3を形成し、層間絶縁膜3の表面を平坦化する。層間絶縁膜3をエッチングすることにより、低地部の上方に位置する第1及び第2の接続孔3a、前記基準部の上方に位置する第3の接続孔3b、及び高地部の上方に位置する第4の接続孔3cを同時に形成する。第1〜第4の接続孔3a〜3cそれぞれに、第1〜第4の導電体4a〜4cを埋め込む。層間絶縁膜3上に、第1の導電体3a、第3の導電体4b及び第4の導電体4cを互いに接続する上部電極5bを形成し、上部電極5bと、第1の導電体3aとの間の抵抗を測定する。

(もっと読む)

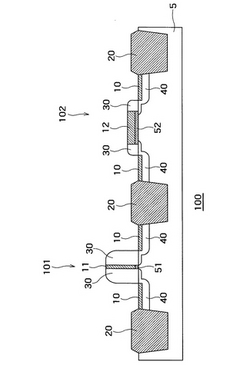

多層配線構造

【課題】 金属配線の微細化とエレクトロマイグレーションの抑制との両立を図ることができる多層配線構造を工程数の増加を招くことなく実現する。

【解決手段】 第1の金属配線13の一端部13aと第2の金属配線15の一端部15aとは第1のプラグ16を介して接続されており、第1の金属配線13の他端部13bと第3の金属配線17の一端部17aとは第2のプラグ18を介して接続されている。第1、第2及び第3の金属配線13、15、17の配線幅は、互いに等しいと共に第1及び第2のプラグ16、18の径ともほぼ等しい。第1の金属配線13の他端部13bの配線幅は、第1の金属配線13の一端部13a及び第3の金属配線17の一端部17aの配線幅よりも大きい。第2の金属配線15の一端部15aの配線幅は第1の金属配線13の一端部13aの配線幅よりも大きい。

(もっと読む)

141 - 155 / 155

[ Back to top ]