Fターム[4M104FF26]の内容

Fターム[4M104FF26]の下位に属するFターム

基板の凹部 (569)

合金化による潜り込み (29)

ダイレクトコンタクト (46)

Fターム[4M104FF26]に分類される特許

121 - 140 / 155

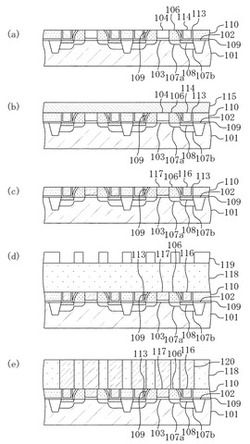

半導体装置とその製造方法

【課題】MISトランジスタを有する半導体装置において、微細化及び製造歩留りの向上を実現する。

【解決手段】半導体装置は、基板101上にゲート絶縁膜103を介して形成されたゲート電極117と、基板101におけるゲート電極117の両側に形成されたソース領域及びドレイン領域107bとを有するMISトランジスタを備え、ゲート電極117は金属シリサイドからなり、ソース領域及びドレイン領域107bの少なくとも一方の上に、金属シリサイドからなる第1のコンタクト電極116を備える。

(もっと読む)

絶縁ゲート電界効果トランジスタ及びその製造方法

【課題】短チャネル効果を抑制しつつ、一層の高速動作が可能な絶縁ゲート電界効果トランジスタ及びその製造方法の提供を目的とする。

【解決手段】チャネルが形成される半導体基板の領域と、当該領域にそれぞれ接し互いに離れて前記半導体基板上に形成されている一対のエクステンション部4と、前記一対のエクステンション部4の対向端から互いに離反する向きにさらに離れて前記エクステンション部4上に形成されている一対のソース・ドレイン領域5,6と、前記ソース・ドレイン領域5,6の間のチャネルが形成される半導体基板上において前記エクステンション部4の端部にかかる位置まで形成されているゲート絶縁膜5と前記ゲート絶縁膜5上に形成されたゲート電極Gと、少なくとも前記ゲート電極Gから前記一対のエクステンション部4にかかる領域までを被覆するように形成された応力調整層8と、を有する絶縁ゲート電解効果トランジスタ1。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクトを有し、且つ、リーク電流の低減が図れる半導体装置及びその製造方法を提供する。

【解決手段】シェアードコンタクト形成領域に位置するゲート電極配線14bの上面上及び側面上にはシリサイド層20dが形成されている。そして、層間絶縁膜22には、N型ソース・ドレイン領域19b上のシリサイド層20b及びゲート電極配線14b上のシリサイド層20dに接続するシェアードコンタクトとなるコンタクトプラグ24bが形成されている。これにより、層間絶縁膜22にコンタクトホール23bを形成した際、半導体基板11の表面を露出させることなく形成することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】 ヘテロ接合半導体素子と別の半導体素子とが同一基板上に集積され、かつ、この別の半導体素子の電極取り出し構造が改良された半導体装置及びその製造方法を提供すること。

【解決手段】 前記別の半導体素子の一例である抵抗素子20を構成する抵抗層11を、イオン注入法または不純物拡散法によって半絶縁性基板1内に形成する。次に、サブコレクタ層2、コレクタ層3、ベース層4、エミッタ層5、そしてエミッタキャップ層6の構成材料層を、基板1の全面にエピタキシャル成長法によって形成する。次に、これらの一部をメサ構造に加工して、HBT10を形成する。一方、抵抗素子20の素子電極14、15を高い位置で取り出すための導電層12、13を、サブコレクタ層2の構成材料層42のパターニングによって形成し、素子電極14、15をこの上に形成する。次に、BCBなどの平坦化膜30を形成し、これを介して配線31、32を形成する。

(もっと読む)

整流素子およびその製造方法

【課題】 定常損失を低減しつつ耐圧を向上することのできる整流素子およびその製造方法を提供する。

【解決手段】 整流素子10は、ワイドバンドギャップ半導体よりなるn-半導体層2と、n-半導体層2にショットキー接触したショットキー電極5およびショットキー電極3と、ショットキー電極5とは異なる電位を印加可能であるカソード電極4とを備えている。ショットキー電極5とn-半導体層2との間のショットキー障壁の高さはショットキー電極3とn-半導体層2との間のショットキー障壁の高さよりも低い。ショットキー電極5およびショットキー電極3と、カソード電極4との電位差が変化することにより、ショットキー電極5とカソード電極4との間に電流を流す状態と、ショットキー電極5とカソード電極4との間に存在するn-半導体層2を空乏層化することによって電流経路を遮断する状態とを選択可能である。

(もっと読む)

整流素子およびその製造方法

【課題】 定常損失を低減しつつ耐圧を向上することのできる整流素子およびその製造方法を提供する。

【解決手段】 本発明の整流素子10は、ワイドバンドギャップ半導体よりなるn-半導体層2と、n-半導体層2内に形成され、かつ平面的に見てn-半導体層2を囲むように形成されたp型半導体層5a,5bと、n-半導体層2とショットキー接触し、かつp型半導体層5a,5bと電気的に接続されたショットキー電極3と、ショットキー電極3とは異なる電位を印加可能であり、かつn-半導体層2に電気的に接続されたカソード電極4とを備えている。ショットキー電極3とカソード電極4との電位差が変化することにより、ショットキー電極3とカソード電極4との間に電流を流す状態と、p型半導体層5a,5bに囲まれるn-半導体層2を空乏層化させてショットキー電極3とカソード電極4との間の電流経路を遮断する状態とを選択可能である。

(もっと読む)

完全空乏型SOI−MOSトランジスタの製造方法

【課題】スループットを向上させ、短チャネル効果を抑制しソースドレイン抵抗の低い完全空乏型SOI−MOSトランジスタの製造方法を提供する。

【解決手段】SOI層を形成し、酸化膜、窒化膜を形成した後、窒化膜をマスクとして酸化処理を施して窒化膜以外に酸化膜を形成し分離部を形成する工程と、ポリシリコン層(A)を形成し酸化膜を形成する工程と、ゲート部以外をエッチングしてゲートを作製する工程と、ポリシリコン層(A)側面にサイドウォールを形成し、ポリシリコン層(B)を形成する工程と、分離部のポリシリコン層(B)のポリシリコンを除去する工程と、ゲート上のポリシリコン層(B)の一部が露出するように、レジストを除去する工程と、露出したポリシリコン層(B)のポリシリコンを除去する工程と、レジストを除去し、ゲート上部の酸化膜を除去する工程と、を順次含む完全空乏型SOI−MOSトランジスタの製造方法。

(もっと読む)

整流素子およびその製造方法

【課題】 定常損失を低減しつつ耐圧を向上することのできる整流素子およびその製造方法を提供する。

【解決手段】 整流素子10は、ワイドバンドギャップ半導体よりなるn-半導体層2と、n-半導体層2内に形成され、かつn-半導体層2に取り囲まれるように形成されたn型半導体層5と、n-半導体層2にショットキー接触し、かつn型半導体層5に電気的に接続されたショットキー電極3と、ショットキー電極3とは異なる電位を印加可能であり、かつn-半導体層2に電気的に接続されたカソード電極4とを備えている。ショットキー電極3とカソード電極4との電位差が変化することにより、n型半導体層5とカソード電極4との間に電流を流す状態と、n型半導体層5とカソード電極4との間に存在するn-半導体層2を空乏層化することによってn型半導体層5とカソード電極4との間の電流経路を遮断する状態とを選択可能である。

(もっと読む)

多層構造の半導体装置及びその製造方法

【課題】多層構造の半導体装置及びこれを製造する方法を提供する。

【解決手段】多層半導体装置は、第1アクティブ半導体構造部、前記第1アクティブ半導体構造部上に形成された第1絶縁膜、前記第1絶縁膜上に形成され、前記第1アクティブ半導体構造部より高く位置する第2アクティブ半導体構造部、前記第2アクティブ構造部上に形成された第2絶縁膜、及び前記第1アクティブ半導体構造部の上部に垂直方向への厚さを有する第1オームコンタクトと、前記第2アクティブ半導体構造部の側壁に径方向へ厚さを有する第2オームコンタクトとを備える。第1オームコンタクトの垂直厚さは、第2オームコンタクトの径方向の厚さより厚く形成されている。

(もっと読む)

炭化珪素半導体装置およびその製造方法

【課題】 逆方向バイアスにおける耐圧性能を確保し、かつ順方向バイアスにおけるショットキー障壁を低くした上で、結晶性に優れてオン抵抗が低く、かつ耐熱性を十分に確保した炭化珪素半導体装置およびその製造方法を提供する。

【解決手段】 炭化珪素半導体装置10は、第1導電型の六方晶炭化珪素半導体基板1と、第1導電型の第1六方晶炭化珪素エピタキシャル層2と、第1導電型の第2六方晶炭化珪素エピタキシャル層3と、ショットキー金属層5と、オーミック金属層4とを備える。第2六方晶炭化珪素エピタキシャル層3は、第1六方晶炭化珪素エピタキシャル層2と同じ結晶構造を有し、かつ第1六方晶炭化珪素エピタキシャル層2よりも高い積層欠陥密度を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】安定した性能を示す半導体装置を提供すること。

【解決手段】酸化膜およびゲート配線により区画された半導体基板上の所定の位置に設け

られたソースおよび/またはドレインせり上げ構造を備えた半導体装置であって、

前記ソースおよび/またはドレインせり上げ構造の上端部の形状の、前記半導体基板法

線方向に沿った前記半導体基板上に対する正射投影像が、対応する前記酸化膜および前記

ゲート配線により区画された前記半導体基板上の所定の形状と略一致し、かつ、前記ソー

スおよび/またはドレインせり上げ構造のうち、前記半導体基板と平行な平面で切断して

得られる断面の、前記半導体基板法線方向に沿った前記半導体基板上に対する正射投影像

の少なくとも一つが、対応する前記酸化膜および前記ゲート配線により区画された前記半

導体基板上の所定形状よりも大きいことを特徴とする半導体装置。

(もっと読む)

半導体装置およびその製造方法

【課題】 半絶縁性GaAs基板を用いたMMICなどの半導体装置において、回路素子と金属電極の間のブレイクダウンを回避する。

【解決手段】 半絶縁性GaAs基板1の裏面に形成された裏面金属電極膜7aが、半絶縁性GaAs基板1とオーミック接合し、バイアホール6の側面に形成された側面金属電極膜7bが、半絶縁性GaAs基板1との界面でオーミック接合した構造とする。

このような構造とすることにより、裏面金属電極膜7a(または側面金属電極膜7b)がエピタキシャル抵抗部3より高電位となるような電界を印加する場合、裏面金属電極膜7a(または側面金属電極膜7b)側から半絶縁性GaAs基板1へホール注入されるのを防止することができる。これにより、エピタキシャル抵抗部3と裏面金属電極膜7a(または側面金属電極膜7b)の間がブレイクダウンするのを回避し、リーク電流が増加するのを防ぐことができる。

(もっと読む)

窒化物半導体装置

【課題】 耐圧が高く、且つオン電圧が低い、新たなIII−V族窒化物半導体装置を提供する。

【解決手段】 III−V族窒化物半導体層からなる凸形状の第1の窒化物半導体層の側面に、微結晶構造の第2の窒化物半導体層が積層し、凸形状の上面に第1のアノード電極がショットキー接合し、側面に第2のアノード電極がショットキー接合する。また第2のアノード電極と第2の窒化物半導体層との間で形成される接合のショットキーバリアの高さが、第1のアノード電極と第1の窒化物半導体層との間で形成される接合のショットキーバリアの高さより高くなるように構成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 雑音特性を劣化を抑制して高周波特性の向上を可能とする半導体装置を提供する。

【解決手段】 基体層23、基体層23上の基体層23より幅の狭い中間層22、及び中間層22上の中間層22より幅の狭い頭部21を備える第1導電型(n型)のコレクタ領域2と、頭部21の上面に配置された第2導電型(p型)のベース領域3と、ベース領域3の上部の一部に配置された第1導電型(n型)のエミッタ領域4と、基体層23の上面から頭部21の側面まで達する絶縁領域5と、絶縁領域5の上面にベース領域3の側面と接して配置されたベース電極6とを備える。

(もっと読む)

電界効果トランジスタ及びその製造方法

【課題】電極界面との接触抵抗を低減した高効率な電界効果トランジスタ等を提供する。

【課題手段】電界効果トランジスタは、窒化物半導体からなる第1の半導体層と、第1の半導体層上に形成され、第1の半導体層よりもバンドギャップエネルギーが大きく、且つ残留ドナー濃度が5×1012/cm-2以上となる窒化物半導体からなる第2の半導体層と、第2の半導体層上に各々形成されるソース電極、ゲート電極及びドレイン電極とをそれぞれ備える電界効果トランジスタであって、ソース電極及び/又はドレイン電極は、少なくとも第2の半導体層の一部に形成された段差部分上に形成されている。この構造により、段差部分でチャネル形成部分と電極との接触面積を増やし、オーミック接触の接触抵抗を下げて効率を改善できる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、高周波数帯で動作する半導体装置の特性の向上、ならびに信頼性の向上に関するものである。

【解決手段】半導体基板の表面側にキャリア走行層として積層された、サブコレクタ層、コレクタ層、ベース層、エミッタ層を用いて形成した単数もしくは複数のバイポーラトランジスタと、前記キャリア走行層の直下に設けられた絶縁層と、さらに前記絶縁層の直下に設けられた導電層と、前記導電層に到達するように形成された非貫通のバイアホールと、トランジスタの何れかの端子と電気的に接続された状態に半導体基板の表面に形成された金属配線層と、バイアホールの側壁及び底面に形成された金属配線層とを備えた構造とする。

(もっと読む)

半導体装置

【課題】 帰還容量を低減できる半導体装置を提供する。

【解決手段】 パワーMOSFETである半導体装置1は、セル9側にドレイン電極45が形成され、シリコン基板3の裏面にソース電極7が形成されている。ソース領域13とベース領域25を短絡するショート電極35の一部は、第1の層間絶縁膜31を介してゲート電極17の上面53の上に位置している。ソース領域13からドレイン領域11へ向かう方向に関して、ショート電極35の側面47の位置が、ゲート電極17のドレイン領域側の側面51の位置と同じにされている。

(もっと読む)

評価用半導体デバイス、評価用半導体デバイスの作製方法、半導体デバイスの評価方法

【課題】 動作(駆動)中の半導体デバイスの動作状況を測定して、上記半導体デバイスをより正確に価できる評価用半導体デバイス、評価用半導体デバイスの作製方法、半導体デバイスの評価方法を実現する。

【解決手段】 半導体基板2上に設けられた任意の半導体デバイスの、ドレイン、ソース、ゲートの各電極3a、4a、5と、各電極3a、4a、5間に形成されたキャリアの分布状態が制御されるアクティブ領域2aとを設ける。各電極3a、4a、5上を覆う絶縁膜7を設ける。観察すべきアクティブ領域2aを露出させた露出面1aを形成する。各電極3a、4a、5を外部と接続させるために、絶縁膜7中に配線部3b、4b、5aをそれぞれ設ける。

(もっと読む)

窒化物半導体装置

【課題】 耐圧が高く、且つオン電圧の低い、新たなIII−V族窒化物半導体装置を提供する。

【解決手段】 半絶縁性または絶縁性基板上に積層したIII−V族窒化物半導体からなる第1の窒化物半導体層と、第1の窒化物半導体層よりも低い温度で成膜した第2の窒化物半導体層と、凹部内に露出する第1の窒化物半導体層上にショットキー接合するショットキーバリア高さの低い第1のアノード電極と、第1のアノード電極に接続し、第2の窒化物半導体層にショットキー接合する第1のアノード電極と同一あるいは異なる金属からなり、ショットキーバリア高さの高い第2のアノード電極と、第1あるいは第2の窒化物半導体層にオーミック接合するカソード電極とを備える。

(もっと読む)

バイポーラトランジスタ及びその形成方法

【課題】エミッタ端子及びベース端子が同一な高さを有する高速バイポーラトランジスタを提供する。

【解決手段】高速バイポーラトランジスタは、ベースのためのシリコン−ゲルマニウム膜(25a)をコレクタのための半導体膜(19)上に形成し、エミッタ端子及びコレクタ端子のための接触窓を有する層間絶縁膜(27)(29)を形成し開口する。ポリシリコンを蒸着した後ベース、エミッタ接触窓(35b)(35a)内にポリシリコンを充填し、イオン注入熱処理工程により、エミッタ拡散部(36)を形成する。その後、平坦化処理により、同一高さをもつポリシリコンエミッタ端子及びポリシリコンベース端子を形成する。更に、エミッタ及びベース接触窓と、金属配線との間に安定的なシリサイド膜を形成でき、低抵抗なエミッタ、ベース接触窓を持つバイポーラトランジスタを形成できる。

(もっと読む)

121 - 140 / 155

[ Back to top ]