Fターム[4M104GG07]の内容

Fターム[4M104GG07]に分類される特許

1 - 20 / 62

半導体装置の製造方法

【課題】SiC半導体基板の裏面電極は、低コンタクト抵抗を実現するために、ニッケル等のシリサイド形成用メタル膜を堆積後、PDAとして摂氏1000度程度の熱処理を必要とする。この熱処理を通常の熱処理やRTAで実行する場合には、ウエハの表面側がアルミニウム等の融点を超えるため、アルミニウム膜等の形成前に実施しなければならないという制約がある。また、既存の紫外線レーザを用いたレーザアニールでは、コンタクト抵抗を十分に下げられないという問題がある。

【解決手段】本願の一つの発明は、SiC基板の表面側にアルミニウム系メタル膜が形成された状態で、裏面にシリサイド形成用メタル膜を成膜し、この裏面に対してレーザビームによってシリサイド化処理を実行する半導体装置の製造方法であって、このレーザビームを、前記シリサイド形成用メタル膜を実質的に透過しない波長域に属する可視光とするものである。

(もっと読む)

炭化ケイ素デバイス用のエッジ終端構造およびエッジ終端構造を含む炭化ケイ素デバイスの製造方法

【課題】炭化ケイ素デバイスの改善されたエッジ終端構造を提供する。

【解決手段】炭化ケイ素半導体デバイス用のエッジ終端構造は、少なくとも炭化ケイ素ベース接合を部分的に取り囲んで、炭化ケイ素層中において、所定間隔で配置された複数の同心円のフローティングガードリング34を有すると共に、フローティングガードリング上に設けられた絶縁層、及びフローティングガードリング同士の間でかつ炭化ケイ素層の表面の近くに設けられた炭化ケイ素表面電荷補償領域38を有する。炭化ケイ素層上に窒化ケイ素層56が設けられ、窒化ケイ素層上に有機保護層66が設けられる。酸化膜層が窒化ケイ素層と炭化ケイ素層の表面との間に存在してもよい。エッジ終端構造の形成・製造方法を開示されている。

(もっと読む)

半導体素子

【課題】III族窒化物半導体を用いて形成され、優れた特性を有する半導体素子を提供する。

【解決手段】半導体素子が、電子を多数キャリアとするように構成されてなる第1半導体層の一方主面上に、それぞれが電気的に接続されてなる複数の単位アノード部、を有するアノード部と、それぞれが電気的に接続されてなる複数の単位カソード電極、を有するカソード部と、を備え、複数の単位アノード部のそれぞれと複数の単位カソード電極のそれぞれとが交互に配置された電極列が形成されてなり、複数の単位アノード部のそれぞれと第1半導体層との接合部がそれぞれ第1と第2の接合部からなり、第1接合部は、第1半導体層と接続する単位アノード部部分が正孔が多数キャリアの第2半導体層であるP−N接合部であり、第2接合部は、第1半導体層と接続する単位アノード部部分が金属によって構成されたショットキー接合部である、ようにした。

(もっと読む)

半導体素子

【課題】III族窒化物半導体を用いて形成され、優れた特性を有する半導体素子を提供する。

【解決手段】半導体素子が、ワイドバンドギャップ材料を用いて電子を多数キャリアとするように構成されてなる第1半導体層の一方主面上に、それぞれが電気的に接続されてなる複数の単位アノード部、を有するアノード部と、それぞれが電気的に接続されてなる複数の単位カソード電極、を有するカソード部と、を備え、複数の単位アノード部のそれぞれと複数の単位カソード電極のそれぞれとが交互に配置された電極列が形成されてなり、複数の単位アノード部のそれぞれの、少なくとも第1半導体層と接合する部分が、所定の半導体材料を用いて正孔を多数キャリアとするように構成されてなる第2半導体層であり、第1半導体層と第2半導体層との接合部においてはP−N接合が形成されてなる、ようにした。

(もっと読む)

高耐圧半導体装置

【課題】高耐圧半導体装置の大型化を招くことなく、従来の高耐圧半導体装置900の場合よりも「気中放電による逆耐圧の低下」を抑制することが可能な高耐圧半導体装置を提供する。

【解決手段】炭化珪素からなるn型の半導体層110と、バリアメタルからなる第1電極層層128と、第2電極層130と、p型のリサーフ層116と、p+型のエッジターミネーション層120と、リサーフ層116の内部における、エッジターミネーション層120の周囲を離間して囲む位置に形成されたp+型の第1ガードリング層122と、半導体層110の表面における、リサーフ層116の周囲を離間して囲む位置に形成されたp型の第2ガードリング層118と、半導体層110の表面上において第1電極層128を取り囲む領域に形成された絶縁層124とを備え、第2ガードリング層118が絶縁層124の外周近傍まで形成されている高耐圧半導体装置100。

(もっと読む)

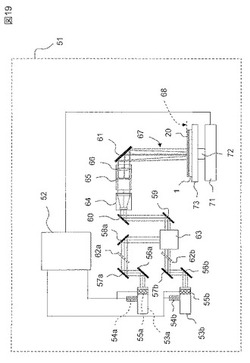

炭化ケイ素パワーデバイスを有する半導体ウェハを処理する方法

【課題】

ドーパントが注入されたSiC基板がオーミックコンタクトの形成前に薄くされる場合には、オーミックコンタクトを形成するために堆積された金属は、基板上に堆積されたときにオーム特性を持たないことがある。

【解決手段】

炭化ケイ素半導体デバイスを形成する方法は、第1の厚さを有する炭化ケイ素基板の第1の表面に半導体デバイスを形成するステップと、前記第1の表面にキャリア基板を取り付けるステップとを含む。さらに、前記炭化ケイ素基板を、前記第1の厚さ未満の厚さまで薄くするステップ、前記第1の表面とは反対側の前記薄くされた炭化ケイ素基板の表面に金属層を形成するステップ、前記金属層を局所的にアニールするステップを含む。前記炭化ケイ素基板は、個片化された半導体デバイスを提供するために、個片化される。

(もっと読む)

高耐圧半導体装置

【課題】従来の高耐圧半導体装置の場合よりも耐圧の低下を抑制することが可能な高耐圧半導体装置を提供する。

【解決手段】炭化珪素からなるn型の半導体層110と、バリアメタル層128と、第2電極層130と、p型のリサーフ層116と、p+型のエッジターミネーション層120と、リサーフ層116の内部における、エッジターミネーション層120の周囲を離間して囲む位置に形成されたp+型の第1ガードリング層122と、半導体層110の表面における、リサーフ層116の周囲を離間して囲む位置に形成されたp型の第2ガードリング層118とを備え、最内周の第1ガードリング層122とエッジターミネーション層120との間隔が3μm〜5μmの範囲内にある高耐圧半導体装置100。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置の反りを抑制しながら、衝撃によるクラック等の破壊を防止することを目的とする。

【解決手段】動作領域Eの形成面sf1に対する裏面sf2に形成された凹部20a内にさらに凹部20bを設けて、凹部20の内部に段差を設ける構成とすることにより、凹部20の側面の付け根部分の厚みW4を厚くすることができ、半導体基板10の寸法を抑えつつ横からの応力に対する強度が向上し、反りを抑制しながら、衝撃によるクラック等の破壊を防止することができる。

(もっと読む)

半導体装置

【課題】トレードオフの関係にある臨界オフ電圧上昇率dV/dtとゲート感度との関係を改善した半導体装置を提供する。

【解決手段】少なくとも、ゲートトリガ電流IGTの経路となるベース層(P型ベース領域、P型半導体領域P1)のゲート電極M1bとのオーミック接触面である高濃度不純物層を、高融点金属シリサイド層LMで形成する。

(もっと読む)

炭化ケイ素半導体デバイスのためのエッジ終端構造及びその製造方法

【課題】炭化ケイ素デバイスのためのエッジ終端構造において、酸化膜などの絶縁層の境界面電荷の悪影響を中和し、多重フローティングガードリング終端では、この酸化膜電荷の変化に対する影響を少なくし、又は影響をなくす。

【解決手段】炭化ケイ素ベースの半導体接合に近接し、この半導体接合から間隔をおいて配置された、炭化ケイ素層中の複数の同心円のフローティングガードリングを有する。酸化膜などの絶縁層が、これらのフローティングガードリング上に設けられ、炭化ケイ素表面電荷補償領域が、これらのフローティングガードリング間に設けられ、この絶縁層に隣接している。かかるエッジ終端構造の製造方法もまた提供される。

(もっと読む)

アッド‐オン層形成方法

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、堆積可能なアッド‐オン層形成方法を提供することを目的とする。

【解決手段】堆積可能なアッド‐オン層形成方法であって、第一半導体基板の取り外し層の形成、取り外し層の上の第一半導体基板に多くのドーピング領域の形成、ここで多くのドーピング層の形成は、第一電導型を有するように、ドーピングされ、取り外し層の上の第一半導体基板の第一ドーピング層の形成、第一電導型に対する第二電導型を有するようにドーピングされ、第一ドーピング層の上の第一半導体基板に最低中間ドーピング層の形成、及び中間ドーピング層上の第一半導体基板に最低第三ドーピング層の形成からなり、第三ドーピング層上に第一の電導性ブランケット層の形成、第一電導ブランケット層上に第二の電導性ブランケット層の形成、及び第二電導性ブランケット層が第二半導体基板の対応する電導性上部層と接触するように、第一半導体基板を第二半導体基板への取り付け、からなる。

(もっと読む)

炭化ケイ素半導体デバイスのためのエッジ終端構造及びその製造方法

【課題】炭化ケイ素デバイスのためのエッジ終端構造において、酸化膜などの絶縁層の境界面電荷の悪影響を中和し、多重フローティングガードリング終端では、この酸化膜電荷の変化に対する影響を少なくし、又は影響をなくす。

【解決手段】炭化ケイ素ベースの半導体接合に近接し、この半導体接合から間隔をおいて配置された、炭化ケイ素層中の複数の同心円のフローティングガードリングを有する。酸化膜などの絶縁層が、これらのフローティングガードリング上に設けられ、炭化ケイ素表面電荷補償領域が、これらのフローティングガードリング間に設けられ、この絶縁層に隣接している。かかるエッジ終端構造の製造方法もまた提供される。

(もっと読む)

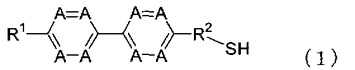

金属電極および該金属電極を有する有機半導体素子

【課題】本発明は、有機高分子等の半導体薄膜形成材料が単結晶でなく、多結晶であっても、印刷方法により金属電極上に安定で良好な有機半導体薄膜を簡便に形成することができ、性能の優れた有機半導体素子を提供することを課題とする。

【解決手段】本発明の金属電極は、下記式(1)で表される化合物を含有する溶液を用いて形成された表面処理層を有することを特徴とする。 (もっと読む)

(もっと読む)

半導体装置

【課題】プロセスの複雑化を招くことなく、サイリスタとしての機能を実現することの出来る半導体装置を提供することを課題の一とする。

【解決手段】リセット動作及び初期化動作により所定の電位が記憶されたメモリ回路を有する半導体装置において、トリガー信号の供給に応じて、メモリ回路の書き換えが行われる回路を設ける構成とする。そして、メモリ回路の書き換えにより、半導体装置に流れる電流を負荷に流す構成とすることで、サイリスタとしての機能を実現しうる半導体装置とする。

(もっと読む)

半導体素子およびその製造方法

【課題】ウェットエッチングにより形成される配線の線幅のばらつきが抑えられた半導体素子を提供する。

【解決手段】半導体素子の製造方法は、半導体層14上に電極11を形成する工程と、半導体層14上に、電極11に達する配線接続孔12aを有し、配線接続孔12aの周りに凹部12bが形成された層間絶縁膜12を形成する工程と、層間絶縁膜12上から配線材料18を堆積する工程であって、層間絶縁膜12の凹部12bに対応して配線材料18に凹部18aが形成される工程と、配線材料18上に、電極11に配線接続孔12aを介して接続される配線13を形成するためのレジスト膜19を、配線材料18に形成された凹部18aを覆うように形成する工程と、レジスト膜19をマスクとしてウェットエッチングを行い、配線材料18を選択的に除去して配線13を形成する工程と、を含む。

(もっと読む)

半導体装置

【課題】高温度における電圧上昇率(dV/dt)耐量を向上し、誤動作を防止することができるサイリスタを提供する。

【解決手段】半導体層(20)の一方の主面において、第1の導電型(p型)をもつ第1の半導体層(21)上に第1の主電極(11)が形成され、前記第1の導電型と反対の第2の導電型(n型)をもち前記第1の半導体層中に局所的に形成された第2の半導体層(24)と、該第2の半導体層と前記第1の半導体層とに接続するゲート電極(13)とが、前記第1の主電極が形成されていない箇所に形成され、

前記半導体層の他方の主面において、第2の主電極(12)が形成され、

前記第1の主電極と前記第2の主電極との間に電流が流れる、サイリスタとしての動作をする半導体装置であって、

前記ゲート電極と前記第1の主電極との間に接続され、SBD(31、32)から成る双方向ダイオードを具備することを特徴とする半導体装置。

(もっと読む)

半導体装置

【課題】オン電圧を低減した半導体装置を提供する。

【解決手段】第1導電型の第1の半導体層と、前記第1の半導体層の上に設けられた第2導電型の第2の半導体層と、前記第1の半導体層の上に前記第2の半導体層と接して設けられた前記第1の半導体層よりも不純物濃度の高い第1導電型の第3の半導体層と、前記第2の半導体層に接続された第1の金属層と、前記第3の半導体層に接続され前記第1の金属層とは異なる金属からなる第2の金属層と、を有する第1の主電極と、を備えたことを特徴とする半導体装置が提供される。

(もっと読む)

半導体装置の製造方法

【課題】製造工程中に半導体基板に発生する欠陥を低減し、逆方向リーク電流を小さくすることが容易な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板110を準備する半導体基板準備工程と、半導体基板110の第2主面にn型不純物を導入する不純物導入工程と、半導体基板110の第1主面にバリアメタル113を形成する金属薄膜形成工程と、半導体基板110の第2主面側から光エネルギーを照射して半導体基板110をバリアメタルの全部又は一部がシリサイド化される温度に加熱することで、不純物を活性化するとともに、バリアメタルの全部又は一部をシリサイド化するランプアニール工程とをこの順序で含む。

(もっと読む)

半導体装置とその製造方法

【課題】柱状半導体層が微細化されて高集積化されても、コンタクト抵抗の増加を抑制する構造の半導体装置を提供する。

【解決手段】半導体装置は、基板(半導体基板1)と、半導体基板1上に設けられた、半導体柱状部(柱状半導体層3)と、の天面に接するように設けられた、柱状半導体層3と同径以下のコンタクト柱状部(コンタクト層7)と、この天面に設けられた凹部をと備えるものである。

(もっと読む)

III族窒化物系化合物半導体素子及びその製造方法

【課題】積層された各層に平面的に電極が形成された、III族窒化物系化合物半導体素子

【解決手段】pnpトランジスタ100は、基板10の上に、図示しないバッファ層を介して、p型GaN層11、n型GaN層12、p型GaN層13を順に形成した後、ケミカルポリシングにより露出部である傾斜面11t、12t及び13tを形成し、そこに各々、コレクタ電極C、ベース電極B、エミッタ電極Eを形成して構成したものである。図1のpnp型トランジスタ100は、水平形状が1辺が500μmの矩形状で、その外周の1辺に水平面と10度の角度を成す傾斜面が形成されている。p型GaN層11、n型GaN層12及びp型GaN層13の膜厚はいずれも1μmであり、p型GaN層11の傾斜面11t、n型GaN層12の傾斜面12t及びp型GaN層13の傾斜面13tの幅はいずれも約5.8μmである。

(もっと読む)

1 - 20 / 62

[ Back to top ]