Fターム[4M104GG15]の内容

Fターム[4M104GG15]に分類される特許

41 - 56 / 56

メタルベースナノワイヤトランジスタ

メタルベーストランジスタを示す。該トランジスタは、第一電極2及び第二電極6と、該第一及び第二電極間の電流流れを制御するベース電極3とを備える。第一電極2を半導体材料から作製する。ベース電極は、第一電極を形成する半導体材料の上に堆積した金属層である。本発明によれば、第二電極は、ベース電極3と電気接触した半導体ナノワイヤにより形成される。  (もっと読む)

(もっと読む)

犠牲マスキング構造を用いた半導体装置の製造方法

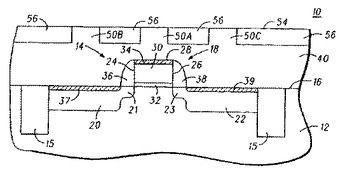

犠牲マスキング構造(50)を用いた半導体装置(10)の製造方法を提供する。半導体デバイスは半導体基板(12)から形成され、誘電材料からなる層(40)は半導体基板(40)および半導体デバイスの上に形成される。誘電材料からなる層(40)は、半導体基板(12)上に直接に形成される場合もあれば、中間層によって半導体基板(12)から間隔があいている場合もある。側壁を有するポストまたは凸部(50)が、誘電材料からなる層(40)から形成される。好ましくは誘電材料からなる層(40)とは異なる電気絶縁材料(52)がポスト(50)の側壁に隣接して形成される。電気絶縁材料(52)は平坦化され、ポスト(50)が除去されて、半導体デバイスの一部または中間層材料の一部を露出させ得る開口を形成する。導電性材料が開口に形成される。  (もっと読む)

(もっと読む)

機能性デバイス及びその製造方法

【課題】ナノメートルサイズの機能性構造体からなり、この機能性構造体を外部電極に接続する接続抵抗を小さく抑えることができ、かつ、様々な機能性構造体の構造設計に与える制約を最小限に抑えることのできる配線手段を備えた機能性デバイス及びその製造方法を提供すること。

【解決手段】絶縁層2が形成された基板1に、例えば1〜2μmの間隙を有する電極3と4が形成されているものとする。これらの電極上及び電極間に金属性のカーボンナノチューブを分散させた液を被着させた後、電極間に交流電圧を印加して、電極間を架橋するようにカーボンナノチューブを配置する。次に、やや大きい電圧を印加してカーボンナノチューブに欠除部8を形成し、カーボンナノチューブ6及び7に区分する。欠除部8に面したカーボンナノチューブ6及び7の開口部において、機能性構造体9の被内包部9a及び9eをそれぞれカーボンナノチューブ6及び7に内包させる。

(もっと読む)

半導体装置及びその製造方法

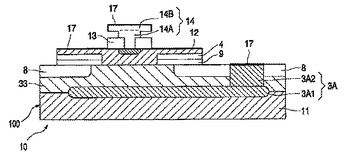

【課題】 ヘテロ接合半導体素子と別の半導体素子とが同一基板上に集積され、かつ、この別の半導体素子の電極取り出し構造が改良された半導体装置及びその製造方法を提供すること。

【解決手段】 前記別の半導体素子の一例である抵抗素子20を構成する抵抗層11を、イオン注入法または不純物拡散法によって半絶縁性基板1内に形成する。次に、サブコレクタ層2、コレクタ層3、ベース層4、エミッタ層5、そしてエミッタキャップ層6の構成材料層を、基板1の全面にエピタキシャル成長法によって形成する。次に、これらの一部をメサ構造に加工して、HBT10を形成する。一方、抵抗素子20の素子電極14、15を高い位置で取り出すための導電層12、13を、サブコレクタ層2の構成材料層42のパターニングによって形成し、素子電極14、15をこの上に形成する。次に、BCBなどの平坦化膜30を形成し、これを介して配線31、32を形成する。

(もっと読む)

半導体デバイスおよびその製造方法

本発明は、シリコンからなる基板(11)および半導体本体(12)を有し、この半導体本体(12)は、トランジスタ(T)を有する能動領域(A)および該能動領域(A)を囲む受動領域(P)を具え、前記半導体本体(12)の表面から埋め込まれた金属材料からなる第1導電領域(2)に接続している金属材料からなる第2導電領域(1)が設けられ、これによって、前記第2導電領域(1)が、前記半導体本体(12)の表面で電気的に接続可能とされる半導体デバイス(10)に関するものである。本発明によれば、前記第2導電領域(1)は、前記半導体本体(12)の能動領域(A)の場所で作られる。このような方法で、非常に低い埋込抵抗は、前記周囲のシリコンとは完全に異なる結晶特性を有する金属材料を用いて、前記半導体本体(12)の能動領域(A)の中で局所的に生成されることができる。これは、本発明に従う方法を用いることによって可能となる。そのような埋込低抵抗は、バイポーラトランジスタおよびMOSトランジスタの双方にとって多くの利点を提案する。  (もっと読む)

(もっと読む)

バンク構造、配線パターン形成方法、デバイス、電気光学装置、及び電子機器

【課題】 幅の異なる領域を有するパターン形成領域に機能液を配置するに際し、形成される膜パターン間での膜厚さを無くした、バンク構造体、膜パターン形成方法、デバイス、電気光学装置、及び電子機器を提供する。

【解決手段】 機能液が配置され流動するパターン形成領域Pをバンク34により区画するバンク構造1である。パターン形成領域Pは、第一のパターン形成領域56と、第一のパターン形成領域56に連続し、かつ第一のパターン形成領域56より幅が広い第二のパターン形成領域55とからなり、第二のパターン形成領域55には、第二のパターン形成領域55を仕切って機能液の流動方向を規制する仕切りバンク34aが少なくとも一つ設けられ、仕切りバンク34aによって規制された機能液の流動方向と略直交する方向の仕切り幅Hが、第一のパターン形成領域56の幅H2の±20%以内に形成されてなる。

(もっと読む)

半導体装置

【課題】 良好な高周波信号の分離特性を有する半導体装置を提供する。

【解決手段】 半導体素子がそれぞれ形成された複数の素子領域1と、2つの素子領域1を分離する素子分離領域2とを備え、素子領域1及び素子分離領域2は、半導体基板3の表面側に形成され、素子分離領域2は、電位が固定された金属層5と、半導体基板3の表面から深さ方向に延び、金属層5を覆う絶縁層6とを有し、金属層5は、深さ方向に向けて絶縁層6から突出している。

(もっと読む)

バイポーラトランジスタおよびその製造方法

本発明は、高周波バイポーラトランジスタ(1)に関し、この高周波バイポーラトランジスタ(1)は、少なくとも、エミッタ接続領域(3)に隣接するエミッタ接点(2)を1つと、ベース接続領域(5)に隣接するベース接点(4)と、コレクタ接続領域(7)に隣接するコレクタ接点(6)とを有する。コレクタ接続領域として埋込層(7)が設けられ、この埋込層が、コレクタ接点(6)を、コレクタゾーン(14)に連結する。本発明は、このような(15)高周波バイポーラトランジスタ(1)の製造方法にも関する。本発明の特徴は、埋込層(7)上に、シリサイド領域(8)が設けられ、このシリサイド領域が、低い抵抗で、コレクタ接点(6)をコレクタゾーン(14)に接続することである。  (もっと読む)

(もっと読む)

化合物半導体装置およびその製造方法

【課題】 HBTとFETを1チップに集積化する際、HBTのエミッタキャップ層をFETのチャネル層としており、FETのピンチオフ性が悪く相互インダクタンスgmが低い。また、複数回のイオン注入、アニール、ベースペデスタルの形成、さらには2回のエピタキシャル成長を行うなど製造工程が複雑であった。

【解決手段】 HBTのエミッタ層とFETのチャネル層を、同一のn型InGaP層とする。また、HBTのベース層であるp+型GaAs層を、FETのp型バッファ層として利用する。これにより、FETのピンチオフ性が良好となり相互インダクタンスgmを高めることができる。またエピタキシャル成長が1回で、イオン注入、アニール工程も不要のため製造工程も簡素化でき、ウエハコストも低減できる。

(もっと読む)

CMOS製造技術と両立可能なバイポーラデバイス

【課題】性能を向上する新規なバイポーラデバイスを提供する。

【解決手段】本発明は、バイポーラデバイス30を開示する。エミッタ33が半導体基板に形成される。コレクタ34が、エミッタ33から横方向に空間を置いて基板に設けられる。ゲート端子38は基板上に形成され、エミッタ33とコレクタ34間の空間を規定する。外部ベース35は、エミッタ33またはコレクタ34の何れか一方から所定の距離を隔てて、基板上に形成される。外部ベース35は、エミッタ33またはコレクタ34の何れか一方から所定の距離を有して基板上に形成され、基板に設けた分離構造31で周囲を囲まれた穴によって活性領域32を規定し、この活性領域32に、ベース35,エミッタ33,コレクタ34およびゲート端子38が配置される。

(もっと読む)

ヘテロ接合半導体装置及びその製造方法

【課題】 積層方向における電極位置の高低差を緩和或いは解消し易く、製造工程の増加や生産性の低下を抑え易く、電気的特性の悪化を招かない構造を有するヘテロ接合半導体装置及びその製造方法を提供すること。

【解決手段】 サブコレクタ層、コレクタ層、ベース層及びエミッタ層が、この順に基板上に積層されてなるHBTにおいて、

ベース層14と同レベル位置のベース層構成材料層14a上、コレクタ層13と同レ ベル位置のコレクタ層構成材料層13a上、コレクタ層13の途中レベル位置のコレク タ層構成材料層13a上、又は、エミッタ層15又はエミッタキャップ層16と同レベ ル位置のエミッタ層構成材料層15a上又はエミッタキャップ層構成材料層16a上に コレクタ電極7が形成され、

このコレクタ電極7とサブコレクタ層12とが、オーミックアロイ法によって形成さ れた導電領域21を介して電気的に接続されていること

を特徴とする、HBT10a。

(もっと読む)

帯状のチャネルを有する半導体装置及びその製造方法

本発明は、基板(11)及び半導体本体(2)から成る半導体装置(10)であって、半導体本体(2)は、電界効果トランジスタが形成されるシリコンの帯状の半導体領域(3、3A、3B)を有し、第1導電型のソース領域(4)と、第1導電型と反対の第2導電型のチャネル領域(33)と、第1導電型のドレイン領域(5)とが連続して配置されており、続いて、帯状の半導体領域(3、3A、3B)の縦方向に示されるように、ゲート絶縁体(6)を具えたチャネル領域(33)が設けられ、第1接続領域(7A)を設けた第1ゲート電極(7)が、帯状の半導体領域(3、3A、3B)の第1垂直側部にあり、第2接続領域(8A)を設けた第2ゲート電極(8)が、帯状の半導体領域(3、3A、3B)の第1垂直側部とは反対の第2垂直側部にある半導体装置デバイスに関する。本発明によれば、第1及び第2ゲート電極(7、8)は、接続領域(7A、8A)の幅を超える帯状の半導体領域(3、3A、3B)の両側の空間を完全に満たす。好適な実施例において、ゲート電極(7、8)は、各々帯状の半導体領域(3、3A、3B)の横側に接している。本発明による半導体装置(10)は、非常にコンパクトで45nm未満の範囲に適しており、製造が容易である。  (もっと読む)

(もっと読む)

CMOS工程と統合されることができる高い利得を有するバイポーラ接合トランジスタ及びその形成方法

【課題】CMOS工程に統合されることができる高利得を有するバイポーラ接合トランジスタ及びその形成方法を提供する。

【解決手段】CMOS工程に統合されることができる本発明のバイポーラ接合トランジスタ形成方法は、CMOS工程でマスク工程及びイオン注入工程を追加することによってベース領域を形成する。これによって、ベース領域のドーピングレベル及び幅を高周波回路に最適の状態で調節することができるので、高利得の高周波回路に適するバイポーラ接合トランジスタを形成することができる。

(もっと読む)

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供する。

【解決手段】基板101上に第1の膜102を形成する工程と、前記第1の膜102上にマスク材料を含有する溶液を吐出して前記第1の膜102上にマスク103を形成する工程と、前記マスク103を用いて前記第1の膜102をパターニングして前記基板101上に塗れ性の低い領域104と塗れ性の高い領域105を形成する工程と、前記マスク103を除去する工程と、前記塗れ性の低い領域104に挟まれた前記塗れ性の高い領域105に、絶縁膜、半導体膜又は導電膜材料を含有する溶液106を吐出して絶縁膜、半導体膜又は導電膜のパターンを形成する工程とを有する。

(もっと読む)

半導体装置及びその製造方法

【課題】メッキ膜厚のウェハ面内均一性を向上させる。

【解決手段】本発明の例に関わる半導体装置は、メタル配線を用いた多層配線構造を有する半導体集積回路が形成され、各々が独立したチップになる複数のチップ領域11と、メタル配線を用いた多層配線構造を有し、複数のチップ領域の各々を取り囲む複数のチップリング12とを備え、複数のチップリング12は、互いに電気的に接続される。

(もっと読む)

バイポーラ・トランジスタを有する半導体装置の製造方法及びバイポーラ・トランジスタを有する装置

本発明は、バイポーラ・トランジスタ装置(10)の製造に関し、この装置内に、絶縁層(13)内のウィンドウ内に存在し絶縁層(13)を覆って横方向に延びる多結晶シリコン領域(14)を用いて、エミッタが形成される。シリコン領域(14)、並びに、絶縁領域(13)及びシリコン領域(14)のスタックに隣接する別のシリコン領域(12)が、この構造を覆って堆積される金属層(16)によってシリサイド化される。形成されるシリサイド(17)のブリッジを回避する手段がスタックの側面に形成される。本発明によれば、形成されるシリサイドのブリッジを回避するための手段は、シリコン領域(14)の上面とスタックの側面の表面に沿った他のシリコン領域(12)の上面との間の間隔が、絶縁層(13)と半導体層(14)の厚さの合計よりも大きく形成されるように、スタックの側面が構築されることを備える。スタック側面の正又は負の傾斜によって増大された通路によりシリサイドのブリッジが回避される。好ましい実施形態は、スタックの側面がどのように構築されるかに関する。  (もっと読む)

(もっと読む)

41 - 56 / 56

[ Back to top ]