Fターム[4M113AD01]の内容

超電導デバイスとその製造方法 (1,906) | 超電導回路 (453) | 回路構成 (61)

Fターム[4M113AD01]の下位に属するFターム

Fターム[4M113AD01]に分類される特許

1 - 10 / 10

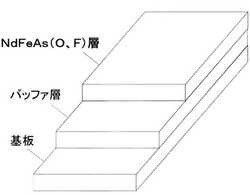

超伝導体構造、その製造方法、及び電子素子

【課題】鉄砒素系超伝導体の高品質な超伝導薄膜を備えた超伝導体構造、その製造方法、及び電子素子を提供すること。

【解決手段】基板と、前記基板上に形成され、III-V族半導体から成るバッファ層と、前記バッファ層上に形成され、下記式(1)で表される組成を有する超伝導薄膜と、を含み、前記超伝導薄膜におけるAs−As間隔は、前記III-V族半導体におけるV族原子間距離の約1倍であることを特徴とする超伝導体構造。式(1)LnFeAsO1-pFq(式(1)において、Lnは1種以上のランタノイド元素であり、0<p<1、0≦q<1)

(もっと読む)

原子捕捉装置および原子捕捉方法

【課題】電流を駆動するための構造を用いることなしに、原子の閉じ込めが行えるようにする。

【解決手段】原子捕捉装置は、超伝導材料から構成されて平板上に形成された捕捉部101と、捕捉部101を超伝導転移温度以下に冷却する冷却部102と、捕捉部101に均一な磁場131を印加する磁場印加部103とを備える。冷却部102を動作させて捕捉部101の冷却し、捕捉部101を超伝導転移温度以下に冷却したら、磁場印加部103により捕捉部101に均一な磁場を印加する。この磁場の印加により、超伝導体である捕捉部101には、マイスナー効果により内部に磁場を浸入させないようにマイスナー電流が誘起される。これにより、捕捉部101においては、表面から法線方向および捕捉部101の中央部から周辺方向に向けて磁場の強さが増加する不均一な磁場が形成される。

(もっと読む)

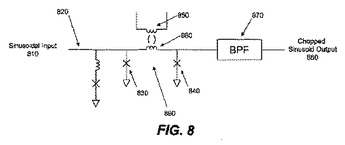

単一磁束量子論理で量子ビットを制御するための方法および装置

一実施形態では、本開示は、量子ビットを磁束量子論理ゲートに連結することにより、量子ビットを共鳴させたりそれを止めさせたりすることによって、量子ビットのエネルギー状態を制御するための方法および装置に関する。量子ビットは、ポンプ信号と、別の量子ビットと、または何らかの量子論理ゲートと共鳴状態になり得る。別の実施形態では、本開示は、RSFQ論理で、またはRSFQと量子ビットとの間のインターフェースを通して、量子ビットを制御するための方法に関する。  (もっと読む)

(もっと読む)

単一磁束量子可変遅延回路

【課題】磁束量子を情報担体とする単一磁束量子回路において、回路の正常動作に必須となる各単一磁束量子信号の適切なタイミングを維持するために、単一磁束量子の伝播時間を自由に可変する方法を提供する。

【解決手段】分岐回路と遅延時間の異なる複数のジョセフソン伝送線路またはマイクロストリップライン、それらを選択するスイッチ回路および合流回路で可変遅延回路を構成する。さらに最小変化幅の異なる複数の可変遅延回路を直列に接続して、可変幅の分解能と可変範囲を同時に向上させる。また、シフトレジスタ回路によるシリアル−パラレル変換により、複数の可変遅延回路を制御する制御線の本数を大きく削減する。

(もっと読む)

ジョセフソン接合素子、その形成方法、および超電導接合回路

【課題】本発明は、ジョセフソン接合素子、その形成方法、および超電導接合回路に関し、IcRn積を向上することを目的とする。

【解決手段】ジョセフソン接合素子は、基板11上に形成された下部電極層12と、絶縁膜13と、下部電極層12の一端に形成された斜面を覆うバリア層14と、バリア層14を覆う上部電極層15を有し、超電導接合部16が形成される。下部電極層12及び上部電極層15は、(RE)1(AE)2Cu3Oyを主成分とする酸化物超電導材料からなり、元素REはY、La、Pr、Nd、Sm、Eu、Gd、Dy、Ho、Er、Tm、Yb、およびLuからなる群のうち少なくとも1種、元素AEがBa、Sr、およびCaからなる群のうち少なくとも1種である。バリア層14は、元素RE、元素AE、Cu、及び酸素を含む材料からなり、この材料中のカチオンのうち、Cu含有量が35〜55原子%、かつ元素RE含有量が12〜30原子%の範囲に設定され、かつ下部電極層12及び上部電極層15の組成と異なる。

(もっと読む)

超電導量子アンテナ

本発明は、量子干渉フィルタ(51)、少なくとも1つの低温トランジスタ(51)および一次アンテナ構造(54、55、59、60)、回路装置から電磁波を誘導する手段(51、52、53a、53b)、冷却要素および断熱体(57)を備えた電磁波用アンテナに関する。前記超電導量子干渉フィルタ(51)および前記トランジスタ(52)は能動要素である。前記一次アンテナ構造は、電磁波が前記一次アンテナ構造(54、55、59、60)に入射すると、前記能動要素(51、52)のうち少なくとも1つの出力部において誘導電磁波が生じるように、前記能動要素(51、52)のうち少なくとも1つに接続されている。前記回路装置の少なくとも一部分および前記一次アンテナ構造(54、55、59、60)の少なくとも一部分は、断熱されている。前記断熱体(57)は、電磁波の周波数に対して透過性を有する。前記冷却要素は、前記回路装置の少なくとも一部分を、超電導材料のうち少なくとも1つの転移温度よりも低い温度まで冷却するように構成されている。  (もっと読む)

(もっと読む)

超伝導ランダムアクセスメモリおよびその製造方法

【課題】 大部分の製造工程に高温プロセスを採用することができ、また、メモリセルの小型化が可能であり、さらに、直流のバイアス電流供給線路に効率的にインダクタンスを形成でき且つこのバイアス電流による磁場の影響を受けない、超高速で、大規模な、超伝導ランダムアクセスメモリのデバイス構造を提供する。

【解決手段】 最上層の超伝導グランド層である第1の超伝導グランド層(M7)上に、ジョセフソン接合(JJ)を含んだ超伝導ループと、複数層の超伝導配線層(M8〜M11)と、第1の抵抗層(RES1)とを有している。第1の超伝導グランド層(M7)下に、複数の超伝導配線層(M2、M4、M6)と、複数の超伝導グランド層(M1、M3、M5)と、第2の抵抗層(RES2)とを有している。

(もっと読む)

超伝導ランダムアクセスメモリの構成方法

【課題】 大規模なRAMの構成においても超高速で且つ超低消費電力を実現可能とする。

【解決手段】 超伝導RAMの構成は、メモリセルアレイにアクセスするワード線、ビット線等の駆動線及びセンス線のそれぞれを複数のブロックに分割し、そのブロック内の信号伝搬にはそれぞれ負荷駆動能力の高いレベル論理のドライバ回路及びセンス回路を有するブロック内信号伝搬回路(DR)3を用いており、更に、長距離のブロック間の信号伝搬には高速動作が可能な単一磁束量子(SFQ)素子で構成された超伝導パッシブトランスミッションライン(PTL)2を使用している。その結果、全体としての高速動作を可能にする。これにスプリッタ(S)又はコンフルエンスバッファ(C)、及びラッチ回路(DL)を追加して用いることができ、更にバイナリーツリー構成を採用してもよい。

(もっと読む)

情報処理用の結合方法およびアーキテクチャ

(i)第一の情報素子、(ii)第二の情報素子、(iii)第一の結合要素および(iv)第二の結合要素を含む構造を提供する。第一の情報素子は少なくとも、互いに電気的に導通する第一のローブおよび第二のローブを有している。第二の情報素子は少なくとも、互いに電気的に導通する第一のローブおよび第二のローブを有している。第一の結合要素は、第一の情報素子の第一のローブを第二の情報素子の第一のローブに誘導結合する。第二の結合要素は、第一の情報素子の第一のローブを第二の情報素子の第二のローブに誘導結合する。  (もっと読む)

(もっと読む)

同調可能なインダクタンス特性を有する薄層型超伝導体部品、同超伝導体部品の製造方法及び同超伝導体部品を含んだデバイス

【課題】 特に、同調可能な又は調整可能な特性を有する薄層型超伝導体,その超伝導体の製造方法及びそのような部品を有するデバイスを提供することを課題とする。

【解決手段】 その部品は、交互に積層された電気的絶縁材料の薄層と超伝導材料の薄層とにより成るスタックと、超伝導層の少なくとも二つの間に抵抗接続を構成するための同調手段とを有している。この部品のインダクタンスは、その接続の抵抗を修正することにより調整することができる。

(もっと読む)

1 - 10 / 10

[ Back to top ]