Fターム[4M119FF14]の内容

MRAM・スピンメモリ技術 (17,699) | コンタクト (2,004) | コンタクトの場所 (1,215) | 記憶素子と下部配線間 (78)

Fターム[4M119FF14]に分類される特許

1 - 20 / 78

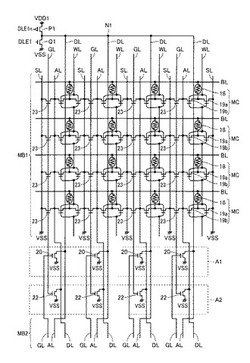

半導体記憶装置

【課題】半導体基板の表面の空き領域が少ない半導体記憶装置を提供する。

【解決手段】このMRAMの各メモリセルMCは、磁気抵抗素子18と2つのアクセストランジスタ19a,19bを含み、トランジスタ19a,19bのドレインを磁気抵抗素子18を介して対応のビット線BLに接続し、それらのゲートを対応のワード線WLに接続し、それらのソースをそれぞれソース線SLおよび補助配線ALに接続する。したがって、アクセストランジスタ19bのソースとDLドライバ14に含まれるドライバトランジスタ23のソースとを共通化することができ、シリコン基板31の表面の空き領域を減らすことができる。

(もっと読む)

半導体装置

【課題】隣接するビット線同士の短絡が抑制されており、かつ層間絶縁膜が平坦に研磨された半導体装置を提供する。

【解決手段】磁気抵抗素子MRDが複数配置されたメモリセル領域と、平面視においてメモリセル領域の周囲に配置された周辺回路領域とを備える。磁気抵抗素子MRDは、磁化固定層と磁化自由層とトンネル絶縁層とを含んでいる。磁気抵抗素子MRDの上方には、主表面に沿った方向に向けて延びる複数の第1の配線BLを有している。上記周辺回路領域には、第1の配線BLと同一レイヤにより構成される第2の配線BL2と平面視において重なるように、磁化自由層と同一材質の層、トンネル絶縁層と同一材質の層および磁化固定層と同一材質の層が積層された積層構造DMMが配置されている。積層構造DMMは、周辺回路領域にて平面視において隣接する1対の第2の配線BL2の両方と重ならない。

(もっと読む)

磁気抵抗効果素子及びその製造方法

【課題】信頼性の高い磁気抵抗効果素子の構造並びにそのような構造を安定して得ることのできる磁気抵抗効果素子の製造方法を提供する。

【解決手段】基板上に、第1の電極層と、金属材料により形成された金属層と、第1の磁性層と、トンネル絶縁膜と、第2の磁性層と、第2の電極層とを形成し、第2の電極層をパターニングし、第2の磁性層、トンネル絶縁膜、第1の磁性層及び金属膜をパターニングするとともに、パターニングした第2の磁性層、トンネル絶縁膜、第1の磁性層及び金属膜の側壁部分に、金属膜のリスパッタ粒子を堆積して側壁金属層を形成し、側壁金属層を酸化して絶縁性の側壁金属酸化物層を形成する。

(もっと読む)

縦型トランジスタSTRAMアレイ

【課題】複数の不揮発性可変抵抗メモリセルを含む縦型のメモリアレイを提供する。

【解決手段】方法は、半導体ウェハから垂直に伸延する複数のピラー構造を有する半導体ウェハを提供するステップを含む。導電相互接続素子が、少なくとも選択された縦型ピラートランジスタ上に堆積されるとともに、不揮発性可変抵抗メモリセルが、導電相互接続素子上に堆積されて、縦型トランジスタメモリアレイを形成する。

(もっと読む)

磁気ランダムアクセスメモリ及びその製造方法

【課題】 セルの微細化を図る。

【解決手段】 実施形態による磁気ランダムアクセスメモリは、半導体基板1上に形成された選択素子Trと、選択素子上に形成された多層配線層7a−cと、多層配線層上に形成された層間絶縁膜8と、層間絶縁膜内に形成され、多層配線層を介して選択素子と電気的に接続されたコンタクト層9と、コンタクト層と電気的に接続され、金属材で形成された下部電極層21と、下部電極層の側面を取り囲み、金属材の酸化物で形成された金属酸化絶縁膜26と、下部電極層上に形成された磁気抵抗素子10と、磁気抵抗素子上に形成された上部電極層23と、磁気抵抗素子及び上部電極層の側面上に形成された側壁絶縁膜25と、上部電極層と電気的に接続されたビット線29と、を具備する。

(もっと読む)

半導体装置、および、半導体装置の製造方法

【課題】磁壁移動型の磁気抵抗素子の微細化を実現する。

【解決手段】基板上に位置する第1の絶縁層24と、第1の絶縁層の24内部に位置し、互いに電気的に絶縁した一対の第1の磁化固定層20a、20bと、第1の絶縁層24上に位置し、平面視で一対の第1の磁化固定層20a、20bいずれとも重なり、かつ、一対の第1の磁化固定層20a、20bいずれとも電気的に接続している磁化自由層31と、磁化自由層31上に位置する第2の絶縁層33と、第2の絶縁層33に形成され、平面視で磁化自由層31と重なる孔と、当該孔の底面および側面に沿って形成された非磁性層41と、非磁性層41形成後の孔内に埋め込まれた第2の磁化固定層42と、を有し、第2の磁化固定層42は、平面視で一対の第1の磁化固定層20a、20bいずれとも重ならず、かつ、平面視で一対の第1の磁化固定層20a、20bの間に位置する半導体装置。

(もっと読む)

抵抗変化型半導体メモリ

【課題】セル面積の縮小及び動作特性の向上に優れたレイアウトを提案する。

【解決手段】実施形態によれば、抵抗変化型半導体メモリは、第1方向に並ぶ第1乃至第4メモリセルを備える。第1乃至第4メモリセルの各々は、第1ソース/ドレインが第1方向に延びる第1ビット線BLA1に接続され、ゲートが第2方向に延びるワード線WL1, WL2, WL3, WL4に接続されるセルトランジスタT11, T12, T13, T14と、一端がセルトランジスタT11, T12, T13, T14の第2ソース/ドレインに接続され、他端が第2方向に延びる第2ビット線BLB1, BLB2, BLB3, BLB4に接続される抵抗性記憶素子M11, M12, M13, M14とを有する。第1及び第2メモリセル内の第1ソース/ドレインは、共有化され、第3及び第4メモリセル内の第1ソース/ドレインは、共有化される。

(もっと読む)

半導体記憶装置

【課題】 セルアレイ面積を増大させることなく、書き込みディスターブを抑制可能な半導体記憶装置を提供する。

【解決手段】

二端子型の記憶素子Rと選択用のトランジスタQを直列に接続してなるメモリセルを複数、マトリクス状に配列させたメモリセルアレイ100と、書き換え電圧パルスを第1ビット線に印加する第1電圧印加回路101と、プリチャージ電圧を第1及び第2ビット線に印加する第2電圧印加回路102を有する半導体記憶装置であって、メモリセルの書き換え時において、予め第2電圧印加回路102がメモリセルの両端を同一電圧にプリチャージした後、第1電圧印加回路101が選択用のトランジスタに直接接続する第1ビット線を介して書き換え電圧パルスを印加するとともに、第2電圧印加回路102が記憶素子と直接接続する第2ビット線に当該プリチャージ電圧を印加する。

(もっと読む)

半導体装置および半導体装置アセンブリ

【課題】外部からの磁場を遮蔽する磁気シールド効果が高い半導体装置を提供する。

【解決手段】半導体基板SUBの主表面上に形成されたスイッチング素子TRを覆うように形成された層間絶縁膜III1と、平板状の引出配線LELと、引出配線LELとスイッチング素子TRとを接続する接続配線ICLと、磁化の向きが可変とされた磁化自由層MFLを含み、引出配線LEL上に形成された磁気抵抗素子TMRとを備える。磁化自由層MFLの磁化状態を変化させることが可能な配線DLと配線BLとを備えている。磁気抵抗素子TMRが複数並んだメモリセル領域において、磁気抵抗素子TMRの上部に配置された第1の高透磁率膜CLAD2が、上記メモリセル領域から、メモリセル領域以外の領域である周辺領域にまで延在している。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】絶縁膜の比誘電率を容易かつ十分に低下させる。

【解決手段】半導体装置の製造方法では、それぞれ環状SiO構造を主骨格とし互いに構造が異なる2種類以上の有機シロキサン化合物原料を混合した後で気化する。又は、それら2種類以上の有機シロキサン化合物原料の混合と気化とを一度に行うことによって、気化ガスを生成する。そして、その気化ガスをキャリアガスとともに反応炉に輸送する。そして、反応炉にてその気化ガスを用いたプラズマCVD法又はプラズマ重合法によって多孔質絶縁膜を成膜する。

(もっと読む)

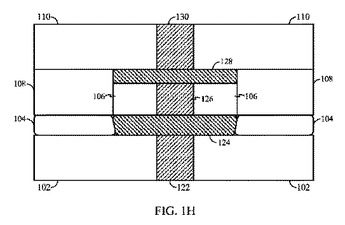

平坦化された電極上の磁気トンネル接合(MTJ)

直接接触を用いた磁気トンネル接合(MTJ)は、より低い抵抗、改善された生産量、及び、より単純な製造を有して製造される。より低い抵抗は、MTJの読み取り方法及び書き込み方法の両方を改善する。MTJ層(126)は、下部電極(124)上に堆積され、下部金属(122)に位置合わせされる。エッチング停止層(302)は、下部金属を囲う絶縁体のオーバーエッチングを防止するために下部金属に隣接して堆積され得る。下部電極は、実質的に平坦な表面を提供するためにMTJ層の堆積前に平坦化される。さらに、下層(202)は、MTJの所望の特性を促進するためにMTJ層の前に下部電極上に堆積され得る。  (もっと読む)

(もっと読む)

磁気ランダムアクセスメモリを製造するシステムおよび方法

磁気ランダムアクセスメモリを製造するシステムおよび方法が開示される。特定の一実施形態では、磁気トンネル接合メモリシステムを作製する方法は、金属層の一部分を、ほぼ直線の部分を有する無分岐のソースラインの中に形成するステップを含む。この方法はまた、ソースラインをほぼ直線の部分で、第1のビアを使用して第1のトランジスタに結合するステップを含む。第1のトランジスタは、ソースラインから受け取った第1の電流を第1の磁気トンネル接合デバイスに供給するように構成される。この方法は、ソースラインを、第2のビアを使用して第2のトランジスタに結合するステップを含み、第2のトランジスタは、ソースラインから受け取った第2の電流を第2の磁気トンネル接合デバイスに供給するように構成される。  (もっと読む)

(もっと読む)

電子装置およびその製造方法

【課題】コンタクトホールを、タングステンにより、前記構造の還元を抑制しながら充填する電子装置の製造方法の提供。

【解決手段】上部電極12Cを露出するコンタクトホール14Aを形成する工程と、コンタクトホールの底面および側壁面を導電性バリア膜15で覆う工程と、シランガスを第1のキャリアガスとともに供給し、導電性バリア膜をシランガスに曝露する初期化工程と、タングステンの原料ガスをシランガスおよび第2のキャリアガスとともに供給し、コンタクトホールの底面および側壁面にタングステン膜を堆積させる工程と、タングステンの原料ガスを水素ガスとともに供給し、タングステン膜上にさらにタングステン膜を堆積し、前記コンタクトホールを少なくとも部分的に充填するタングステン充填工程とを含み、第1および第2のキャリアガスの各々は不活性ガスよりなり、水素ガスを含まないか、水素ガスをシランガス流量の二倍以下の流量で含む。

(もっと読む)

半導体装置およびその製造方法

【課題】製造プロセス中に磁性体膜の材料の拡散を防止しながら、高い磁気シールド効果を有するヘテロ構造磁気シールドを備えた半導体装置を提供する。

【解決手段】半導体装置10は、半導体基板20、半導体基板20の主面上に形成され、かつ多層配線層11Bを含む半導体素子12、および半導体素子12を被覆するヘテロ構造磁気シールド170を含む。ヘテロ構造磁気シールド170は、第一の磁気シールド積層構造16Aと磁気シールド積層構造16Aを覆う第二の磁気シールド積層構造16Bを含む。第一および第二の磁気シールド積層構造16Aおよび16Bは、いずれも、半導体素子12を被覆する磁性体からなる磁気シールド膜および半導体素子12と磁気シールド膜との間に介在し磁性体の拡散を防止するバッファ膜とを有する。

(もっと読む)

磁気記憶装置

【課題】MRAMの情報の記録動作時における安定動作と、記録情報の安定保持とを可能にした磁気記憶装置を提供する。

【解決手段】ダイ110は、基板と、第1および第2配線と、磁気記憶素子と、第1の磁気シールド構造とを有する。第1の磁気シールド構造は、平面視において磁気記憶素子を覆うように形成されている。第2および第3の磁気シールド構造113、114は、厚み方向においてダイ110を挟んでいる。リードフレーム部材112は、ダイ110が実装され、かつ強磁性体を含有する。リードフレーム部材112は平面視においてダイ110の一部のみと重複している。

(もっと読む)

磁気記憶装置およびその製造方法

【課題】磁気記憶素子の機能低下を抑制することのできる磁気記憶装置およびその製造方法を提供する。

【解決手段】磁気記憶装置は、磁化状態に基づいたデータを保持可能な磁気記憶素子MMと、発生する磁界により磁気記憶素子の磁化状態を変化させることが可能なディジット線DLおよびビット線BLとを備えている。磁気記憶素子MMは、ディジット線DLとビット線BLとの交差部分において、ディジット線DLの上であってビット線BLの下に配置されている。ディジット線DLはこの交差部分において幅WDLを有しており、かつビット線BLはこの交差部分において幅WBLを有している。幅WDLは磁気記憶素子MMの幅WMM1よりも大きく、かつ幅WBLは磁気記憶素子MMの幅WMM2よりも小さい。

(もっと読む)

半導体記憶装置

【課題】最適な書き込み電流を磁気抵抗素子に供給する。

【解決手段】半導体記憶装置は、半導体基板11に設けられた選択トランジスタ13と、半導体基板11の上方に設けられ、かつ第1の方向に延在する第1の配線層BLと、磁化の方向が固定された固定層22Aと、固定層22A上に設けられた非磁性層22Bと、非磁性層22B上に設けられかつ磁化の方向が可変である記録層22Cとを有し、かつ第1の配線層BLの上方に設けられ磁気抵抗素子22と、第1の方向に延在し、かつ選択トランジスタ13の拡散領域17に電気的に接続された第2の配線層bBLとを含む。固定層22Aは第1の配線層BLに電気的に接続され、記録層22Cは選択トランジスタ13の拡散領域16に電気的に接続される。

(もっと読む)

不揮発性磁気メモリ装置

【課題】垂直磁化型の記録層における磁化容易軸をより確実に垂直方向に向かせ得る構成、構造を有する不揮発性磁気メモリ装置を提供する。

【解決手段】不揮発性磁気メモリ装置は、(A)磁化容易軸が垂直方向を向いている記録層53を有する積層構造体50、(B)積層構造体50の下部に電気的に接続された第1の配線41、並びに、(C)積層構造体50の上部に電気的に接続された第2の配線42から成る磁気抵抗効果素子を備えており、積層構造体50の側面に近接して、記録層53を構成する材料のヤング率よりも高い値のヤング率を有する高ヤング率領域171が配置されている。

(もっと読む)

磁性記憶素子を用いた半導体集積回路装置の製造方法

【課題】トンネル磁気抵抗効果膜を積層した積層体の加工をイオンミリング等で行なう場合、トンネル磁気抵抗効果膜を構成する材料の飛散物が、当該積層体の側壁等に付着したり、当該加工を行なう装置内を汚染する。従って、磁性記憶素子或いはこうした磁性記憶素子を搭載した半導体装置を安定的な特性で製造することが困難であった。

【解決手段】トンネル磁気抵抗効果膜の上部に配置した導体層の側壁に側壁スペーサを形成し、且つ側壁スペーサに、加工中のトンネル磁気抵抗効果膜を構成する材料の飛散物を付着させた後に、側壁スペーサを除去することで前記材料の付着物をも除去する。一種類の側壁スペーサを用いる方法と、2種類の側壁スペーサを用いる方法がしめされる。

(もっと読む)

半導体装置およびその製造方法

【課題】MRAMデバイスを含む半導体装置において、外部磁界に対する耐性を向上させることにより、MRAMデバイスのデータ保持特性の向上を図ることができる技術を提供する。

【解決手段】ダイパッドDP上にダイアタッチフィルムDAF1を介して磁気シールド材PM1を配置する。そして、この磁気シールド材PM1上にダイアタッチフィルムDAF2を介して半導体チップCHPを搭載する。さらに、半導体チップCHP上にダイアタッチフィルムDAF3を介して磁気シールド材PM2を配置する。つまり、半導体チップCHPは、磁気シールド材PM1と磁気シールド材PM2で挟まれるように配置する。このとき、磁気シールド材PM2の平面的な面積は、磁気シールド材PM1の平面的な面積よりも小さくなっているが、磁気シールド材PM2の厚さは、磁気シールド材PM1の厚さよりも厚くなっている。

(もっと読む)

1 - 20 / 78

[ Back to top ]