Fターム[4M119FF16]の内容

MRAM・スピンメモリ技術 (17,699) | コンタクト (2,004) | コンタクトの場所 (1,215) | 記憶素子と選択素子間(下部配線無) (226)

Fターム[4M119FF16]に分類される特許

121 - 140 / 226

半導体素子のパターン構造物形成方法

【課題】磁性物質又は相変化物質を含む半導体素子のパターン構造物の形成方法を提供する。

【解決手段】基板上に、磁性物質又は少なくとも3つの元素を含む合金からなった相変化物質のいずれか一つの物質を含むエッチング対象膜を形成する段階と、少なくともアンモニア(NH3)ガスを含むエッチングガスを使って前記エッチング対象膜をプラズマ反応性エッチングすることによってパターン構造物を形成する段階とを有する。

(もっと読む)

半導体装置

【課題】 スピン注入磁化反転を用いたメモリセルの読み出しディスターブを防ぎ、大電流で高速に読み出す。

【解決手段】 複数のワード線WLと、複数のビット線BLと、複数のメモリセルMCと、選択されたメモリセルから情報を読み出す読み出し回路SA,LAと、読み出し回路SA,LAが読み出した情報に基づいて、選択されたメモリセルに書き換えを行う書き換え回路WD1,WD2とを有し、読み出し回路SA,LAが選択されたメモリセルから情報を読み出す期間は、書き換え回路WD1,WD2が読み出し回路SA,LAが読み出した情報に基づいて選択されたメモリセルに情報を書き込む期間より短い。

(もっと読む)

磁気記憶装置

【課題】大容量化が可能な磁気記憶装置を提供する。

【解決手段】第1方向に形成されたアクティブエリア11と、アクティブエリア11上に形成され、抵抗値の変化によってデータを記憶するMTJ素子12と、MTJ素子12の両側のアクティブエリア11上に、第1方向と直交する第2方向に形成されたセルトランジスタT1,T2のゲート電極(ワード線WL)とを備える。さらに、ゲート電極のMTJ素子12と反対側のアクティブエリア11上に形成されたビット線コンタクト13と、MTJ素子12に接続され、第1方向に形成されたビット線BLと、ビット線コンタクト13に接続され、第1方向に形成されたビット線bBLとを備える。MTJ素子12とビット線コンタクト13がゲート電極を間に挟んで交互に配置されている。

(もっと読む)

不揮発性メモリの記録方法及び不揮発性メモリ

【課題】抵抗変化を情報として記録を行う不揮発性メモリにおいて、記録による情報記憶素子の破壊や寿命の短縮を抑えて長寿命で信頼性の高い記録を実現する。

【解決手段】抵抗変化を有する情報記憶素子に対して電気的に情報の記録を行う記録回路を含む不揮発性メモリの記録方法であって、上記記録回路は、情報記憶素子に対して当該記録回路の出力インピーダンスが情報記憶素子の低抵抗状態の抵抗値よりも大きい状態で低抵抗状態の情報を記録する。また、上記記録回路は、情報記憶素子に対して当該記録回路の出力インピーダンスが情報記憶素子の高抵抗状態の抵抗値よりも小さい状態で高抵抗状態の情報を記録する。

(もっと読む)

メモリ及び書き込み制御方法

【課題】少ない書き込み電圧から成る書き込み電流を印加することによって記憶層の磁化の向きを反転させることで、記憶素子の破壊を防ぎつつ、記憶素子に情報を記憶させる。

【解決手段】SpRAM1は、磁性体の磁化状態により情報を記憶する記憶層と、記憶層に対して非磁性層を介して、磁化の向きが固定された磁化固定層と、を有し、記憶層及び磁化固定層の積層方向に流す書き込み電流を印加することによって、記憶層の磁化の向きが変化して、記憶層に情報が記憶される記憶素子2を備える。また、独立した2つ以上のパルス列から成る書き込み電圧で、記憶素子2に書き込み電流を供給する電圧制御部11を備える。

(もっと読む)

メモリ

【課題】同じ構成の記憶素子を用いて、ROMとRAMとを共に実現することができるメモリを提供する。

【解決手段】磁化M1の向きが反転可能な磁化自由層18と、絶縁体からなるトンネルバリア層17と、磁化自由層18に対してトンネルバリア層17を介して配置され、磁化M14,M16の向きが固定された磁化固定層13とを含む、トンネル磁気抵抗効果素子から構成された記憶素子1を複数個含み、記憶素子1の磁化自由層18の磁化M1の向きによって情報が記録される、ランダムアクセスメモリ領域と、記憶素子1のトンネルバリア層17の絶縁破壊の有無によって情報が記録される、リードオンリーメモリ領域とを含むメモリを構成する。

(もっと読む)

メモリ及び情報処理方法

【課題】不良が発生した記憶素子から情報を読み出す場合に、書き込まれるべき情報を正しく読み出すこと。

【解決手段】SpRAM1は、1ビットの情報を記憶する記憶素子2と、記憶素子2に書き込まれた情報を読み出すセンスアンプ10を備える。センスアンプ10は、所定の単位数の記憶素子2を有する記憶ブロックの内、特定の1個の記憶素子2を反転フラッグ素子として定める。そして、センスアンプ10は、反転フラッグ素子に書き込まれた1ビットの情報が、“0”又は“1”の内、いずれかを示す第1の値である場合に、他の記憶素子2に書き込まれた所定の単位数−1ビットの情報をビット反転して読み出す。一方、反転フラッグ素子に書き込まれた1ビットの情報が、第1の値とは異なる第2の値である場合に、他の記憶素子2に書き込まれた所定の単位数−1ビットの情報をそのまま読み出す。

(もっと読む)

記憶素子及びメモリ

【課題】大きな磁気抵抗変化率を確保しつつ、スピン注入時の電流を抑制し、かつ、絶縁破壊電圧を向上させることが可能な記憶素子を提供する。

【解決手段】記憶層17と、この記憶層17を挟むように設けられた、絶縁層(第1の中間層)16及び絶縁層(第2の中間層)19と、第1の中間層16の記憶層17とは反対側に配置された第1の磁化固定層31と、第2の中間層19の記憶層17とは反対側に配置された第2の磁化固定層32と、第2の中間層19と記憶層17との間に設けられた非磁性導体層18とを含み、積層方向にスピン偏極した電子を注入することにより、記憶層17の磁化M1の向きが変化して、記憶層17に対して情報の記録が行われる記憶素子3を構成する。

(もっと読む)

スピントルクの切換を補助する層を有する、スピントルクの切換を持つ磁気積層体

磁気メモリセルは強磁性の自由層と強磁性のピン留めされた参照層とを有し、自由層と参照層との各々は平面外磁気異方性と平面外磁気配向とを有し、スピントルクによって切換え可能である。セルは、自由層に近接する強磁性のアシスト層を含み、アシスト層は約500Oe未満の磁気異方性を有する。アシスト層は、平面内または平面外の異方性を有し得る。  (もっと読む)

(もっと読む)

抵抗変化型メモリ

【課題】製造コストの低減及び動作特性の向上が可能な抵抗変化型メモリを提供する。

【解決手段】本発明の例に関わる抵抗変化型メモリは、第1の方向に延在するビット線BL1と、第2の方向に延在するビット線bBL1,bBL2と、ワード線WL1,WL2と、制御端子がワード線WL1に接続され、電流経路の一端が第2のビット線bBL1に接続される選択トランジスタST1と、制御端子がワード線WL2に接続され、電流経路の一端がビット線bBL2に接続され、電流経路の他端が選択トランジスタST1の他端と共有ノードN1をなす選択トランジスタST2と、一端がビット線BL1に接続され、他端が共有ノードN1に接続される抵抗変化型記憶素子10と、を備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】可変抵抗素子の特性バラツキを低減することで、動作マージンを大きくすることが可能な半導体記憶装置及びその製造方法を提供する。

【解決手段】半導体記憶装置は、メモリ領域に配置され、かつ抵抗値の変化に応じてデータを記憶し、かつ第1の配線SLに一端が電気的に接続され、第2の配線に他端が電気的に接続された複数の可変抵抗素子23と、メモリ領域に配置され、かつ可変抵抗素子23と同じ材料からなり、かつ電気的に絶縁された複数のダミー素子28とを含む。MTJ素子23及びダミー素子28を合わせた素子アレイは、格子状の密集パターンを有している。すなわち、MTJ積層膜を加工する際のレジストパターンを格子状の密集パターンによって形成する。そして、このレジストパターンを用いてMTJ積層膜を加工することで、MTJ素子23とダミー素子28とを合わせた素子アレイを格子状の密集パターンに配置する。

(もっと読む)

抵抗変化型メモリ装置

【課題】 小型のセルを有し、大きな双方向電流を供給可能な抵抗変化型メモリ装置を提供する。

【解決手段】 抵抗変化型メモリ装置は、第1ノードと接続ノードとの間に並列接続された2つのトランジスタと、一端を接続ノードと接続され且つ抵抗値が異なる少なくとも2つの状態を有する抵抗変化素子と、を各々が具備し、第1軸および第2軸からなる行列状に配置された複数のメモリセルMCと、複数のビット線BLと、を含んでいる。各メモリセルの第1ノードと、このメモリセルの抵抗変化素子の他端である第2ノードとは別々のビット線と接続される。メモリセルの1つである第1メモリセルの第1ノードと、第1メモリセルと第2軸に沿った第1方向側で隣接するメモリセルの第1ノードとは、同じビット線と接続される。第1メモリセルの第2ノードと、第1メモリセルと第2軸に沿った第2方向側で隣接するメモリセルの第2ノードとは、同じビット線と接続される。

(もっと読む)

磁気ランダムアクセスメモリ

【課題】スピン注入型の磁気ランダムアクセスメモリに関し、より小さいサイズのメモリセル選択トランジスタで効率的な書き込みが可能な磁気ランダムアクセスメモリを提供する。

【解決手段】ビット線24、接続導体層25及びMTJ素子30が形成された層間絶縁膜22上には、層間絶縁膜26が形成されている。層間絶縁膜26には、接続導体層25に接続されたプラグ27と、MTJ素子30に接続されたプラグ28とが埋め込まれている。層間絶縁膜26上には、プラグ27とプラグ28とを電気的に接続する局所内部配線29が形成されている。これにより、MTJ素子30のフリー層側は、プラグ28、局所内部配線29、プラグ27、接続導体層25、プラグ23、接続導体層21、及びプラグ19を介して、n型ドレイン領域16に電気的に接続されている。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】磁気抵抗変化素子を備えたメモリセルに記憶された2値の情報を適切に読み出すことができる半導体記憶装置等を提供する。

【解決手段】記憶用磁気抵抗変化素子を備えた複数のメモリセルを含むメモリセルアレイ51と、参照用磁気抵抗変化素子を備えた複数の参照セルを含み、参照電流を出力する参照セルアレイ53と、前記参照電流から求められる参照抵抗値と前記記憶用磁気抵抗変化素子の抵抗値とを比較して当該メモリセルに記憶されている情報を判定する判定手段56と、が設けられている。更に、前記参照セルアレイが前記参照電流を出力する際に、前記複数の参照用磁気抵抗変化素子から選択される高抵抗状態の参照用磁気抵抗変化素子及び低抵抗状態の参照用磁気抵抗変化素子を特定する情報並びにこれらの接続関係を示す制御情報を記憶する記憶手段55と、前記制御情報に基づいて前記参照セルアレイの動作を制御する制御手段54と、が設けられている。

(もっと読む)

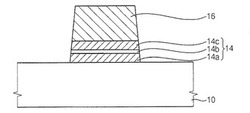

磁気抵抗効果素子および磁気記憶装置

【課題】低コストでホイスラー合金の規則化を促進させ、高い磁気抵抗効果を実現すること。

【解決手段】下地層11に自由磁化層12、非磁性層13、固定磁化層14、反強磁性層15および保護層16を積層した積層構造を有する磁気抵抗効果素子1において、自由磁化層12を固定磁化層14のうち少なくともいずれか1層をホイスラー合金で形成し、下地層、非磁性層13、保護層16のうち少なくとも1層をB2規則化構造の合金層で形成する。

(もっと読む)

垂直異方性を有するST−RAMセル

磁気トンネル接合セルとも称される、磁気スピントルクメモリセルは、関連した強磁性層についての、ウェハ平面に垂直に揃えられた、または「面外」の磁気異方性(すなわち、ゼロ磁場およびゼロ電流における磁化方向)を有する。メモリまたは磁気接合セルは、強磁性自由層と、第1の固定基準層と、第2の固定基準層を有し、各々は、基板に対して垂直な磁気異方性を有する。自由層は、スピントルクによって、第1の方向から反対の第2の方向へ切換可能な、基板に垂直な磁化方向を有する。  (もっと読む)

(もっと読む)

磁気メモリ装置

【課題】磁気メモリ装置のメモリセルを縮小化する。

【解決手段】MTJ素子と選択トランジスタとが直列接続された1T1MTJメモリセルでは、MTJ素子に流す電流の向きによって選択トランジスタの電流駆動能力が異なることに鑑み、電流駆動能力の低い方でMTJ素子に流される書き込み電流が、電流駆動能力の高い方でMTJ素子に流される書き込み電流より小さくなるように、MTJ素子の特性を調整することで、より小さなサイズの選択トランジスタが使用できるようにする。

(もっと読む)

半導体記憶装置

【課題】高速動作が可能なロジック回路とMRAMを備えた半導体記憶装置を提供する。

【解決手段】第1MOS型トランジスタのソース領域またはドレイン領域上の層間絶縁膜15A内にはコンタクトプラグ16Aが形成されている。ソース領域またはドレイン領域上の層間絶縁膜15A内にはコンタクトプラグ16Bが形成されている。コンタクトプラグ16A上には第1配線層M1Aが形成されている。磁気抵抗効果素子19は、コンタクトプラグ16B上の、第1配線層M1Aと半導体基板面から同じ高さの層に配置されている。第2MOS型トランジスタのソース領域またはドレイン領域上の層間絶縁膜15A内にはコンタクトプラグ16Cが形成されている。そして、第1配線層M1Bは、コンタクトプラグ16C上の、第1配線層M1A及び磁気抵抗効果素子19と半導体基板面から同じ高さの層に配置されている。

(もっと読む)

ダマシンタイププロセスで形成されたトンネル障壁とピンド層と頂部電極とを備えた磁気トンネル接合

スピン移動トルク磁気抵抗ランダムアクセスメモリ(STT‐MRAM)ビットセル用の磁気トンネル接合記憶素子は、底部電極層(150)と、底部電極層に隣接するピンド層(160)と、底部電極層及びピンド層の一部分を封入する誘電体層(70)であって、ピンド層の一部分に隣接するホールを画定する側壁を含む誘電体層と、ピンド層に隣接するトンネリング障壁(190)と、トンネリング障壁に隣接する自由層(200)と、自由層に隣接する頂部電極(210)とを含む。第一の方向における底部電極層及び/又はピンド層の幅は、第一の方向におけるピンド層とトンネリング障壁との間のコンタクト領域の幅よりも大きい。また、STT‐MRAMビットセルの製造方法も開示される。  (もっと読む)

(もっと読む)

フローティングボディー効果を利用した磁気抵抗メモリセル、これを含むメモリ素子及びその動作方法

【課題】高集積の磁気抵抗メモリ素子に必要な選択トランジスタの電流駆動能力をフローティングボディー効果によって向上させた磁気抵抗メモリセル、これを含む磁気抵抗メモリ素子及びその動作方法を提供する。

【解決手段】磁気抵抗メモリセルは、磁気トンネル接合素子及び選択トランジスタを含む磁気抵抗メモリセルであり、選択トランジスタは、第1導電型の半導体層101;半導体層101上にゲート絶縁膜22を介して形成されたゲート電極20;半導体層101内に相互離隔して形成され、第2導電型を持つ第1及び第2拡散領域40;を含む。ここで、第1及び第2拡散領域40の間の半導体層101の一部が電気的にフローティングされたボディー領域103に形成される。本発明によれば、フローティングボディー効果を利用した高性能の選択トランジスタを適用することで、磁気抵抗メモリ素子の高集積化を達成することができる。

(もっと読む)

121 - 140 / 226

[ Back to top ]