Fターム[4M119FF16]の内容

MRAM・スピンメモリ技術 (17,699) | コンタクト (2,004) | コンタクトの場所 (1,215) | 記憶素子と選択素子間(下部配線無) (226)

Fターム[4M119FF16]に分類される特許

101 - 120 / 226

磁気ランダムアクセスメモリ及びその製造方法

【課題】 書き込み電流の低減を図る。

【解決手段】 実施形態による磁気ランダムアクセスメモリは、メモリセルに磁気抵抗素子100を備えた磁気ランダムアクセスメモリであって、磁気抵抗素子100は、第1の金属磁性層24と、第2の金属磁性層26と、第1及び第2の金属磁性層24、26に挟まれた絶縁層25と、を具備し、第1及び第2の金属磁性層24、26の各面積は、絶縁層25の面積より小さい。

(もっと読む)

記憶素子、記憶素子の製造方法、及び、メモリ

【課題】消費電力化が可能な記憶素子を提供する。

【解決手段】積層方向に電流を流して、スピン偏極した電子を注入することにより、記憶層16の磁化M1の向きが変化して、記憶層16に対して情報の記憶が行われる記憶素子3を構成する。この記憶素子3は、情報を磁性体の磁化状態により保持する記憶層16と、記憶層16に対してトンネルバリア層15を介して設けられている磁化固定層14とを備える。そして、トンネルバリア層15は、厚さが0.1nm以上0.6nm以下であり、且つ、界面ラフネスが0.5nm未満である。

(もっと読む)

磁気記憶素子及び磁気メモリ

【課題】情報保持特性を低下することなくスピン注入による磁化反転を起こすために必要な電流を低減化する。

【解決手段】磁化方向が所定の方向に固定された参照層26と、スピン注入により磁化方向が変化する記録層28と、記録層28と参照層26を隔てる中間層27と、記録層28を加熱する発熱部33と、を備える。記録層28の材料は、磁化量が150℃で室温時の磁化量の50%以上となり、150℃以上200℃以下の範囲で室温時の磁化量の10%以上80%以下となる磁性体より構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体集積回路の高集積化と機能素子の高性能化とを同時に実現する。

【解決手段】実施形態に係わる半導体装置は、半導体基板1の表面領域に配置されるスイッチ素子3,4と、下面がスイッチ素子3,4に接続されるコンタクトプラグ6と、コンタクトプラグ6の上面の直上に配置される機能素子7とを備える。コンタクトプラグ6の上面の最大表面粗さは、0.2nm以下である。

(もっと読む)

磁気トンネル接合素子を用いた磁気ランダムアクセスメモリおよびその製造方法

【課題】磁気トンネル接合素子を用いた磁気ランダムアクセスメモリ(MRAM)において、磁気トンネル接合素子形成プロセスで、磁気トンネル接合素子の側壁に導電性膜などが形成されてしまうと、トンネルバリア層から素子側壁導電性膜へ、電流リークが発生する。電流リークを防止し、信頼性の高い磁気トンネル接合素子を用いたMRAMおよびその製造方法を提供することを目的とする。

【解決手段】

素子側壁導電性膜であるTaO層60の上面60Uよりも、トンネルバリア層42の下面42Lの位置のほうが高く形成できるように、バッファ層30上に磁気トンネル接合素子を形成する。そのために、バッファ層30の膜厚と、トンネルバリア層下面位置42Lと、磁気トンネル接合素子周辺に形成されたTaO層60の上面60Uと、の関係をあらかじめ求めておき、当該関係に基づき、バッファ層30の成膜膜厚を決定する。

(もっと読む)

磁気記憶装置の製造方法及び磁気記憶装置

【課題】 MTJ素子が配置される凹部の平面寸法は微細であるため、下層構造との位置合わせが困難である。

【解決手段】 基板の上に下部導電膜を形成する。下部導電膜の上に第1の絶縁膜を形成する。第1の絶縁膜に、下部導電膜まで達する開口を形成する。開口内の下部導電膜の上、及び第1の絶縁膜の上に、磁化自由層とトンネル絶縁膜と磁化固定層とを有するMTJ積層膜を堆積させる。MTJ積層膜の上に上部電極を形成する。第1の絶縁膜の上に堆積しているMTJ積層膜を除去することにより、開口内に残ったMTJ積層膜からなるMTJ素子を形成する。第1の絶縁膜の少なくとも一部、及び下部導電膜の一部を除去することにより、MTJ素子の下に下部導電膜からなる下部電極を形成する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】記憶素子の下にあるコンタクトプラグの上面の平坦性を改善し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、半導体基板上に設けられた複数のスイッチングトランジスタと、隣接する2つのスイッチングトランジスタ間に埋め込まれ、該隣接する2つのスイッチングトランジスタの各ゲートから絶縁されかつ該隣接する2つのスイッチングトランジスタのソースまたはドレインに電気的に接続され、上面がスイッチングトランジスタの上面よりも高い位置にあるコンタクトプラグと、コンタクトプラグの上面上に設けられ、データを記憶する記憶素子と、記憶素子上に設けられた配線とを備えている。

(もっと読む)

抵抗変化メモリ

【課題】メモリセルアレイの面積を縮小する。

【解決手段】抵抗変化メモリ10は、第1の方向に延在する複数のビット線BLと、第2の方向に延在する複数のワード線WLと、複数のメモリセルMCを備えたメモリセルアレイ11とを含む。各メモリセルMCは、可変抵抗素子21と選択トランジスタ22とを有し、可変抵抗素子21の第1の端子は第1のビット線に接続され、可変抵抗素子21の第2の端子は選択トランジスタ22のドレインに接続され、選択トランジスタ22のソースは第2のビット線に接続され、選択トランジスタ22のゲートはワード線に接続される。第1の方向に順に並んだ第1乃至第4の可変抵抗素子のレイアウトにおいて、第1及び第2の可変抵抗素子は1本のワード線を挟み、第2及び第3の可変抵抗素子は2本のワード線を挟み、第3及び第4の可変抵抗素子は1本のワード線を挟む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】下層の配線層にMTJ素子を形成しつつ、MTJ素子に熱が加わることを抑制する。

【解決手段】基板10上に絶縁層220を形成する。次いで絶縁層220上にMTJ素子100を形成する。次いで、MTJ素子100上に配線242を形成する。次いで配線242上に絶縁層250を形成する。次いで絶縁層250の表層に配線252を形成する。そして配線252を光照射により熱処理する。そして配線252を形成する工程において遮蔽導体254を形成する。

(もっと読む)

半導体記憶装置

【課題】 製造コストおよびプロセス歩留りの改善が可能となる、抵抗変化素子を含む半導体記憶装置を提供すること。

【解決手段】 第1の方向に並んで設けられた第1および第2のMOSFETと、前記第1および第2のMOSFETの上方に設けられ下端が前記第1および第2のMOSFETのドレインに接続された第1の抵抗変化素子と、第1の方向に並んで設けられた第3および第4のMOSFETと、前記第3および第4のMOSFETの上方に設けられ下端が前記第3および第4のMOSFETのドレインに接続された第2の抵抗変化素子と、前記第1および第2のMOSFETのソースに接続され第1の方向に延びる第1の配線と、前記第3および第4のMOSFETのソースに接続され第1の方向に延びる第2の配線と、前記第1の抵抗変化素子の上端と前記第2の抵抗変化素子の上端とを接続する上部電極と、前記上部電極に接続され第1の方向に延びる第3の配線とを備える。

(もっと読む)

磁気メモリ

【課題】書き込み電流を低減する。

【解決手段】本発明の例に関わる磁気メモリは、磁化が可変な磁性層11と、磁化が固定された磁性層13と、中間層12と、膜面に対して平行方向の磁化が可変な磁性層15とを有する磁気抵抗効果素子1と、絶縁膜を介して磁気抵抗効果素子1の側面上に設けられ、磁性層15の端部から発生する磁場を収束する磁性層16と、を有する。

(もっと読む)

半導体記憶装置

【課題】活性領域の接触面積を増大でき、コンタクト抵抗を低減可能な半導体記憶装置を提供する。

【解決手段】フィン状の活性領域13は、半導体基板11内に設けられ、第1の側面、前記第1の側面に平行する第2の側面、及び前記第1、第2の側面を繋ぐ上面を有する。ワード線の一部としてのゲート電極14は、活性領域に形成された溝17内及び溝を跨いで形成され、活性領域と絶縁されている。シリサイド層16は、ゲート電極の両側の活性領域に位置し、ソース、ドレイン領域としての活性領域の少なくとも第1の側面に形成されている。少なくとも記憶素子21を接続するためのコンタクト15は、シリサイド層に接続されている。

(もっと読む)

半導体集積回路

【課題】セル面積が小さい不揮発性SRAMセルを提案する。

【解決手段】本開示に係わる半導体集積回路は、第1及び第2のインバーターINV1,INV2と、ゲートにワード線WLが接続され、ソースに第1のビット線BLが接続され、ドレインに第2のインバーターINV2の入力端子が接続される第1のトランジスタM5と、ゲートにワード線WLが接続され、ソースに第2のビット線bBLが接続され、ドレインに第1のインバーターINV1の入力端子が接続される第2のトランジスタM6と、第1の端子に第1のトランジスタM5のドレインが接続され、第2の端子に第1のインバーターINV1の出力端子が接続される第1の可変抵抗素子R1と、第1の端子に第2のトランジスタINV2のドレインが接続され、第2の端子に第2のインバーターINV2の出力端子が接続される第2の可変抵抗素子R2とを備える。

(もっと読む)

不揮発磁気薄膜メモリ装置の記録方法

【課題】デバイスの温度が上昇しても、安定的に動作する不揮発磁気薄膜メモリ装置の記録方法を提供する。

【解決手段】不揮発磁気薄膜メモリ装置は、基板と、その基板上に磁気抵抗効果素子を有するメモリセルが二次元状に配されたメモリセルアレイとを有している。不揮発磁気薄膜メモリ装置への情報の記録を行なう前に、メモリセルに情報の試し書きを行ない、試し書きの記録を確認した後、正規のデータを記録する。

(もっと読む)

半導体素子の製造方法

【課題】本発明は半導体素子の製造方法を提供すること。

【解決手段】基板上に下地膜を形成する。前記下地膜上に犠牲膜を形成する。前記犠牲膜をパターニングして前記下地膜の所定領域を露出させる開口部を形成する。前記開口部内にマスク膜を形成する。前記マスク膜の一部または全部を酸化させて酸化物マスクを形成する。前記犠牲膜を除去する。前記酸化物マスクをエッチングマスクとして用いて前記下地膜をエッチングして下地膜パターンを形成する。

(もっと読む)

半導体装置の製造方法

【課題】磁気素子を備えた半導体装置の製造で、磁気素子のダメージを抑止し、下部電極膜の加工に灰化処理を用いないことで下層に存する導電部材の酸化を防止する。

【解決手段】半導体基板10上で、上部電極膜43上に形成したレジストマスク44で上部電極膜43をエッチングして上部電極43aとし、上部電極43aをマスクとしてMTJ膜42をエッチングしてMTJ42aとし、上部電極43a及びMTJ42aを覆う保護膜45aを形成し、上部電極43a及びMTJ42aを保護膜45aを介して覆うように、保護膜45a上にレジスト46を形成し、レジストマスク46で保護膜45aをエッチングし、保護膜45aをマスクとして下部電極膜41エッチングして下部電極41aとし、上部電極43a、MTJ42a及び下部電極41aを覆うように保護膜45bを形成して、保護膜45b上に層間絶縁膜47を形成する。

(もっと読む)

垂直磁気トンネル接合構造体並びにそれを含む磁性素子、及びその製造方法

【課題】垂直磁気トンネル接合構造体並びにそれを含む磁性素子、及びその製造方法を提供することである。

【解決手段】本発明の垂直磁気トンネル接合は、上部磁性層及び下部磁性層のうちいずれか1層の磁性層に自由層を含み、トンネリング層と自由層との間に、分極強化層と交換遮断層とが積層されており、該交換遮断層は、非晶質の非磁性層であり、該分極強化層は、Fe層、体心立方(bcc)構造を有するFe系合金層、CoFeB系非晶質合金層、L21型ホイスラ(Heusler)合金層及びそれらの複合層のうちいずれか1層であり、該非晶質非磁性層は、ジルコニウム・ベース非晶質合金層、チタン・ベース非晶質合金層、パラジウム・ベース非晶質合金層、アルミニウム・ベース非晶質合金層及びそれらの複合層のうちいずれか1層であり、また該非晶質非磁性層は、全体的には非晶質であるが、局所的にはナノ結晶構造を有するものでありうる。

(もっと読む)

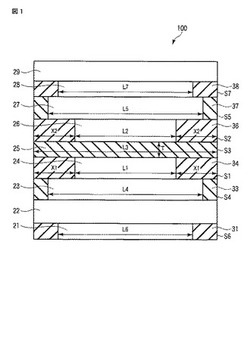

スピン注入型磁気ランダムアクセスメモリ

【課題】スピン注入型磁気ランダムアクセスメモリに関し、同じ面積でスイッチング電流Icの小さなMTJを用いてMulti−levelcell構造を構成するメモリを提供する。

【解決手段】フィルター層22,32が強磁性層23,33/非磁性層24,34/強磁性層25,35からなる反強磁性結合構造を有するとともに互いに異なったスイッチング電流特性を有する強磁性トンネル接合素子21,31を直列に複数個積層し、且つ、前記各強磁性トンネル接合素子21,31の平面面積を同じにする。

(もっと読む)

磁気トンネル接合デバイス及び製造

磁気トンネル接合(MTJ)デバイス及び製造方法が開示される。特定の実施形態では、底部電極(110、702)の上方に磁気トンネル接合構造(202)を形成することを含む方法が開示される。また、本方法は、磁気トンネル接合構造の上方及びこれに隣接する拡散障壁層(302、402)を形成することも含む。本方法は、拡散障壁層をエッチングバックして、磁気トンネル接合構造の上方の拡散障壁層を除去することを更に含む。また、本方法は、磁気トンネル接合構造の頂部 を導電層(604、704)に接続することも含む。  (もっと読む)

(もっと読む)

導電構造物を含む半導体装置及びその製造方法

【課題】容易に抵抗を調節することができ、高集積化が可能な導電構造物を含む半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、基板上に配置され、基板の導電領域を露出させる開口部を含む絶縁膜と、開口部内に配置されるバリア膜パターンと、バリア膜パターン上に配置され、開口部の外部に延長される酸化された部分及び開口部内に位置する酸化されなかった部分を含む導電パターンと、を具備し、導電パターンの幅がバリア膜パターンの厚さによって決定される。

(もっと読む)

101 - 120 / 226

[ Back to top ]