Fターム[4M119KK09]の内容

MRAM・スピンメモリ技術 (17,699) | 集積又は混載技術 (507) | 層間膜 (37)

Fターム[4M119KK09]に分類される特許

1 - 20 / 37

不揮発性半導体記憶装置

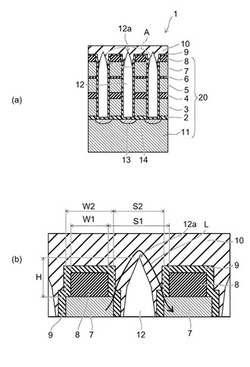

【課題】隣接する配線の間におけるリークを抑制することができる不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1は、シリコンを含む基板11と、基板11の上に設けられた複数のメモリセルと、複数のメモリセルの上方に設けられた配線7と、配線7の上に設けられたリーク抑制層8と、前記リーク抑制層8の上方に設けられた層間絶縁膜10と、を備えている。そして、隣接するメモリセルの間、および、隣接する配線7の間には空隙12が形成され、リーク抑制層8の幅寸法は、配線7の幅寸法よりも短いこと、および、隣接するリーク抑制層8の間の寸法は、隣接する配線7の間の寸法よりも長いこと、の少なくともいずれかである。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】MTJ素子内における層間の短絡を抑制し、かつ、MTJ素子を構成する磁性層の劣化を抑制した半導体記憶装置およびその製造方法を提供する。

【解決手段】本実施形態による半導体記憶装置は半導体基板を備える。磁気トンネル接合素子は、2つの磁性層と該2つの磁性層間に設けられたトンネル絶縁膜とを含み、半導体基板の上方に設けられている。側壁膜は、磁気トンネル接合素子の側面の上部に設けられている。フェンス層は、導電性材料を含み、側壁膜の側面および磁気トンネル接合素子の側面の下部に設けられている。保護膜は、絶縁体からなりフェンス層の側面に設けられている。フェンス層の上面および保護膜の上面は、側壁膜の上面よりも低く、かつ、トンネル絶縁膜よりも高い位置にある。

(もっと読む)

磁気抵抗効果素子及びその製造方法

【課題】素子特性の劣化なしにリデポ現象による電気的ショートを防止する。

【解決手段】実施形態に係わる磁気抵抗効果素子は、磁化方向が可変の記憶層11と、記憶層11上のトンネルバリア層12と、トンネルバリア層12上の磁化方向が不変の参照層13と、参照層13上のハードマスク層14と、参照層13及びハードマスク層14の側壁上の側壁スペーサ層17とを備える。記憶層11及び参照層13は、垂直磁化を有し、参照層13の平面サイズは、記憶層11の平面サイズよりも小さい。記憶層11及び参照層13のサイズ差は、2nm以下であり、側壁スペーサ層17は、ダイアモンド、DLC、BN、SiC、B4C、Al2O3及びAlNのうちの1つを備える。

(もっと読む)

半導体記憶装置

【課題】磁気抵抗効果素子間の磁気的な干渉作用を遮断し、安定した動作を可能にし、且つ、容易に製造することができる半導体記憶装置を提供する。

【解決手段】本発明の実施形態にかかる半導体記憶装置は、半導体基板上にマトリックス状に配列した複数の磁気抵抗効果素子を有し、各磁気抵抗効果素子は、半導体基板上に形成された第1の磁性層と、第1の磁性層上に形成された非磁性層と、非磁性層上に形成された第2の磁性層とからなる積層構造を有し、隣り合う各磁気抵抗効果素子の間には、金属、又は、磁性体材料が分散された絶縁膜が埋め込まれている。

(もっと読む)

磁気記憶装置の製造方法および磁気記憶装置

【課題】TMR素子間の特性のばらつきを低減でき、かつ製造歩留まりの高い不揮発性磁気メモリの製造方法およびその構造を提供する。

【解決手段】TMR素子を含む磁気記憶装置の製造方法が、配線層が設けられた層間絶縁膜の上に、絶縁膜を形成する工程と、絶縁膜に、配線層が露出するように開口部を形成する開口工程と、開口部を埋めるように、絶縁膜上に金属層を形成する金属層形成工程と、CMP法を用いて絶縁膜上の金属層を研磨除去し、開口部内に残った金属層を下部電極とするCMP工程と、下部電極上にTMR素子を形成する工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】積層ハードマスクを部分的に残存させつつ、配線層用のビアプラグのアスペクト比を低減することが可能な半導体装置及びその製造方法を提供する。

【解決手段】基板上に第1の配線層102を形成し、第1の配線層102上に、半導体素子材料103、第1の絶縁膜104、及び第2の絶縁膜105を順に形成し、半導体素子材料103、第1の絶縁膜104、及び第2の絶縁膜105を含むピラー状の構造体を形成する。第1の配線層102上に、構造体の上面及び側面を覆うように、第3及び第4の絶縁膜109,106を形成し、第4の絶縁膜106を、第2の絶縁膜105が露出するように、部分的に除去する。第1及び第2の絶縁膜内に、半導体素子材料に接続された第1のビアプラグ107を形成し、第3及び第4の絶縁膜内に、第1の配線層102に接続された第2のビアプラグ108を形成し、第1及び第2のビアプラグ上に第2の配線層111を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ロジック混載MRAMにおいて、LSIの多層配線形成プロセスがMRAMの特性変動を引き起こす不都合、また、MRAMの形成プロセスが多層配線の特性変動を引き起こす不都合を軽減すること。

【解決手段】多層配線層に含まれる配線層Aの中に、配線層Bに形成された第1の配線104bに接し、互いに絶縁している少なくとも2つの第1の磁化固定層50a及び50bと、2つの第1の磁化固定層50a及び50bと平面視で重なり、かつ、第1の磁化固定層50a及び50bと接続している磁化自由層10と、磁化自由層10の上に位置する非磁性層40と、非磁性層40の上に位置する第2の磁化固定層104aと、を有するMRAMが形成されている半導体装置。

(もっと読む)

磁気トンネル接合素子及び磁気ランダムアクセスメモリ

【課題】 書込み電流の低減のみならず、大きなMR比を有するMTJ素子の開発が望まれている。

【解決手段】 磁気トンネル接合素子が、磁化自由層と、磁化固定層と、磁化自由層と磁化固定層との間に配置されたトンネルバリア層とを有する。磁化自由層は、垂直磁化自由層、垂直磁化自由層とトンネルバリア層との間に配置された面内磁化自由層、及び垂直磁化自由層と面内磁化自由層との間に配置された非磁性中間層とを含む。垂直磁化自由層の磁化容易方向は膜面に対して垂直であり、面内磁化自由層の磁化容易方向は膜面に平行であり、垂直磁化自由層の磁化は、非磁性中間層を介して面内磁化自由層と交換結合することによって、面内方向を向いている。

(もっと読む)

磁気トンネル接合素子及び磁気ランダムアクセスメモリ

【課題】 GMR素子では、十分大きなMR比を得ることが困難である。大きなMR比を実現することが可能なMTJ素子において、反転電流を低減させることが望まれている。

【解決手段】 下部電極の上に、磁化容易方向が厚さ方向を向く垂直磁気異方性膜が形成されている。垂直磁気異方性膜の上に、非磁性材料で形成されたスペーサ層が配置されている。スペーサ層の上に、アモルファスの導電材料からなる下地層が配置されている。下地層の上に、磁化容易方向が面内方向を向く磁化自由層が配置されている。磁化自由層の上にトンネルバリア層が配置されている。トンネルバリア層の上に、磁化方向が面内方向に固定された磁化固定層が配置されている。スペーサ層は、垂直磁気異方性膜と磁化自由層との間に交換相互作用が働かない厚さであり、かつスピン緩和長よりも薄い。

(もっと読む)

半導体装置

【課題】隣接するビット線同士の短絡が抑制されており、かつ層間絶縁膜が平坦に研磨された半導体装置を提供する。

【解決手段】磁気抵抗素子MRDが複数配置されたメモリセル領域と、平面視においてメモリセル領域の周囲に配置された周辺回路領域とを備える。磁気抵抗素子MRDは、磁化固定層と磁化自由層とトンネル絶縁層とを含んでいる。磁気抵抗素子MRDの上方には、主表面に沿った方向に向けて延びる複数の第1の配線BLを有している。上記周辺回路領域には、第1の配線BLと同一レイヤにより構成される第2の配線BL2と平面視において重なるように、磁化自由層と同一材質の層、トンネル絶縁層と同一材質の層および磁化固定層と同一材質の層が積層された積層構造DMMが配置されている。積層構造DMMは、周辺回路領域にて平面視において隣接する1対の第2の配線BL2の両方と重ならない。

(もっと読む)

磁気抵抗素子の製造方法

【課題】磁気特性の低下の抑制を図る。

【解決手段】磁気抵抗素子の製造方法は、磁化の方向が不変の固定層4、コバルトまたは鉄を含み、磁化の方向が可変の自由層6、および前記固定層と前記自由層との間に挟まれる非磁性層5で構成される積層体を形成し、前記積層体上に、ハードマスク11を形成し、前記ハードマスクをマスクとして塩素を含むガスで前記積層体をエッチングし、エッチングされた前記固定層および前記自由層の側面に、ボロンと窒素とを含む絶縁膜14を形成する。

(もっと読む)

不揮発性磁気メモリ装置

【課題】記録層における磁化容易軸が垂直方向を向いている垂直磁化型の不揮発性磁気メモリ装置において、記録層の磁化容易軸をより確実に垂直方向に向かせることを目的とする。

【解決手段】不揮発性磁気メモリ装置は、磁化容易軸が垂直方向を向いている記録層を有する積層構造体50、第1の配線41、及び、第2の配線42から成る磁気抵抗効果素子を備えており、積層構造体50の上、又は、積層構造体50の下、又は、積層構造体50の上及び下には、記録層53を構成する材料のヤング率よりも低い値のヤング率を有する低ヤング率領域481が配置されており、積層構造体50は磁化参照層51を更に有し、低ヤング率領域481を配置することによって記録層53及び磁化参照層51において内部応力が発生し、記録層53及び磁化参照層51の垂直磁気異方性が増大される。

(もっと読む)

媒体を製造するためのシステムおよび方法

【課題】媒体を製造するシステムおよび方法を提供する。

【解決手段】媒体を製造する方法は、基板上に記録媒体を形成するステップを含む。記録媒体上の、基板と反対側に保護膜が成膜される。保護膜は第一の表面仕上げ層を有する。保護膜はエッチングされ、材料が取り除かれ、保護膜に、第一の表面仕上げより平滑な第二の表面仕上げ層が設けられる。成膜とエッチングは、in−situドライ真空工程で逐次的に行われてもよい。第二の表面仕上げ層には、エッチング後に、保護膜をさらに平坦化するための機械加工を行わなくてもよい。

(もっと読む)

半導体装置およびその製造方法

【課題】生産コストを抑えながら高いスループットが得られる半導体装置の製造方法と半導体装置とを提供する。

【解決手段】ヨークカバーとなる積層膜として、バリアメタル層、磁性体層およびバリアメタル層が順次形成される。次に、積層膜MLに、四フッ化炭素(CF4)ガスとアルゴン(Ar)ガスとの混合ガスによる反応性イオンエッチング処理、一酸化炭素(CO)、アンモニア(NH3)ガスおよびアルゴン(Ar)ガスの混合ガスによる反応性イオンエッチング処理、四フッ化炭素(CF4)ガスとアルゴン(Ar)ガスとの混合ガスによる反応性イオンエッチング処理を施すことにより、ヨークカバーYCが形成される。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】記憶素子の下にあるコンタクトプラグの上面の平坦性を改善し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、半導体基板上に設けられた複数のスイッチングトランジスタと、隣接する2つのスイッチングトランジスタ間に埋め込まれ、該隣接する2つのスイッチングトランジスタの各ゲートから絶縁されかつ該隣接する2つのスイッチングトランジスタの拡散層に電気的に接続されたコンタクトプラグと、コンタクトプラグ上に形成され、上面がスイッチングトランジスタの上面よりも高い位置にある上部コネクタと、上部コネクタの上面上に設けられ、データを記憶する記憶素子と、記憶素子上に設けられた配線とを備えている。

(もっと読む)

半導体装置および半導体装置アセンブリ

【課題】外部からの磁場を遮蔽する磁気シールド効果が高い半導体装置を提供する。

【解決手段】半導体基板SUBの主表面上に形成されたスイッチング素子TRを覆うように形成された層間絶縁膜III1と、平板状の引出配線LELと、引出配線LELとスイッチング素子TRとを接続する接続配線ICLと、磁化の向きが可変とされた磁化自由層MFLを含み、引出配線LEL上に形成された磁気抵抗素子TMRとを備える。磁化自由層MFLの磁化状態を変化させることが可能な配線DLと配線BLとを備えている。磁気抵抗素子TMRが複数並んだメモリセル領域において、磁気抵抗素子TMRの上部に配置された第1の高透磁率膜CLAD2が、上記メモリセル領域から、メモリセル領域以外の領域である周辺領域にまで延在している。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】絶縁膜の比誘電率を容易かつ十分に低下させる。

【解決手段】半導体装置の製造方法では、それぞれ環状SiO構造を主骨格とし互いに構造が異なる2種類以上の有機シロキサン化合物原料を混合した後で気化する。又は、それら2種類以上の有機シロキサン化合物原料の混合と気化とを一度に行うことによって、気化ガスを生成する。そして、その気化ガスをキャリアガスとともに反応炉に輸送する。そして、反応炉にてその気化ガスを用いたプラズマCVD法又はプラズマ重合法によって多孔質絶縁膜を成膜する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】磁気抵抗素子への不純物の侵入や応力の負荷を抑制し、低い駆動電力で高精度に作動する半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置は、主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に位置する磁気抵抗素子MRDとを備えている。その他、保護層IIIと、配線BLと、第1上部電極UEL1と、第2上部電極UEL2とを備えている。保護層IIIは、磁気抵抗素子MRDの側面を覆うように配置されている。配線BLは、上記磁気抵抗素子MRDの上部に位置する。第1上部電極UEL1は、上記磁気抵抗素子MRD上に、平面視における大きさが磁気抵抗素子MRDと実質的に同じであるものが配置されている。第2上部電極UEL2は、上記第1上部電極UEL1上にて、上記第1上部電極UEL1と電気的に接続されており、平面視における大きさが第1上部電極UEL1より大きい。

(もっと読む)

磁気抵抗効果素子構造体、磁気ランダムアクセスメモリ、および、空間光変調器

【課題】素子作製時の加熱や、電流注入によって生じる熱等による磁気抵抗効果素子の特性劣化を防止することができる磁気抵抗効果素子構造体、この磁気抵抗効果素子構造体を用いた磁気ランダムアクセスメモリ、この磁気抵抗効果素子構造体を用いた空間光変調器を提供する。

【解決手段】固定層101と、中間層102と、反転層103とが積層された磁気抵抗効果素子10を有し、固定層101に、遷移金属と希土類金属との磁性合金、Mnを含む磁性合金、または、磁性多層膜のうちのいずれかを用いた磁気抵抗効果素子構造体1であって、磁気抵抗効果素子10の上面に設けられた上部電極11および磁気抵抗効果素子10の下面に設けられた下部電極12の間に、当該電極間を絶縁するための絶縁材13を備え、絶縁材13は、MgF2誘電体材料13aであり、MgF2誘電体材料13aは、固定層101の側面に当接して設けられていることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】磁気抵抗素子の短絡不良等が軽減される半導体装置と、その製造方法とを提供する。

【解決手段】メモリセルが形成される層間絶縁膜33において、磁気抵抗素子51が形成されるメモリセル領域Mに位置する層間絶縁膜33の部分の上面の位置が、周辺領域Pに位置する層間絶縁膜33の部分の上面の位置よりも低く形成されている。磁気抵抗素子51を覆うように、層間絶縁膜40が形成されている。その層間絶縁膜40に、磁気抵抗素子に電気的に接続されるビット線41が形成されている。磁気抵抗素子51の直下にディジット線31が形成されている。

(もっと読む)

1 - 20 / 37

[ Back to top ]