Fターム[5B015KB66]の内容

Fターム[5B015KB66]に分類される特許

1 - 20 / 42

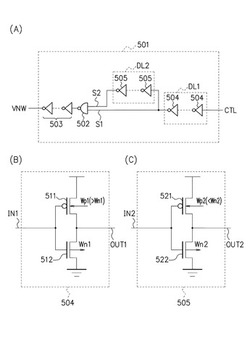

メモリ装置

【課題】高速にデータを書き込むことができるメモリ装置を提供することを課題とする。

【解決手段】メモリ装置は、第1及び第2のpチャネルトランジスタと、第1のpチャネルトランジスタ及び第2のpチャネルトランジスタのバックゲートに第2のバックゲート信号を出力するバックゲート信号生成回路(501)とを有し、バックゲート信号生成回路は、第1の遅延回路(DL1)と第2の遅延回路(DL2)とを有し、第1の遅延回路は、第3のpチャネルトランジスタ及び第3のnチャネルトランジスタを含む第1のインバータ(504)を有し、第3のpチャネルトランジスタは、第3のnチャネルトランジスタよりゲート幅が広く、第2の遅延回路は、第4のpチャネルトランジスタ及び第4のnチャネルトランジスタを含む第2のインバータ(505)を有し、第4のpチャネルトランジスタは、第4のnチャネルトランジスタよりゲート幅が狭い。

(もっと読む)

半導体装置

【課題】ロジックと揮発メモリが混載されたシステムLSIのスタンバイ状態の消費電力を低減する。

【解決手段】システムLSI中のロジック回路と第1電源線の間に第1スイッチを設けるとともに、揮発メモリの少なくとも一部と第1電源線の間に第2スイッチを設ける。スタンバイ時には該第1スイッチと第2スイッチをオフして電源を遮断する。同時に揮発メモリの少なくとも他の一部では、スタンバイ時の基板バイアスを制御してリーク電流を低減する。

(もっと読む)

半導体装置

【課題】待機時のリーク電流が少なく、かつ、データ保持特性に優れたSRAMセルを備えた半導体装置を提供する。

【解決手段】それぞれ負荷MOSトランジスタを備えた複数のSRAMセルがマトリクス状に配置されたメモリセルアレイ110と、メモリセルアレイの第1の電源端子VDDMと第2の電源端子VSSMとの間に電源を供給する電源回路130と、負荷MOSトランジスタに基板バイアス電圧を与える基板バイアス発生回路140と、動作時より待機時の方が、第1の電源端子と第2の電源端子との間の電位差が小さく、かつ、負荷MOSトランジスタの基板バイアス電圧が浅くなるように電源回路と基板バイアス発生回路とを制御する電圧制御回路200と、を備える。

(もっと読む)

半導体装置

【課題】先端プロセスでは、MOSのゲートトンネルリーク電流が増大し、低リーク電流での待機が必要となる半導体装置では問題となる。

【解決手段】電源線とソース線との電位差である複数のスタティック型メモリセルの電源電圧を制御する電源電圧制御回路を具備する。負荷型P型MOS及び駆動型N型MOSのゲート絶縁膜厚は、4nm以下である。電源電圧制御回路は、動作状態では前記電源電圧を第1電圧とし、待機状態では前記電源電圧を前記第1電圧よりも小さい第2電圧とするように制御して、オフ状態での負荷型P型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流、及び、駆動型N型MOSのソース電極とゲート電極の間に流れるゲートトンネルリーク電流を動作状態に対し待機状態の方を小さくする。

(もっと読む)

半導体集積回路装置

【課題】メモリセルのリーク電流成分に応じて、最適な電圧制御を行い、リーク電流を大幅に低減する。

【解決手段】レジュームスタンバイモードにおいて、リーク種判定回路7はリーク電流の成分がゲートリークと基板リークが多いと判断すると、VDDRレギュレータ5は電源電圧VDDよりも低い第1の電圧レベルの電源電圧VDDRを生成し、切り替えスイッチ9を介して、電源電圧VDDR1としてSRAMモジュール12に供給する。リーク種判定回路7がチャネルリークが多いと判断すると、VDDRレギュレータ5は第1の電圧レベルよりも高く、電源電圧VDDよりも低い電源電圧VDDR1をSRAMモジュール12に供給する。また、ARVSSレギュレータ6は、基準電圧VSSよりも高いセルソース電源電圧ARVSS1を領域2のSRAMモジュール12に供給する。

(もっと読む)

SRAMメモリセル

【課題】現存のデバイスの欠点を取り除き、さらにSRAM型メモリセルの体積を減少させる。

【解決手段】SRAM型メモリセルであって、絶縁層によってベース基板から隔離された半導体材料の薄膜を含む絶縁基板上の半導体と、2個のアクセストランジスタT1,T4と、2個の伝導トランジスタT2,T5と、2個の充電トランジスタT3,T6とを含み、メモリセルは、トランジスタT1−T6のそれぞれが、チャネルの下方でベース基板内に形成されたバックコントロールゲートBG1,BG2を有し、トランジスタの敷居電圧を調整するようにバイアスをかけられ、第1のバックゲートラインはアクセストランジスタT1,T4に接続し、第2のバックゲートラインは伝導トランジスタT2,T5および充電トランジスタT3,T6に接続し、各々の電位はセル制御動作の型に応じて調整される。

(もっと読む)

半導体装置、センスアンプ回路、半導体装置の制御方法及びセンスアンプ回路の制御方法

【課題】ダブルゲートトランジスタを用いた機能回路のバックゲート電圧を適切に制御して良好な特性を実現可能な半導体装置等及びその制御方法を提供する。

【解決手段】本発明の半導体装置は、ダブルゲートトランジスタを含む機能回路と、ダブルゲート構造の基準トランジスタ20、30を含む電圧制御回路を備えている。基準トランジスタ20、30には、第1ゲート電極に参照電圧Vrp、Vrnが印加され、第2ゲート電極の電位はドレイン電流Ip、Inが参照電流Irp、Irnと一致するように制御され、その電位が制御電圧VBGP、VBGNとして出力される。制御電圧VBGP、VBGNを機能回路のダブルゲートトランジスタの第2ゲート電極に印加することで機能回路に所望の特性が付与される。

(もっと読む)

半導体記憶装置

【課題】書き込み時の記憶ノードの電位の反転性を保証しつつ、記憶ノードのプルアップを高速化する。

【解決手段】ウェル電位制御部13は、書き込みサイクル内においてワード線WLの電位がハイレベルからロウレベルに移行するタイミングでメモリセルMCのPチャンネル電界効果トランジスタM1、M2のNウェル電位を下降または電源電位を上昇させる。

(もっと読む)

半導体装置

【課題】メモリが混載されたシステムLSIのリーク電流を低減し、スタンバイ状態の消費電力を低減する。

【解決手段】システムLSI中のロジック回路には電源スイッチを設け、スタンバイ時にはそのスイッチを遮断してリーク電流を低減する。同時にSRAM回路では、基板バイアスを制御することと、リードアンプあるいはライトアンプへの電源スイッチを設け、且つそのスイッチを遮断してリーク電流を低減する。

(もっと読む)

半導体装置

【課題】グローバルな閾値ばらつきの補正機能を備えた半導体装置を提供すること。

【解決手段】測定回路9は、SRAM2,3,4のいずれか1つのSRAMに、通常電圧よりも低い電圧で書き込みを行った後に通常電圧で読み出すことを各メモリセルに実行して書込不良ビット数を検出し、また、通常電圧で書き込みを行い、通常電圧よりも低い電圧での読み出しと通常電圧での読み出しとを行うことを各メモリセルに実行してディスターブ不良ビット数を検出し、検出した書込不良ビット数とディスターブ不良ビット数との大小関係からグローバルな閾値ばらつきの状態を判断し、数が多い方の不良ビット数から印加するバックゲートバイアスを決定し、ヒューズボックス7に記録する。ウェルバイアス生成回路8がヒューズボックス7に記録されたバックゲートバイアスに基づき生成するウェルバイアスにより搭載される全てのSRAMにバックゲートバイアスが印加される。

(もっと読む)

半導体集積回路

【課題】 サブスレッショルドリーク電流を抑制し、動作電源の変動によるスタティックメモリセルのデータ破壊を抑制する。

【解決手段】 半導体集積回路は、一対の電源配線(10,11)と、複数個のスタティックメモリセル(18)と、前記電源配線から前記スタティックメモリセルに印加する動作電圧を制御する電圧制御回路(20)と、前記電源配線の電圧をモニタするモニタ回路(21)と、動作モードを制御するモード制御回路(5)と、を含む。モニタ回路は、前記一対の電源配線間の電位差が縮小する変化を検出することが可能である。電圧制御回路は、モード制御回路による低消費電力モードの指示に応答してスタティックメモリセルの一対の電源ノードの電位差を小さくする方向に制御し、モニタ回路による前記一対の電源配線間の電位差縮小の検出に応答してスタティックメモリセルの一対の電源ノードの電位差を大きくする方向に制御することが可能である。

(もっと読む)

半導体装置

【課題】メモリセルの書込み及び読出しマージンの劣化を自動的に補償することができる半導体装置を提供する。

【解決手段】半導体装置は、ワード線の選択期間を決めるためのワード線タイミング信号と基準信号とを比較し、その比較結果が読み出しマージンの低い状態に応ずるときは読み出しマージンを拡大する基板バイアスを印加し、逆にその比較結果が書き込みマージンの低い状態に応ずるときは書き込みマージンを拡大する基板バイアスを印加する。基準信号は、ワード線選択期間(ワード線パルス幅)によって変動する動作マージンを補償する場合、プロセス変動(閾値電圧のばらつき)によって変動する動作マージンを補償する場合に応じて選択される。ワード線パルス幅により基板バイアスを制御することで、ワード線パルス幅によって変動する動作マージンを改善し、また、製造時の閾値電圧のばらつきによって変動する動作マージンを改善する。

(もっと読む)

負電圧生成回路及びこれを用いた半導体メモリ装置

【課題】本発明は、トランジスタのバルクに印加される第1の負電圧がターゲットレベルに到達した後、トランジスタのソースに印加される第2の負電圧を生成する半導体メモリ装置の負電圧生成回路を提供する。

【解決手段】本発明は、第1の負電圧レベルを感知して、第1の感知信号を生成する第1の感知部;第1の感知信号に応じて、第1の負電圧を生成する第1の負電圧生成部;第2の負電圧レベルを感知して、第2の感知信号を生成する第2の感知部;パワーアップ信号がイネーブルされ、第1の感知信号がディセーブルされると、第2の感知信号をイネーブル信号として出力するタイミング制御部;及び、イネーブル信号に応じて、第2の負電圧を生成する第2の負電圧生成部を含む。

(もっと読む)

半導体メモリデバイス

【課題】MCUの発生抑制に有効な構成の半導体メモリデバイスを提供する。

【解決手段】ソースがGND電圧の供給線に接続され、ドレインが負荷素子(PMOS)を介して電源電圧Vddの供給線に接続されるN型の駆動トランジスタN1,N2を含むSRAMセル100と、N型の駆動トランジスタN1,N2が形成されるPウェル20PをGND電圧より低い所定のバックバイアス電圧(−VBB)に制御する基板バイアス制御回路8と、を有する。

(もっと読む)

スタティック型半導体記憶装置

【課題】スタティック型半導体記憶装置のメモリセルのトランジスタの基板電圧を、早いタイミングで所定電圧レベルに駆動し、スタティック・ノイズ・マージンを十分に確保し、安定にデータの読出を行なう。

【解決手段】メモリセルの負荷トランジスタ(PQ1,PQ2)の基板領域へ印加される基板電圧(VPS)の遷移を、遅くともワード線(WL)の選択状態への駆動タイミングまでのタイミングに設定する。

(もっと読む)

半導体記憶装置及びその駆動方法

【課題】メモリセル縮小化による効果を十分に確保しながら、書き込み特性を向上させることができる半導体記憶装置(SRAM)及びその駆動方法を提供する。

【解決手段】半導体基板に形成された第1及び第2ドライバトランジスタ(DTr1,DTr2)、第1及び第2ロードトランジスタ(LTr1,LTr2)、第1及び第2転送トランジスタ(TTr1,TTr2)が形成され、第1及び第2記憶ノード(ND,/ND)が構成される第1及び第2インバータを有し、第1転送トランジスタを介してビットラインBLに、第2転送トランジスタを介して反転ビットライン/BLに接続するメモリセルMCが複数個集積されており、メモリセルにデータを書き込む際に、第1転送トランジスタ及び第2転送トランジスタを構成する半導体基板の部分がフローティング(浮遊)状態になるように制御する制御部が設けられている構成とする。

(もっと読む)

コンパイラブルメモリマクロ、半導体記憶回路、及びそれらを用いた半導体集積回路、並びに半導体記憶回路の構成方法

【課題】回路規模を増大させることなく付加的な機能を追加するコンパイラブルメモリマクロを提供すること。

【解決手段】コンパイラブルメモリマクロ1は、最低限必要な複数の基本的機能を提供する一般ブロックA〜Eと、一般ブロックA〜Eの少なくとも一つに対して、基本的機能とは異なる機能を提供する特殊ブロックであるVSSレベル昇圧回路14とを備える。一般ブロックA〜Eは、予め決められた配置規則に従って配置されている。VSSレベル昇圧回路14は、配置規則に従って一般ブロックA〜Eが配置された際に生じるデッドスペースDSに、配置されている。

(もっと読む)

半導体集積回路

【課題】半導体集積回路において、進んだ製造プロセスにおいても、無駄に面積のオーバーヘッドが生じないメモリセルを実現する。

【解決手段】情報保持回路2Bは、第1の反転回路18Aと、連続して直列に接続された同極の2個のトランジスタ18c、18dを有する第2の反転回路18Bとを備える。前記第1の反転回路18Aの出力は前記第2の反転回路18Bの入力に接続され、前記第2の反転回路18Bの出力は前記第1の反転回路18Aの入力に接続される。書き込み用ポートAWは、前記情報保持回路2Bに接続される。前記第2の反転回路18Bの同極の2個のトランジスタ18c、18dのうち1つのトランジスタ18cのゲートは、前記書き込み用ポートAWのデータ信号が入力される。

(もっと読む)

半導体記憶装置及び半導体装置

【課題】バリッドビットにおける無効化処理において、電源投入時に無効化処理を行うことができる半導体記憶装置を提供する。

【解決手段】第1のトランジスタと、第2のトランジスタと、を有する第1のインバータ回路と、入力部が前記第1のインバータ回路の出力部に接続され、出力部が前記第1のインバータの入力部に接続され、第3のトランジスタと、第4のトランジスタと、を有する第2のインバータ回路と、を含む初期化用メモリセルを有し、第3のトランジスタのしきい値電圧の絶対値は、第1のトランジスタのしきい値電圧の絶対値より低い構成とする。

(もっと読む)

半導体記憶装置

【課題】低電圧でSRAM回路を動作させるために構成するトランジスタのしきい値電圧を下げると、トランジスタのリーク電流の増加により、データを記憶しながら動作していない状態での消費電力が増加するという問題がある。

【解決手段】SRAMメモリセルMC内の駆動MOSトランジスタのソース線sslの電位を制御することでメモリセル内のMOSトランジスタのリーク電流を低減する。

(もっと読む)

1 - 20 / 42

[ Back to top ]