Fターム[5B017CA01]の内容

Fターム[5B017CA01]に分類される特許

101 - 120 / 211

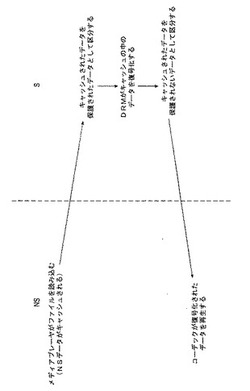

キャッシュメモリの中の制御データの修正

【課題】キャッシュメモリの中の制御データを処理するための装置及び方法を提供する。

【解決手段】データ処理システムは、少なくとも1つのプロセッサ4、6と、メインメモリ18と、キャッシュメモリ14とを提供される。キャッシュメモリ14の中のキャッシュデータは、有効データ及びそれに関連付けられた制御データを有する。制御データは、キャッシュされたデータに対するアクセスを制御する。プロセッサ4、6によって実行されるプログラム命令は、キャッシュされたデータと関連付けられた制御データがキャッシュメモリ14の中に格納された状態を維持すると共に有効な状態を維持したままで、該制御データを修正するように、キャッシュコントローラ26を制御する。制御データは、例えば、プロセッサまたは複数のプロセッサを保証するために、アクセスが制限されるか否かを示すセキュリティフラグを指定し得る。

(もっと読む)

コンピュータメモリ保護方式の拡張機構

【課題】中央処理装置(CPU)内の既存のアドレス変換バッファーが同時にレガシーオペレーティングシステムソフトウェアとのコンパチビリティを保存しながら提供することができるものを越えて、CPUが仮想メモリに与えられる保護方式を拡張できるようにする装置および方法が提供される。

【解決手段】この装置はアドレス変換バッファー(TLB)および拡張保護論理を含んでいる。アドレス変換バッファー(TLB)は複数のTLBエントリを格納し、その各々がフラグフィールドおよび拡張フラグフィールドを有する。拡張保護論理はTLBに接続されている。拡張保護論理はフラグフィールドに従ったレガシーアクセス制約を指定し、かつ拡張フラグフィールドと結合したフラグフィールドに従った拡張アクセス制約を指定する。レガシーアクセス制約の仕様はレガシー仮想ページアクセス保護プロトコルとのコンパチビリティを保存する。

(もっと読む)

メモリ消去プログラム、装置及び方法

【課題】 作業の中断時間に不正にアクセスされた場合でも、データの漏洩を阻止する。

【解決手段】 メモリ消去プログラム3の実行により、休止モード、スタンバイモード又はシャットダウンモードに移行する前にOS2のモード移行コマンドを保留し(ST2)、消去対象に対応するモードであれば(ST3)、消去対象のメモリ識別情報に対応するメモリアドレスに基づいてメモリ領域内のデータを消去し(ST4,ST9〜ST14)、このデータの消去が完了した後、保留したモード移行コマンドを有効にする(ST15)。これにより、移行したモードにおいては、作業中の各種プログラムで処理したデータが消去されているので、上記課題を解決できる。

(もっと読む)

書込プロテクトされたメモリ管理ユニット・レジスタを備える論理デバイス

制御モジュール(110)と、メモリ管理ユニット(105)と、メモリ・モジュール(120)と、少なくとも1つの第1のレジスタ(140)と、を含む論理デバイス(100)。メモリ管理ユニット(105)は、制御モジュール(110)とメモリ・モジュール(120)との間のソフトウェア・コードの流れを制御する。制御モジュール(110)は、メモリ・モジュール(120)内の少なくとも1つのデータ・メモリ・セクション(130)を指定するために、論理デバイス(100)の起動手順中に第1のレジスタ(140)のうちの少なくとも1つをプログラムする。メモリ管理ユニット(105)は、データ・メモリ・セクション(130)を識別するために、第1のレジスタ(140)と通信し、メモリ管理ユニット(105)は、データ・メモリ・セクション(130)内のストレージから実行可能コードを除外する。起動手順の終了後、第1のレジスタ(140)は書込プロテクトされ、論理デバイス(100)をシャットダウンさせずにメモリ管理ユニット(105)を動作不能にすることはできない。  (もっと読む)

(もっと読む)

メモリドメインを基にしたデータ処理システム内のセキュリティ制御

【課題】アクセス制御データに応じて所定のメモリアドレスへのアクセスを制御する。

【解決手段】メモリアドレス空間へのアクセスは、アクセス制御データを使用したメモリアクセス制御回路によって制御される。アクセス制御データを変更する権限は、ドメイン制御回路によって制御される。メモリアドレスの集合である特定のドメイン内に記憶される命令がアクセス制御データを修正することができるか否かは当該ドメインに依存する。従って、アクセス制御データを変更する権限は、メモリアドレス空間内の特定の定義された位置の中に記憶された命令に制限することが可能であり、セキュリティを向上させる。この権限は、OSへの呼び出し転送が呼び出し転送コードを介して強制され、非セキュアOSの制御の下で実行する信頼されたソフトウェアによってのみ当該データがアクセス可能であり、メモリアドレス空間の信頼された領域を確立することができる。

(もっと読む)

保護された関数呼び出し

【課題】データ処理システムの動作のセキュリティを向上させる。

【解決手段】メモリアドレス空間はドメインに分割され、命令アクセス制御回路を使用して、実行される命令が取り込まれるメモリアドレスが、いつドメイン境界を横切り、変化したかを検出し、その場合に、新たなドメイン内の命令が許可された形態の許容命令であることを確認するために検査を行う。許容命令は、下位互換性を助けるために、命令アクセス制御回路に関する以外はノーオペレーション命令であるように決めておくことができる。

(もっと読む)

情報処理装置

【課題】プロセッサが仮想化サポート機能を有するか否かによらず、安全性を向上させる。

【解決手段】プロセッサと、HV保護領域にアクセス可能なハイパーバイザを記憶する保護メモリと、保護メモリとプロセッサとを接続した第1通信路と、第1通信路を介して、ハイパーバイザの起動時に実行されるエントリ部に含まれる複数の命令のうち、最初の命令のアドレスへのフェッチを検出するフェッチ検出部と、第1通信路を介して、エントリ部の最後の命令の実行を検出する命令検出部と、フェッチを検出してから、最後の命令の実行を検出するまで所定の時間が経過したか否かを判断する時間判断部と、所定の時間が経過していないと判断した場合、最後の命令の実行結果から、プロセッサの割り込みを禁止しているか否かを判断する実行判断部と、禁止していると判断した場合に、プロセッサにHV保護領域のアクセスを開放する第1及び第2HV領域保護回路と、を備える。

(もっと読む)

情報処理装置

【課題】アドレスを暗号化しつつ、DRAMへのアクセス速度の低下を低減することができる情報処理装置を提供する。

【解決手段】CPU2から出力されたアドレスにおけるローアドレスを示す部分であるアドレス信号A15〜A24をローアドレス信号RAに変換するローアドレス変換部5と、CPU2から出力されたアドレスにおけるカラムアドレスを示す部分であるアドレス信号A5〜A14をカラムアドレス信号CAに変換するカラムアドレス変換部6とを備えた。また、ローアドレス信号RA、及びカラムアドレス信号CAを指定してDRAM8へのアクセスを行うと共に、ローアドレス信号RAが同一であるメモリアドレスへのアクセスが複数回連続する場合、二回目以降のアクセスにおいてローアドレス信号RAの指定を行わないDRAMコントローラ7を備えた。

(もっと読む)

端末装置およびプログラム

【課題】アプリケーションプログラムの詳細情報についてのセキュリティを確保しつつ、その詳細情報の表示を迅速に行うことを可能にする。

【解決手段】複数のアプリケーションプログラムの各々の基本情報と詳細情報とがアプリケーションプログラム毎に異なる記憶領域に記憶されているとともに、各記憶領域に対して他のアプリケーションプログラムがアクセスすることを禁止する端末装置に、各アプリケーションプログラムの基本情報を含んでいる画面を表示させ、何れかの基本情報の表示位置にカーソルが移動された場合に、該カーソルを位置付けられた基本情報に対応する第1のアプケーションプログラムの詳細情報と、該基本情報に隣接して基本情報が表示されている第2のアプリケーションプログラムの詳細情報とを該当する記憶領域から読み出し、第1のアプリケーションプログラムの詳細情報を表示する処理を実行させる。

(もっと読む)

情報処理装置

【課題】汎用性があり、トレースメモリに対するアクセス制御を行うことが可能な情報処理装置を提供することを目的とする。

【解決手段】情報処理装置100は、エミュレータ120によるトレースメモリ114からのトレースデータの書き出しを制御する制御回路115を有する。制御回路115は、デバッグ用PC200からエミュレータ120を介して書き出し禁止されたアドレス部分の書き出し要求を受けると、このアドレス部分のトレースデータをすべて固定の値にして出力する。

(もっと読む)

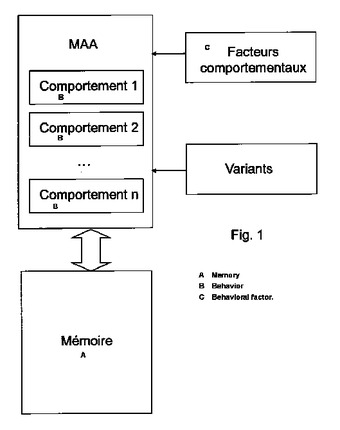

セキュリティ保護された電子システム、セキュリティ保護方法およびそのシステムの使用

本発明は、プロセッサと情報データ格納メモリとを備える電子システム、そのシステムのセキュリティ保護の方法および使用に関する。本発明によるシステムは、システムが前記メモリにそうしたデータを書き込む物理アドレスの割り当てモジュールをさらに備えており、該モジュールが変異子によって多様化されたヒューリスティックに従って前記アドレスを割り当てることができることを特徴とする。本発明は、特に、ハードウェアまたはソフトウェアによる攻撃に対する量産オンボードシステムのセキュリティ保護に適用される。  (もっと読む)

(もっと読む)

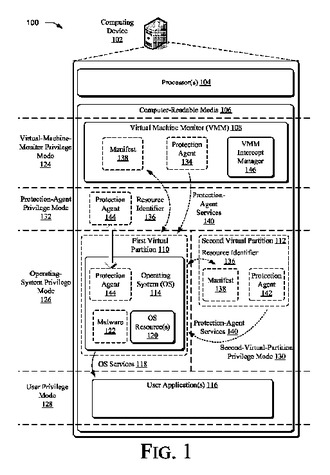

保護エージェント及び特権モード

本明細書は、保護エージェントに付随するオペレーティングシステムメモリの一部をオペレーティングシステム特権モードから変更できなくするかまたはアクセスできなくすることができるツールを開示する。いくつかの実施形態では、これらのツールは、バーチャルマシンモニタがオペレーティングシステムメモリの当該部分を保護することを要求することにより、保護エージェント特権モードを生成することができる。他の実施形態では、これらのツールは、物理プロセッサを複数の仮想プロセッサに仮想化することにより、保護エージェント特権モードを生成することができる。複数の仮想プロセッサのうちの少なくとも1つは、保護エージェントを実行するように設計された保護エージェント仮想プロセッサである。オペレーティングシステムメモリの当該部分を、オペレーティングシステム特権モードから変更できなくするかまたはアクセスできなくすることによって、保護エージェントを、オペレーティングシステム特権モードにおいて動作するエンティティによる攻撃に対して強くすることができる。  (もっと読む)

(もっと読む)

情報処理装置

【課題】プロセッサが仮想化サポート機能を有するか否かにかかわらず、安全性を向上させる。

【解決手段】HV保護領域の全てのアクセス先にアクセス可能なハイパーバイザを記憶する保護メモリと、HV保護領域のうち全てのアクセス先より狭い範囲となるアクセス先にアクセス可能なソフトウェアと、ハイパーバイザと、を動作させるプロセッサと、保護メモリとプロセッサとを接続する通信路と、プロセッサが通信路を介して保護メモリのハイパーバイザが格納されたエントリ部のアドレスに対するフェッチを検出する検出部と、当該フェッチを検出の有無に応じてアクセス先を制御する第1及び第2HV領域保護回路と、を備える。

(もっと読む)

電子制御装置

【課題】高速読み書きが容易に行なえる不揮発性メモリMRAMを用いた電子制御装置の安全性を向上する。

【解決手段】外部ツール108から制御プログラムが書込まれるMRAM120Aは、訂正符号付き書込回路122と復号化読出回路123と、エラー発生アドレス番号がエラーデータとして書込まれるエラーレジスタ125a・125bとを備え、エラー発生アドレスを指定して確認読出しを行なったときに依然としてエラーが発生していると重複異常判定を行なって異常報知される。MRAM120Aのプログラムメモリ領域は通常は書込禁止状態にあり、外部ツール108が接続されると禁止状態が解除される。エラーレジスタ125a・125bは書込禁止対象とならないデータメモリ領域に設けられている。

(もっと読む)

情報処理装置および方法、プログラム、並びに記録媒体

【課題】OSのメモリ保護機能を有効に活用するとともに、ユーザによる操作性を向上させることができるようにする。

【解決手段】カーネル空間131で実行され、OS101のカーネルにフックされるソフトウェアとしてエクセプションハンドラ133を設ける。OS101のカーネルが、ユーザランド空間132で実行される通常アプリケーションによる不正な処理の発生を検知した場合、カーネルからエクセプションハンドラ133に、不正な処理の発生を通知して、その後、通常アプリケーションのプロセス151を強制終了する。エクセプションハンドラ133は、プロセス151が終了された後、ユーザに、システムエラーを通知し、再起動を促すための例外アプリケーションの実行を制御し、ユーザランド空間132で例外アプリケーションのプロセス152が実行される。

(もっと読む)

保護領域境界を越えるオブジェクトの起動のための方法、システム、及び装置

【解決手段】リモートシステム呼び出しを起動し、保護メモリシステムにおけるプロセス間通信を容易にする方法、装置、システム、及びコンピュータプログラム製品は、システム呼び出しによるオブジェクトのリモート呼び出しをサポートするカーネルを使用する。このシステム呼び出しは、オブジェクト識別子と、入力及び出力バッファへのポインタのセットを含み得る。カーネルは、分離されたサーバプロセス領域内で特定のオブジェクトを検索し、オブジェクトを起動するサーバ領域内のサーバスレッドを呼び起こす。与えられたメモリポインタを用いて、カーネルは中間バッファへのデータコピーを必要とすることなく単一のステップで、保護領域を越えて、入力及び出力データをコピー出来る。これにより、従来の保護メモリシステムで求められていた複数回のデータコピーステップのオーバーヘッドを無くすことが出来る。 (もっと読む)

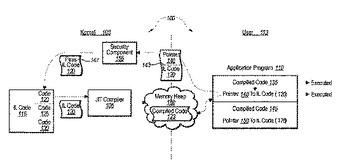

信頼性の低いアドレス空間への実行コードのコンパイル

管理されたコードを実行する安全でないアプリケーションプログラムが、安全な仕方で実行される。特に、オペレーティングシステムは、アプリケーションプログラムをユーザーモードで実行するが、カーネルモードで動作する型安全なJITコンパイラを介して、管理されたコードのコンパイルを処理するように構成される。オペレーティングシステムは、また、単一のメモリロケーションが、異なる許可セットを使用して、複数のアドレス空間を介してアクセスされることも指定可能である。ユーザーモードで動作するアプリケーションプログラムは、読み取り/実行アドレス空間で実行されうるが、JITコンパイラは、読み取り/書き込みアドレス空間で実行されうる。中間言語コードへの1つまたは複数のポインタに遭遇した場合、アプリケーションランタイムは、1つまたは複数のコンパイル要求を、その要求を検証するカーネルモードのセキュリティ構成要素に送出できる。要求が検証されると、JITコンパイラは、要求された中間言語コードをコンパイルし、アプリケーションプログラムは、共有メモリヒープからコンパイルされたコードにアクセスできる。  (もっと読む)

(もっと読む)

共有メモリ管理装置及び該装置を備えたマルチプロセッサシステム

【課題】マルチプロセッサシステムにおける共有メモリ上のデータを確実に保護しながら共有メモリの効率的な利用を可能とする共有メモリ管理装置を備えたマルチプロセッサシステムを提供すること。

【解決手段】複数のプロセッサ10〜13が共有するメモリ4を備えるマルチプロセッサシステム100は、メモリ4の所定領域40〜43に対する各プロセッサのアクセス権限に関する情報を保持するアクセス権限情報保持手段21とアクセス権限に関する情報に基づいて各プロセッサによるメモリ4へのアクセスを管理するメモリ管理手段20とを備える。また、メモリ4の所定領域は、複数のプロセッサからのアクセスを許容する。

(もっと読む)

情報処理装置及び情報処理方法

【課題】外部デバイスを用いた所定の処理を行うためのCPUのオーバーヘッドを低減する。

【解決手段】DMA C23は、外部デバイス4において、入力データの物理アドレスとして設定されたメモリ3の物理アドレスに基づいて、メモリ3からの入力データのデータ転送を行い、かつ出力データの物理アドレスとして設定されたメモリ3の物理アドレスに基づいて、メモリ3への出力データのデータ転送を行う。外部デバイス4は、所定の処理の対象データの仮想アドレスに対応する物理アドレスをMMU11から取得し、所定の処理の結果データの仮想アドレスに対応する物理アドレスをMMU11から取得する。外部デバイス4は、取得された対象データの物理アドレスと結果データの物理アドレスとを、それぞれ入力データの物理アドレスと出力データの物理アドレスとして設定する。

(もっと読む)

仮想化システム、メモリ管理方法及び制御プログラム

【課題】同一のOSを実行するドメインを複数起動した場合のメモリの使用効率を向上させることを可能にする。

【解決手段】OS310がOS未ロードのページ313に対してアクセスを行うと(S601)、ページ無効例外が発生し、当該例外に応じて、ハイパーバイザは、物理メモリ領域を1ページ分割り当て、そこにプログラムのロードを行う(S602)。二次記憶装置からOSのデータが物理メモリ410上に読み込まれると、ハイパーバイザは、ページテーブルの書き換えを行う(S603)。その後、同じページに対して、他方のOS320でアクセスがあった場合は、物理メモリ410上へのロードは行われず、既にロード済みのページフレームと、他方のOSのページとを対応付けるようにページテーブルが更新される。

(もっと読む)

101 - 120 / 211

[ Back to top ]