Fターム[5B017CA01]の内容

Fターム[5B017CA01]に分類される特許

61 - 80 / 211

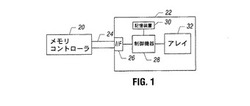

トランザクションを開始することが可能な不揮発性メモリ

【課題】 マスタ/スレーブ設定ではなく、ピアツーピア設定で動作することができる不揮発性メモリが提供される。

【解決手段】 実施形態によっては、本メモリは、メモリの外のデバイスとのトランザクションを開始することができる。従って、本メモリは、従来はメモリコントローラと他の外部デバイスとで実行されるタスクを、主体的に実行することができる。

(もっと読む)

過渡エラー制約を受ける電子システムのためのメモリアクセス監視装置

【課題】過渡エラー制約を受ける電子システム用の処理手法を提案し、過渡エラーの様相を検出し、それらを修正することである。

【解決手段】本発明は、過渡エラー制約を受ける電子システムの処理手順に関し、単一物理チャネルにある二つの仮想チャネルが所定のリアルタイムサイクルでタイミングよく多重化され(使用の前に票決できるように、仮想チャネルの各実行から生じるデータは記憶されている)、エラーが検出された場合には、処理中のリアルタイムサイクルは禁止され、再ロードされたコンテキスト始まる次のサイクルの仮実行からなる再開始を行うように異常のないコンテキストが再ロードされる。本発明は、また、メモリアクセスの監視装置にも関する。

(もっと読む)

画像処理装置

【課題】OSのオーバーヘッドを少なくすることができ、アクセス違反によるデータ破壊を抑制することができる画像処理装置を提供する。

【解決手段】この画像処理装置1は、システムメモリ7と、複数のタスクに対応してシステムメモリ7上に連続して設定された複数のスタック領域に対応する仮想アドレスを、仮想アドレス領域に離散的にマッピングする仮想アドレス離散配置手段62と、仮想アドレスと物理アドレスとを対応付けるとともにメモリアクセス違反が検知するメモリ管理手段64と、画像処理用アプリケーションによるメモリアクセス違反が検知されたとき、メモリアクセス違反を履歴情報として不揮発性記憶部8に保存する履歴情報保存手段66とを備える。

(もっと読む)

画像処理装置

【課題】OSのオーバーヘッドを少なくすることができ、アクセス違反によるデータ破壊を抑制するとともに、アクセス違反の再発防止が可能な画像処理装置を提供する。

【解決手段】この画像処理装置1は、システムメモリ7を初期化する際、不揮発性記憶部8に保存されているメモリアクセス違反の履歴情報を参照して前回メモリアクセス違反を発生したタスクに係るスタック領域の仮想アドレスを仮想アドレス領域の空き領域に拡張するメモリ資源初期化手段を備える。

(もっと読む)

画像処理装置

【課題】アクセス違反が発生する度に例外処理を行う構成と比べて、アクセス違反によるシステムダウンを減らすことができる画像処理装置を提供する。

【解決手段】この画像処理装置1は、メモリアクセス違反を発生したアプリケーション上の位置情報のうち、無視すべき位置情報が登録された無視テーブル68と、メモリアクセス違反が検知されたとき、メモリアクセス違反を発生したアプリケーション上の位置情報が無視テーブル68に登録されていないときは例外処理を行い、無視テーブル68に登録されているときは例外処理を行わない例外処理手段65とを備える。

(もっと読む)

データ保護方法とコンピュータ装置

【課題】データのバックアップとオペレーティング・システムの復元を実行するためのデータ保護方式を提供する。

【解決手段】(a)トリガーコマンドを受信すると、ハードウェア制御モジュール(1)と通信状態にあるオペレーティング・システムブロック(4)による識別不可、読み取り不可、書き込み不可である隠れゾーン(31)内にデータを保存するようにハードウェア制御モジュール(1)を設定し、(b)ハードウェア制御モジュール(1)と直接的な通信状態にある入力装置(2)から復元要求コマンド(22)を受信すると、既定条件が満たされたとき、隠れゾーン(31)からオペレーティング・システムブロック(4)による識別可能、読み取り可能、書き込み可能な作業ゾーン(32)にデータを転送するために、復元要求コマンド(22)を実行するようにハードウェア制御モジュール(1)を設定する、ステップを有するデータ保護方法である。

(もっと読む)

プロセッサ、メモリ、コンピュータシステムおよび認証方法

【課題】低コストで、コンピュータへの不正アクセス等の不正行為を防止することのできるプロセッサを提供する。

【解決手段】演算手段と一体に形成され、第1メモリ認証用情報および第2メモリ認証用情報を保持するプロセッサ側メモリ認証用情報保持手段と、第1メモリから取得した第1メモリ認証用情報と、プロセッサ側メモリ認証用情報保持手段が保持する第1メモリ認証用情報とを比較して第1メモリを認証し、さらに第2メモリから取得した第2メモリ認証用情報と、プロセッサ側メモリ認証用情報保持手段が保持する第2メモリ認証用情報とを比較して第2メモリを認証するメモリ認証手段と、メモリ認証手段による認証結果に基づいて、第1メモリおよび第2メモリへのアクセスを制御するアクセス制御手段とを備えた。

(もっと読む)

光学的情報読取装置

【課題】セキュリティ性を向上させ得る光学的情報読取装置を提供する。

【解決手段】各導通部51〜56および締結状態検知回路24により、筐体11に締結される各ねじ41〜46の締結状態を検出するとともに、主制御回路21により、検出される各ねじ41〜46の取り外し順序が判定用順序に一致するか否かについて判定される。この判定用順序は、ステップS101の処理により異なる順序に変更されるか、開封用情報コードが読み取られることに応じてステップS107の処理により開封用順序に変更される。そして、各ねじ41〜46の取り外し順序が判定用順序に一致しないとの判定、すなわち、筐体11の不正開封であるとの判定に応じて、メモリ23の読取情報が消去される。

(もっと読む)

オペレーティングシステムおよび情報処理装置

【課題】既存システムの再利用や、既存システムの統合を容易にすることができ、各システム間の連携が高速かつ安全にできるオペレーティングシステムおよび情報処理装置を提供する。

【解決手段】マルチコアプロセッサ上で動作するオペレーティングシステムにおいて、複数のプロセッサコアを1以上のプロセッサコアからなる複数のコアユニットにグループ化して管理するようにした。また、同一のコアユニットで実行される処理単位群は、それぞれグループ化されて処理単位グループを形成するようにした。そして、1の処理単位が、当該処理単位の属する処理単位グループとは別の処理単位グループ固有のメモリ領域に対してアクセスしたときに、このアクセスが不正アクセスとして検出されるようにした。

(もっと読む)

半導体システム

【課題】システムメモリ(主メモリ部)に書き込むデータを保護することができ、データの不正な複製等を防止することが可能な半導体システムを提供することである。

【解決手段】半導体システム10Aは、保護された情報を入力し、保護の解除処理を行うことが可能な機密情報処理部15Aと、乱数を発生する乱数発生部16-1と、発生した乱数あるいは乱数を発生するためのシードを保存するバッファ部16-2又は16-2aと、前記乱数と保護すべき情報との排他的論理和の計算により、前記保護すべき情報の前記乱数による暗号化及び復元を行う排他的論理和部17と、前記排他的論理和部で暗号化された保護すべき情報を記憶する主メモリ部12と、前記主メモリに記憶した情報を前記排他的論理和回路に戻して復元させ、該復元した情報を再生部13又は14に供給するように制御する制御部11とを備えている。

(もっと読む)

ハードウェア・ベースの強制アクセス制御

【課題】 ハードウェア・ベースの強制アクセス制御の方法及び機構を提供する。

【解決手段】 ハードウェア・ベースの、データに対する命令のアクセス制御を行うためのハードウェア機構が提供される。これらのハードウェア機構は、プロセッサによって処理される命令に命令アクセス・ポリシー・ラベルを付随させ、プロセッサによって処理されるデータにオペランド・アクセス・ポリシー・ラベルを付随させる。命令アクセス・ポリシー・ラベルは命令と共に、プロセッサの1つ又は複数のハードウェア機能ユニットを介して伝えられる。オペランド・アクセス・ポリシー・ラベルはデータと共に、プロセッサの1つ又は複数のハードウェア機能ユニットを介して伝えられる。プロセッサの1つ又は複数のハードウェア機能ユニットに関連付けられた1つ又は複数のハードウェア実装ポリシー・エンジンが、命令アクセス・ポリシー・ラベル及びオペランド・アクセス・ポリシー・ラベルに基づいてデータへの命令によるアクセスを制御するのに用いられる。

(もっと読む)

セキュアメモリインターフェース

【課題】セキュアメモリインターフェースを提供すること。

【解決手段】セキュアメモリインターフェースは、セキュアモードが活性化された場合に、メモリ装置に対する欠陥注入を探知するように読出部、書込部、及びモード選択部を含む。モード選択部は、データプロセッシング部から生成されたメモリアクセス情報を使用してセキュアモードを活性化または非活性化する。従って、データプロセッシング部はメモリ装置に保存されたセキュアデータの量と位置を柔軟に指定することができる。

(もっと読む)

メモリ保護方法、情報処理装置、メモリ保護プログラム及びメモリ保護プログラムを記録した記録媒体

【課題】

メモリ上で分割された領域間の不正アクセスを抑制するとともに、当該領域間に渡る手続きの実行速度の低下を軽減させるようにした技術を提供する。

【解決手段】

プログラムによる不正アクセスからメモリを保護するメモリ保護方法は、メモリ上の単一アドレス空間を複数の領域に分割する領域定義処理工程と、分割された領域間に渡るプログラムの手続きの呼び出しに際して、分割された領域を一時的に結合させる結合処理工程と、領域が結合された後、手続きを呼び出す処理工程と、呼び出された手続きの実行の終了後、結合された領域を該結合前の状態に戻す復帰処理工程とを含む。

(もっと読む)

高速RAM内に格納したプログラムのプロテクト方式

【課題】高速RAM内のプログラム格納領域にデータが誤ってライトされないようにして当該プログラムを保護し、高速RAM内のプログラム実行で制御動作速度の向上化を図る一方で、そうした場合の動作信頼性の維持ないし向上を図ること。

【解決手段】本方式は、高速RAM7上でプログラムを格納したプログラム格納領域のアドレスをFPGA8に記憶させる。FPGA8は、CPU4からのライト信号WRによりライトが行われる高速RAM7内のアドレスと、上記記憶した上記プログラム格納領域のアドレスとを比較し、上記両アドレスが、不一致のときはライト信号WRに対応するライト信号WR0により高速RAM7にライトを行う一方、一致するときはライト信号WR0を高速RAM7に出力させないようにしてプログラム格納領域内のプログラムをプロテクトする。

(もっと読む)

アクセス制限回路

【課題】従来よりも小規模な構成で、メモリ資源に格納されているデータを秘匿する。

【解決手段】比較部138は、初期属性レジスタ132Aにアクセス禁止属性の空間として保存された全アドレス空間に対して、任意の時点で改変不能にすることができるハードウェアで実装されたアクセス制限ハードレジスタ133に保存された範囲をアクセス許可属性の空間の範囲として設定し、さらに、このアクセス許可属性の空間の範囲内で、適宜改変することができるソフトウェアで実装されたアクセス制限ソフトレジスタ144に保存された範囲をアクセス禁止属性の空間の範囲として設定することによって、アクセス可能なアドレスの範囲を設定し、アクセス信号が指定するアドレス空間とアクセス可能なアドレスの範囲とを比較して、アクセス信号が指定するアドレス空間がアクセス可能なアドレスの範囲内にある場合に、アクセス信号をメモリ資源へ出力する。

(もっと読む)

セキュアプロセッサ

【課題】実行中の命令によってデータや実行コードの暗号化/復号に用いるべき鍵を選択可能とする。

【解決手段】命令を実行する命令実行手段と、該命令実行手段からのコマンドに対応して外部のメモリに対するデータのロード/ストアを制御するロード/ストア制御手段と、該ロード/ストア制御手段と外部のメモリとの間でデータの暗号化/復号化を行う暗号処理手段とを備える。前記命令実行手段は、実行中の命令又は実行中の命令によるデータ/命令フェッチのアクセスアドレスに対応して、該暗号処理手段に対してデータ暗号化/復号化に使用すべき鍵を指定する。

(もっと読む)

プロセッサ

【課題】レジスタに保持されるアドレス情報及び属性情報の一部を組み合わせ回路により予め定数値として設定することにより、回路規模を削減し、設定のタイミングの制御を容易にし、かつ、消費電力を低減する。

【解決手段】プロセッサ1は、バス13に接続されるプロセッサコア11aと、プロセッサコア11aに設けられ、バス13を介してメモリへアクセスするときにおけるメモリのアドレス及びプロセッサコア11aにおいて実行されるプログラムの命令の属性を監視し、予め設定されたアドレス及び属性との比較を行い、一致しないときに、プロセッサコア11aに例外の発生を通知するユニットであって、予め設定されたアドレスと属性の一部は、プロセッサコア11aを介してレジスタに設定され、予め設定されたアドレスと属性の他の一部は、組み合わせ回路により出力されるメモリ保護装置12aとを有する。

(もっと読む)

マルチコアシステム

【課題】高いセキュリティ性を維持しつつメモリ保護領域への各コアのアクセス権限を動的に変化させることを可能とする。

【解決手段】マルチコアシステムは、メモリの保護領域に対する各コアのアクセス権限に関する情報を保持するアクセス設定情報部と、アクセス設定情報部で保持されるアクセス設定情報に応じて各コアによるメモリの保護領域へのアクセスを制限又は許可するメモリ保護部と、アクセス設定情報部にて保持されるアクセス設定情報を変更する保護管理部と、所与の識別情報を保持する不変情報保持部とを備え、アクセス設定情報部は、保護管理部からの識別情報が不変情報保持部内の所与の識別情報と対応した場合に、アクセス設定情報への保護管理部のアクセスを許可し、保護管理部からの識別情報が所与の識別情報と対応しなかった場合に、アクセス設定情報への保護管理部のアクセスを制限する。

(もっと読む)

メモリシステムの暗号化方式

【課題】メモリシステムのデータ保護のためにデータは暗号化されている。しかしデータ暗号化の変換規則が原理的に推定でき、暗号化されたデータが解読されるという問題がある。

【解決手段】完全に非公開で、外部からは変更することだけが可能な基準キーと、データの所有者が設定する所有者キーと、基準キーと所有者キーから生成される変換キーを有し、その変換キーによってメモリデータを暗号化する。

(もっと読む)

データ保護装置及びプログラム

【課題】 処理プログラムに保護対象データの上書き処理を挿入せず、且つ利用直後の保護対象データを消去せずに、保護対象データが漏洩する可能性を低減させる。

【解決手段】 データ保護装置においては、メモリ内の保護対象データに対し、保護対象データのアドレス情報、長さ情報及びアクセス履歴情報を含む管理用情報を記憶し(ST11,ST12,ST16)、このアクセス履歴情報に基づいて、一定期間毎に保護対象データへのアクセスの有無を判定し(ST15−1〜ST15−2)、この判定の結果、アクセスが無い場合には、当該判定に用いたアクセス履歴情報を含む管理用情報内のアドレス情報及び長さ情報に基づいて、この管理用情報に対応する保護対象データをメモリから消去する(ST15−3)。

(もっと読む)

61 - 80 / 211

[ Back to top ]