Fターム[5B017CA01]の内容

Fターム[5B017CA01]に分類される特許

161 - 180 / 211

マイクロコンピュータ

【課題】内蔵不揮発性メモリプログラム又はデータの訂正を可能としながら、プログラム又はデータの読み出しに対するセキュリティ向上を図る。

【解決手段】マイクロコンピュータ100において、比較部160は内蔵不揮発性メモリ120の訂正したいアドレスを記憶する訂正アドレス記憶手段140の値とCPU110がアクセス中のアドレスとを比較する。比較結果記憶手段170は前記比較手段が出力する比較結果を記憶する。データ変換部180は、前記比較結果記憶手段が記憶する比較結果が一致の場合、内蔵不揮発性メモリ120から読み出されるプログラム又はデータを無効化する。

(もっと読む)

データ通信装置

【課題】CPUバスに暗号器や通信インタフェースやメモリがそれぞれ独立に接続している構成で、暗号化動作をする度にCPUバス上においてデータをメモリから暗号器へそして暗号器からメモリへと2回移動する必要があり、暗号化、復号化の度にバスの帯域を占有するため非効率であった。

【解決手段】通信インタフェース14と、通信インタフェースにCPUバス11を介して接続されて通信を制御するCPU12と、データを蓄積するメモリ13と、データを暗号化または復号化する暗号器15とを備える。メモリは、そのアドレス空間について、CPUがデータを直接的に読み書き可能な第1のアドレス空間と、CPUがデータを暗号器における暗号処理部15aを介して読み書き可能な第2のアドレス空間とを有し、CPUは、メモリに対してデータの読み書きを行う際に、第1のアドレス空間と第2のアドレス空間とを選択可能に構成されている。

(もっと読む)

ICチップ、ボード、情報処理装置及びコンピュータプログラム

【課題】 暗号鍵を別個に備えたセキュアモジュールで生成して、メインメモリに書き込む情報を暗号化することにより、複数のプログラム間で情報の受け渡しを行う場合であっても、受け渡しに係る情報の権利保護アルゴリズムの漏洩を防止することができるICチップ、ボード、情報処理装置及びコンピュータプログラムを提供する。

【解決手段】 内部に格納されている情報を外部から参照することができない構造であるセキュアモジュールを有するICチップをセキュリティボードに備えた情報処理装置において、セキュアモジュールは、情報を受け渡しするプログラムを実行する外部CPUから通信暗号鍵の供給を要求する暗号鍵要求信号を外部から受信し、暗号鍵要求信号を受信する都度、複数のプログラム間で受け渡しする情報を暗号化する通信暗号鍵を生成し、生成した通信暗号鍵を暗号鍵要求信号の送信元のプログラムを実行する外部CPUへ供給する。

(もっと読む)

仮想計算機の制御方法及びプログラム

【課題】権限レベルが2段階のマイクロプロセッサを用いた仮想計算機において、ゲストアプリケーションとゲストOS及びVMM間のメモリ保護を確実に行う。

【解決手段】少なくとも一つのCPUとメモリを共有して複数のプログラムを切り替えて実行する仮想計算機の制御方法であって、CPUで実行される第1のプログラムがアクセス可能なメモリ領域を規定する第1のメモリ保護テーブルを設定し、前記CPUで実行される第2のプログラムがアクセス可能なメモリ領域を規定する第2のメモリ保護テーブルを設定し、第1または第2のプログラムの実行開始を検出し(S11)、実行開始を検出した第1または第2のプログラムに対応して第1または第2のメモリ保護テーブルの何れか一方を選択して切り替えて(S17)、前記選択した第1または第2のメモリ保護テーブルを前記CPUのメモリ管理ユニットで参照し、前記選択した第1または第2のメモリ保護テーブルに規定されたメモリ領域を保護させる(S18、S19)。

(もっと読む)

プロセッサ及びシステム

【課題】 本発明は、情報を部分的に暗号化して保護すれば十分である場合に、そのような用途に適した効率的な構成のプロセッサ及びシステムを提供することを目的とする。

【解決手段】 プロセッサは、プログラムを実行する実行部と、実行部に結合されるバスと、バスに結合されるローカルメモリと、バスに結合されるDMAユニットと、バスと外部とを結合するインターフェースを含み、DMAユニットは、実行部からの命令に応じてDMA転送処理を実行し、DMA転送処理によりインターフェースを介して外部から情報を取り込み、取り込んだ情報を復号化し、復号化した情報をDMA転送処理によりローカルメモリに書き込むよう構成されることを特徴とする。

(もっと読む)

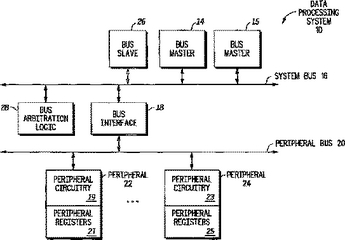

セキュリティサービスプロセッサに対する接続用バスブリッジを含むコンピュータシステム

セキュア動作モード機能付きプロセッサ(100A−B)とセキュリティサービスプロセッサ(130)との間のトランザクションをブリッジするためのバスブリッジ(121,221,321)を含むコンピュータシステム(10,20)。バスブリッジは、トランザクションソースディテクタ(450)、コンフィグレーションヘッダ(415)及び制御ロジック(416)を含んでいてもよい。トランザクションソースディテクタは、セキュリティ初期化命令の実行結果として行われたセキュリティ初期トランザクションを受けてもよい。更に、トランザクションソースディテクタは、セキュア動作モード機能付きプロセッサがセキュリティ初期化トランザクションのソースであるか否かを決定してもよい。コンフィグレーションヘッダは、セキュリティサービスプロセッサに関連付けられた情報に関するストレージを提供してもよい。制御ロジックは、コンフィグレーションヘッダに接続され、セキュリティサービスプロセッサが不可付番(non-enumerable)周辺バス(135,335)を介してバスブリッジに接続されているかどうかを決定するように構成されていてもよい。また、制御ロジックは、セキュリティサービスプロセッサが不可付番周辺バスに接続されているとの決定に応じて、ブート処理中にコンフィグレーションヘッダをアクセス可能な状態にする。  (もっと読む)

(もっと読む)

タスク管理システム

【課題】タスクの重要なデータを他のタスクからアクセスされることを防止できるタスク管理システムを提供する。

【解決手段】タスク管理システム200は、タスクが利用している重要なデータから検証子を生成する検証子生成部217と、生成された検証子を検証子記憶領域233に記憶する検証子更新部216と、検証子記憶領域233に記憶されている検証子と新たに生成された検証子とを比較検証する検証部218と、重要なデータを暗号化する暗号化部215と、暗号化された重要なデータを復号する復号部220と、タスクによる重要なデータへのアクセスを検知し遅延処理を実現するアクセス検知部219と、遅延処理を行うべきか否かを判断する処理選択部221とを備える。

(もっと読む)

秘密情報保護システム、ダンプイメージ管理サーバ及び秘密情報保護方法

【課題】ダンプイメージを提供する際、ダンプイメージに含まれる秘密情報を保護し、かつ、コストを抑制しつつ、必要に応じて十分な情報を提供することを可能にする秘密情報保護システム、秘密情報保護システムと通信するダンプイメージ管理サーバ、及び、秘密情報保護方法を提供することを目的とする。

【解決手段】秘密情報入力監視部105が、記憶領域において、秘密情報が格納されたアドレスを取得する。秘密情報周辺領域特定部141が、アドレスに基づいて、秘密情報が格納された領域である秘密情報領域を含む秘密情報周辺領域を特定し、秘密情報秘匿部142が、秘密情報周辺領域に格納されている秘密情報周辺情報を秘匿する。一方、秘密情報領域特定部154が、アドレスと、記憶領域において秘密情報が伝播する伝播ルートとに基づいて、秘密情報領域を特定し、秘密情報秘匿部155が、秘密情報領域に格納されている秘密情報を秘匿する。

(もっと読む)

情報処理装置

【課題】処理する情報の機密性を保つことができる情報処理装置を提供する。

【解決手段】本発明の情報処理装置であるプリンタ装置1は、PC2から画像データ及びジョブ情報と共にパスワードを受け付けた後、画像データを暗号化して記憶部106に記憶し、ジョブ情報にパスワードを関連づけてジョブ管理テーブルとして管理部104に記憶して処理を待機する。セキュリティプログラムが動作している場合は、主電源110が停止したときに、管理部104へ通電するバックアップ部105の動作を禁止して、管理部104が記憶しているジョブ管理テーブルを消去させる。セキュリティプログラムが動作していない場合には、バックアップ部105により管理部104へ通電して、管理部104に記憶しているジョブ管理テーブルを維持する。

(もっと読む)

コンピュータシステムのCPU(中央処理装置)

【課題】 セキュリティホールの発生原因と言われるバッファオーバーラン現象を防止し、コンピュータウイルスや不正アクセスを抑制することのできるコンピュータシステムのCPU(中央処理装置)を提供する。

【解決手段】 記憶装置のどのアドレスまで現時点で使用しているかを示し、記憶装置を使用するごとに、未使用の記憶装置のアドレスを示すように値を演算する機能を有するスタックレジスタ装置を複数備えるコンピュータシステムのCPU(中央処理装置)100であって、プログラムが使用するデータ処理に用いる第一のスタックレジスタ装置R1と、サブルーチンコールを行う際に書き込む戻りアドレスの格納に用いる第二のスタックレジスタ装置R3とを少なくとも備える。  (もっと読む)

(もっと読む)

周辺装置アクセス保護を有するデータ処理システムおよびその方法

本明細書に開示のデータ処理システム(10,100)内部の柔軟な周辺装置アクセス保護機構によって、よりセキュアな動作環境が可能となる。一実施態様では、データ処理システム(10)内部の各マスタ(14,15)には、対応する権限レベル変更子(70,74)と、特定のバス・アクセスの型(例えば、読取および書込アクセス)に対する対応する信頼属性(71,72,75,76)とが含まれる。また一実施態様では、データ処理システム(10)内部の各周辺装置(22,24)には、対応する信頼属性(80,84)、書込保護標識子(81,85)、および権限保護標識子(82,86)が含まれる。したがって、一実施態様では、バス・マスタによる周辺装置へのバス・アクセスは、周辺装置が要求する適切な権限レベルおよび適切な信頼レベルをバス・マスタが有する時(かつ、バス・アクセスが書込アクセスの場合には、周辺装置が書込保護されていない時)に許可される。また、権限レベル変更子を用いることによって、特定のバス・アクセスに対する特定の権限レベルをバス・マスタに強制することも可能である。  (もっと読む)

(もっと読む)

マイクロコンピュータ及びコンパイル方法

【課題】ロードストア型マイクロコンピュータ内部の割込処理と通常処理において、RAMを共有している場合、同時にアクセスを行っても、優先順位の高い割込処理により別処理の生成データが変更又は上書きされることなくRAMにデータストアする。

【解決手段】アドレス判定装置102は、複数の処理からアクセスされる共有アドレスエリアを有し、RAM104に格納されるアドレスが共有アドレスエリアに含まれる場合に処理優先度判定装置105へ信号を送り、処理優先度判定装置105は、アドレス判定装置102から信号を受けたとき、実行されている処理の種類に応じて優先度の高低を判定し、割込マスク制御装置108は、処理優先度判定装置105により、実行されている処理が優先度の低い処理であると判定されたとき、割込処理をマスクするように割込マスク制御装置108へ指示する。

(もっと読む)

メタデータを符号化する方法およびシステム

【課題】悪意のある攻撃、および(意図的な、あるいは意図的でない)バッファオーバーランからコンピュータを保護するシステムおよび方法を提供すること。

【解決手段】詳細には、本発明の実施形態は、データブロックのブロックヘッダの内容を保護し、ブロックヘッダの一部分が変更されているかどうかをメモリマネジャが判定する能力を可能にする。本発明の一態様によれば、複数のフィールドを有するデータを保護する方法が提供される。この方法は、複数のフィールドを少なくとも第1のグループと第2のグループにグループ化し、第1のグループの第1の識別子と第2のグループの第2の識別子を生成することを含む。また、第1のグループと第2のグループは符号化されて、それらグループのフィールドに含まれる情報を保護する。さらに、第1の識別子と第2の識別もグループの中に符号化することができる。

(もっと読む)

マルチプロセッサシステムにおいてプロセッサのセキュアな連携を行う方法および装置

【課題】メインプロセッサの管理機能の効果が低減する問題がある。

【解決手段】メインメモリ106に動作可能に接続されるとともに、それぞれがローカルメモリに関連付けられた複数のプロセッサと、プロセッサによる、メインメモリ106内のデータおよびプロセッサ内のデータに対するアクセスを制御可能な少なくとも一つのメインプロセッサ102Eと、を含むマルチプロセッサシステムにおける方法および装置を提供する。その方法および装置は、少なくとも一つのプロセッサ102Aがセキュアな動作モードに入り、メインプロセッサ102Eを用いて、複数のプロセッサのうちの前記少なくとも一つのプロセッサ102A以外の他のプロセッサとは異なる少なくとも一つの別のプロセッサ102Cに関連付けられたデータに対して、前記少なくとも一つのプロセッサ102以外の他のプロセッサがアクセスすることを禁止する。

(もっと読む)

メモリへのアクセスを制御するためのデータ処理装置および方法

【課題】処理ロジックのうちの種々の部分の間でデータを共用しなければならない場合、セキュアデータへのアクセスを規制すること

【解決手段】メイン処理ロジックは補助処理ロジックによってアクセスできる割り当てられたメモリとすべきメモリの一部を定めることができ、補助処理ロジックによる割り当てられたメモリへのアクセスを制御するためのメモリ管理ユニットが設けられる。

(もっと読む)

プログラム実行保護プロセッサ

【課題】プログラムの実行が中断された際に暗号化などの処理負荷をかけずに、タスクの実行環境を外部からの不正なアクセスから保護することができるプログラム実行保護プロセッサを提供すること。

【解決手段】タスクを実行するタスク実行手段と、タスクからの要求に応じて、復号鍵が暗号化された暗号情報を取得する暗号情報取得手段4と、暗号情報取得手段4によって取得された暗号情報を復号化し、この復号化で得られた復号鍵をもって、暗号化されたプログラムコードおよび/またはデータを復号化する復号化手段5と、タスクからの要求に応じて割り当てられ、少なくとも復号化手段5によって復号化されたプログラムコードおよび/またはデータを記憶するプライベートページを有する内部メモリ7と、タスクによる上記プライベートページへのアクセスを許可するか否かを判断するアクセス判断手段8とを備える。

(もっと読む)

制御装置

【課題】 RAM内の動作プログラムの書き換えによるCPUの誤動作を防ぐと共に、RAMを制御するコマンドの入力を抑制しない制御機器を提供する。

【解決手段】 比較回路51で、アドレス信号、制御信号からSDRAM40に対する書込保護を行うか否かを判断する。比較回路51により書込保護を行うと判断された場合には、その結果をWPACC信号414としてゲート回路52に出力する。WPACC信号414がアクティブであれば、ゲート回路52はDQMB信号412を強制的にアクティブとする。これにより、SDRAM40へのデータ書き込みを防ぐことができると同時に、SDRAM40を制御するコマンドの入力は可能となる。

(もっと読む)

セキュリティ向上のためのプログラム変換方法及びこれを用いたコンパイラプログラム

【課題】

canary値の破壊検知に基づく従来の手法では、当該値を外部から推測できる場合に、防御機能が減殺される。別の従来手法では、スタック領域のみを保護対象としているため、スタック領域外のデータを対象とした攻撃に対しては防御できなかった。

【解決手段】

配列を含む変数をスタック外の、書き込み不能領域に隣接した領域に配置する。また、スタック外の重要データに関しては、アドレスとその格納値のマッピングテーブルを用い、コードポインタなど不正な制御奪取の原因となる変数について、定義点で登録した値と使用点で確認した値が等しいか否かを確認するコードを生成することにより、不正な制御の奪取を検出する。

バッファオーバフローを利用した攻撃に対して、外部からの値の推測や、スタック上に割り当てられていないデータ領域の破壊による不正な制御の奪取を抑止することが可能となる。

(もっと読む)

メモリ保護ユニットを有するデータ処理装置

データ処理装置(100)は、データ値を記憶するメモリと、メモリ属性をメモリの部分と関連させ、かつメモリのそれぞれのアドレス範囲に対応する複数のメモリ領域を識別するメモリ保護ユニット(130)とを備える。該メモリ保護ユニットは、それぞれのメモリ領域指示子を複数のメモリ領域(150)の少なくとも1つと関連させ、メモリ領域指示子は、メモリ領域と関連したメモリ属性の組を限定するための属性フィールド(230)と、下位区分領域メンバシップ値を保持するための下位区分領域フィールド(240)とを備える。下位区分領域メンバシップ値は、メモリ属性が、メンバ下位区分領域に適用されるが、非メンバ下位区分領域には適用されないように、それぞれの下位区分領域(160−1〜160−8)がメンバ下位区分領域であるかまたは非メンバ下位区分領域であるかを、メモリ領域の複数の下位区分領域の各々に対して特定する。  (もっと読む)

(もっと読む)

メディアメモリシステム

親プロセッサアドレス変換をメディアプロセッサのアドレス変換に整合させ、複数のメディアプロセッサに別々の変換テーブル情報によって同時共有メモリアクセスを与えるための方法および装置である。詳しくは、所定メディアアプリケーションに対するページディレクトリは、メディアアプリケーションが親プロセッサおよびメディアプロセッサ上で実行されるメディアアプリケーションによって共有されるべきメモリを割り当てる場合にメディアプロセッサのページディレクトリにコピーされる。 (もっと読む)

161 - 180 / 211

[ Back to top ]