Fターム[5B018GA02]の内容

記憶装置の信頼性向上技術 (13,264) | 目的 (2,614) | エラー訂正 (431)

Fターム[5B018GA02]に分類される特許

421 - 431 / 431

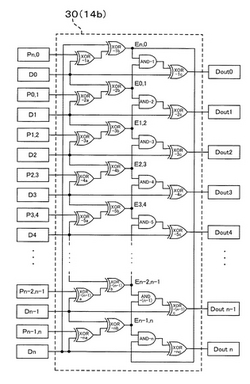

誤り訂正回路およびこれを備えた物理量センサ装置

【課題】 基板面積を削減し得る誤り訂正回路を提供する。

【解決手段】 誤り訂正回路部14bでは、隣接するデータビットD0 〜Dn および検査ビットPn,0 〜Pn-1,n に対し、誤り訂正回路30が構成されている。これにより、メモリ回路部から読み出されたトリミングデータのうち、例えば、データビットD1 がデータ化けを起こしていても、「データビットD0 、検査ビットP0,1 およびデータビットD1 の排他的論理和の結果(E0,1 )」および「データビットD1 、検査ビットP1,2 およびデータビットD2 の排他的論理和の結果(E1,2 )」の論理積と、データビットD1 と、の排他的論理和をとるので、データビットD1 は反転、つまりデータビットの誤りを訂正しDout1として出力することができる。したがって、誤り訂正回路部14bの回路配線を簡素化できるとともに回路基板上の配線パターンの引き回しの錯綜を防止するので、基板面積を削減できる。

(もっと読む)

ブロッキングなく、キャッシュ参照間に直面するビットエラーを修正する方法および装置

本発明のある実施形態は、キャッシュメモリへの参照の間に直面するビットエラーを修正するシステムを提供する。アプリケーションの実行の間に、システムは、データアイテムおよび関連するエラー訂正コードをキャッシュメモリから取り出すことによって、キャッシュメモリへの参照を実行する。次に、システムは、エラー訂正コードを取り出されたデータアイテムから計算し、計算されたエラー訂正コード関連するエラー訂正コードと比較する。計算されたエラー訂正コードが関連するエラー訂正コードと整合しない場合、ビットエラーが生じる。この場合、システムは、ビットエラーが後の時間に修正され得るように、キャッシュメモリと関連する1つ以上のレジスタのセット内のあるレジスタに参照の識別子を格納する。このシステムはまた、アプリケーションが実行し続けることを可能にする。  (もっと読む)

(もっと読む)

フラッシュメモリ装置における内部プログラミング中の同時の外部読出動作

メモリ装置(301)の内部のプログラミング中に同時に外部の読出動作を実行するためのシステム(300)および方法が記載される。メモリ装置は、データをランダムに記憶するように構成されており、かつ、ソース場所(305)と、宛先場所(303)と、データレジスタ(307)と、キャッシュレジスタ(309)とを含む。データレジスタ(307)は、データを宛先(303)およびキャッシュレジスタ(309)に同時に書込むように構成される。システム(300)はさらに、メモリ装置との電気的な通信を介して受信したデータの的確さを検証するための処理装置(107)(たとえば、マイクロプロセッサまたはマイクロコントローラ)を含む。処理装置(107)はさらに、受信したデータが不正確であった場合、誤り訂正を行ない、必要に応じてそのデータにランダムデータを追加し、誤り訂正済みおよび/またはランダムデータ変更されたデータを宛先場所(303)に転送して戻すように構成される。  (もっと読む)

(もっと読む)

メモリコントローラ、フラッシュメモリシステム及びフラッシュメモリの制御方法

【課題】 フラッシュメモリシステムにおけるエラー検出及び訂正の能力を高める。

【解決手段】 複数のチップで構成されたフラッシュメモリ2に対し、コントローラ3は、互いに異なるチップ内のブロックを関連付け、関連付けられた複数のブロックを共通のグループとして取扱い、そのグループ内の1ブロックを、他のブロックに書込まれたユーザデータのパリティーデータを書込むパリティーデータ用ブロックに割当て、ユーザデータとパリティーデータとを書込む。そして、パリティーデータに基づいてユーザデータのエラー検出及びその訂正を行う。

(もっと読む)

情報処理装置におけるエラー訂正、検出装置

【課題】従来、ASICに接続されるDIMMの個数が多くなればなるほどPIN数が増えるので、ASICのLSIのサイズが大きくなりLSIのコストが高くなっていた。

【解決手段】第1のASIC群の各ASIC5、6は第1のASIC群内でECCの塊を作成しライトデータに対するECCコードの発生及びECCコードのライトデータへの付加機能とECCコード付きライトデータを第2のASIC群の各ASIC7、8へ振り分ける機能とDIMMからのリードデータに対するECCチェック及びECC訂正機能とを有し、第2のASIC群の各ASIC7、8はDIMMの制御を行う機能と、第1のASIC群で発生させたECCの塊がDIMMの中の同じ素子にアクセスしないようにライトデータの並替を行う機能と、DIMMからのリードデータに対しライト時に並替たデータを元に戻す機能を有し、各機能で1バイト誤り訂正又は2バイト誤り検出可能にした。

(もっと読む)

電子回路における誤り訂正

電子回路は、メモリセルのマトリクス等のデータ生成回路(12)を有している。キャプチャ回路(14)は、データ生成回路(10)に結合される入力を有しており、データ生成回路の選択部がキャプチャ回路の入力を駆動することを許容した後にデータ信号をキャプチャする。誤り検出回路(15)は、キャプチャされたデータ信号中の誤り(エラー)を検出する。特定のデータ信号中の誤りの検出に応じて、誤り検出回路は、特定のデータ信号の再キャプチャを引き起こし、それにより、データ生成回路(10)は、再キャプチャまで、第1の時間間隔よりも長い継続時間を有する第2の時間間隔に亘って、キャプチャ回路(14)の入力においてデータ信号を駆動することを許容される。これにより、広がりに起因して生じ得る最悪の場合の駆動速度に相当するように設定される継続時間を使用することなく、回路部分(例えばメモリセル)の平均駆動速度を可能にする第1の時間間隔の継続時間を選択することができる。広がりによって引き起こされる誤り(エラー)は、キャプチャ回路の入力を駆動するための増大された時間間隔をもって読み取ることにより訂正される。好ましくは、第1の時間間隔の継続時間は、平均して所定の誤り率が生じるように調節される。  (もっと読む)

(もっと読む)

メモリカード及びデータ処理装置並びにメモリカードの制御方法及び設定方法

メモリカード(1)は、データ処理装置(50)との間でコマンドやデータの送受信を行うホストインタフェース(2)と、データを格納する不揮発性メモリ(7)と、メモリカードの動作を制御するコントローラ(3)と、所定の管理情報を格納する記憶手段(32)とを備える。管理情報は、不揮発性メモリへの書き込み動作時にエラーが発生したときにリトライ機能を実行するか否かを指定するためのリトライ設定情報を含む。コントローラ(3)は、データ書き込み動作時に、リトライ設定情報を参照し、リトライ設定情報がリトライ機能の停止を示す場合は、データ書き込み動作時のエラー発生時にリトライ機能を動作させないように、また、リトライ設定情報がリトライ機能の作動を示す場合は、データ書き込み動作時のエラー発生時にリトライ機能を動作させるように、書き込み動作を制御する。 (もっと読む)

フラッシュメモリシステムの起動動作

不揮発メモリシステムの動作を制御するためのファームウエアコードの複数のコピーがメモリシステムのフラッシュメモリの適宜異なる位置に記憶される。これらの位置のアドレスマップもフラッシュメモリに記憶される。メモリシステムが初期化されると、アドレスマップを参照し、ファームウエアの1つのコピーをフラッシュメモリからコントローラメモリにロードするために、メモリコントローラに記憶されているブートコードがそのマイクロプロセッサによって実行され、その後、ユーザデータを記憶し、検索するためにメモリシステムを動作させるようにコピーがコントローラメモリからマイクロプロセッサによって実行されてもよい。データをチェックするために誤り訂正符号(ECC)が使用されるが、ECCを使用する必要性を少なくするため、フラッシュメモリに記憶されている2つ以上のファームウエアコピーの最良部分が使用される。ユーザデータが同じメモリに2つ以上の状態で記憶される場合には、ファームウエアコードが2つの状態でフラッシュメモリに記憶されてもよい。  (もっと読む)

(もっと読む)

ディスクアレイ内の2つのディスク故障に対する保護を提供する一様で対称な二重故障訂正技術

ストレージシステムのディスクアレイにおける2以下のディスク故障に対する保護を提供する一様で対称な二重故障訂正技術。ストレージシステムのRAIDシステムは、ディスク2台分の「冗長」情報を生成し、アレイ内に記憶する。この冗長情報(例えば、パリティ)は例えば、対角パリティセット(「対角」)及び行パリティセット(「行」)に沿った計算から導出される。具体的には、RAIDシステムは、アレイの行に沿って行パリティを計算し、アレイの対角方向に沿って対角パリティを計算する。ただし、冗長(パリティ)情報ディスクの内容は、純粋に対角冗長情報(だけを)含むディスクや、純粋に行冗長情報(だけを)含むディスクがないように相互作用する。冗長情報は対角パリティを使用して生成され、その結果が、行パリティ計算に使用される(逆もまた可能である)。  (もっと読む)

(もっと読む)

1つまたは複数のメモリモジュールを接続するハブコンポーネント

本発明は、1つまたは複数のメモリチップを、対応するメモリチップインタフェースを介して接続するためのハブチップに関する。このハブチップは、ハブチップをアドレスバスに接続するためのアドレス入力部と、別のアドレスバスに接続するためのアドレス出力部と、アドレス入力部に与えられたアドレスを用いて、接続されたメモリチップのうちの1つをアドレス指定するため、または、与えられたアドレスをアドレス出力部に与えるためのアドレス復号器ユニットとを有する。このハブチップの特徴は、与えられたチェック用データを用いて、1つまたは複数のメモリチップのメモリ領域中のエラーを検出するためのエラー認識ユニットを有する点にある。  (もっと読む)

(もっと読む)

チェックサム構築システム

【課題】 コンピュータ・システムの別々のメモリ・ユニットに格納された様々なデータ値のチェックサムを効率的に構築するシステムと方法を提供する。

【解決手段】 本発明は、複数のメモリ・ユニット、複数のメモリ・コントローラ、及び1つの標識を用いる。各メモリ・ユニットはデータ格納用の複数の記憶位置を持ち、各メモリ・コントローラはそれぞれのメモリ・ユニット内の記憶位置にアクセスするよう構成される。メモリ・コントローラの1つは、その記憶位置の1つにチェックサムを構築するよう構成され、標識は、他のメモリ・コントローラのうちチェックサムの1つの記憶位置を更新できるものを示す。チェックサム構築過程中に、様々なデータ値を格納している記憶位置へのデータ格納が可能となり、そのためコンピュータ・システムの性能に顕著な影響を与えることなくチェックサムを構築することができる。

(もっと読む)

421 - 431 / 431

[ Back to top ]