Fターム[5B018HA33]の内容

記憶装置の信頼性向上技術 (13,264) | 手段 (2,627) | タイミング関係、時間関係 (124) | 遅延 (20)

Fターム[5B018HA33]に分類される特許

1 - 20 / 20

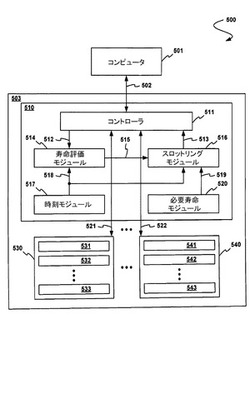

メモリの寿命を縮める動作を遅延させるシステム、方法、及びコンピュータプログラム製品

【課題】メモリの寿命を縮める動作を遅延させるシステム、方法、及びコンピュータプログラム製品を提供する。

【解決手段】メモリの寿命を縮める動作を遅延させるシステム500は、複数のストレージデバイス530、540を含むストレージシステム503が含まれている。コマンドの少なくとも一部は、寿命を縮めるコマンドであり、少なくとも一つのモジュール又はブロック531、532、533、541、542、543への悪影響を有する。使用中に、装置510は、そのような寿命を縮めるコマンドに拠らず、ストレージデバイス530、540の寿命を延ばすように働く。使用時に、メモリの寿命に関連する少なくとも一つの特徴が、特定される。このために、メモリの寿命を縮める少なくとも一つの動作が、当該特徴に基づいて遅延される。

(もっと読む)

半導体集積回路

【課題】信号の位相差の調整又はテストを高精度且つ簡略に行える半導体集積回路を提供する。

【解決手段】半導体集積回路は、書き込みストローブ生成回路、書き込みストローブ遅延回路、書き込み用遅延回路、出力データ生成回路、データ入力回路、及び、入力データ比較回路を備える。前記書き込み用遅延回路は複数の書き込みテストクロック信号を生成する。前記出力データ生成回路は、対応する前記書き込みテストクロック信号にそれぞれ同期した複数のテスト出力データを生成する。前記データ入力回路は、前記複数のテスト出力データと前記テスト書き込み用ストローブ信号とに基づいて前記メモリに書き込まれた複数のテスト書き込みデータを並列に入力する。前記入力データ比較回路は、入力された前記複数のテスト書き込みデータと前記複数のテスト出力データとの対応するもの同士を比較して、一致した前記テスト出力データを特定する。

(もっと読む)

誤り検出回路及び集積回路

【課題】メモリ等の入力対象に入力される信号の誤判定を行うのに好適な誤り検出回路を提供する。

【解決手段】集積回路1を、誤り検出回路2A〜2Cとメモリ回路3とを含み、誤り検出回路2A〜2Cを、クロック信号CKの立ち上がりエッジにおいて入力信号IN0〜INnの状態を保持し、保持した状態を示す第1信号IN_A0〜IN_Anを出力するラッチ回路21A0〜21Anと、クロック信号CKを遅延時間t1だけ遅延させる遅延回路20Aと、遅延クロック信号CK_Aの立ち上がりエッジにおいて入力信号IN0〜INnの状態を保持し、保持した状態を示す第2信号IN_B0〜IN_Bnを出力するラッチ回路21B0〜21Bnと、第1信号IN_A0〜IN_Anと第2信号IN_B0〜IN_Bnとが一致しているか否かを比較判定し、判定結果を示す第3信号COMP0〜COMPnを出力する比較回路24_0〜24_nとを含む構成とした。

(もっと読む)

データ処理装置

【課題】動作速度を向上させることが可能なECC機能付きSRAMを搭載したデータ処理装置を提供すること。

【解決手段】データRAM12は、バスクロック20に同期してデータが書き込まれる。ECC部13は、データRAM12に書き込まれるデータに基づいてECCコードを生成する。クロック微調整回路17は、バスクロック20を遅延して出力する。そして、ECCRAM15は、クロック微調整回路17によってバスクロックを遅延したECCRAMクロックに同期して、ECC部13によって生成されたECCコードが書き込まれる。したがって、ECCRAM15にECCコードを書き込むタイミングをデータRAM12にデータを書き込むタイミングよりも遅らすことができ、ECC機能付きSRAMの動作速度を向上させることができる。

(もっと読む)

ダイナミックランダムアクセスメモリチャネル制御器のパラレルトレーニング

【解決手段】

コンピュータシステムにおけるトレーニング時間及びこれに伴うブート時間を短縮化するために、多重メモリチャネルが同時にトレーニングされる。トレーニング同期器は、多重メモリチャネル制御器に対するトレーニングデータ及びパラメータを受信し、通信インタフェースを介してメモリチャネル制御器と同時に通信する複数の通信インタフェースを含む。メモリチャネル制御器は、トレーニング同期器に応答して、メモリチャネル制御器のそれぞれに結合される複数のメモリチャネルを同時にトレーニングする。

(もっと読む)

半導体試験装置

【課題】DUTから出力される複数の被測定信号をデジタル信号に変換してメモリに取り込むように構成された複数のデジタイザを有する半導体試験装置において、デジタイザ間の信号配線遅延の影響を受けずに常に同一のタイミングでデータを取り込めるようにするとともに、トリガ信号配線数の削減と、データ保存用メモリの有効利用も実現すること。

【解決手段】DUTから出力される複数の被測定信号をデジタル信号に変換してトリガ信号に基づきメモリに取り込むように構成された複数のデジタイザを有する半導体試験装置において、前記各デジタイザを駆動するクロックに対して適切なタイミング関係に位相調整されたトリガ信号を入力する共通のトリガ制御回路を設けたことを特徴とするもの。

(もっと読む)

メモリ制御装置及びその遅延量測定方法

【課題】 量産に適用されるような一般的なテスタでも遅延回路の遅延量の測定が可能なメモリ制御装置及びその遅延量測定方法を提供することを課題とする。

【解決手段】 本メモリ制御装置は、半導体記憶装置にデータを書き込むメモリ制御装置であって、入力信号を遅延させて出力する複数の遅延回路を有し、通常動作時に、前記複数の遅延回路は、互いに独立し、個々の遅延回路に入力される信号を個々に遅延して出力し、テスト動作時に、前記複数の遅延回路は、テスト用入力信号が全ての遅延回路を経由し、それぞれの遅延量の合計分だけ遅延するように接続され、遅延後の前記テスト用入力信号は、テスト用出力信号として、前記メモリ制御装置の外部に出力されていることを要件とする。

(もっと読む)

情報処理装置及びストレージシステム性能確認方法

【課題】ホストコンピュータがすべてのメディアに対して実効的なデータ記録スピード(処理速度)を確認し、ホストアプリケーションの実現可能な性能を判断できるようにする。

【解決手段】当該情報処理装置で動作させるアプリケーションで使用するシーケンスを生成し、前記シーケンスを前記情報処理装置とデータ通信可能に接続しているメディアへ送信する。そして、前記メディアによる前記シーケンスの実行時間の測定開始時及び測定終了時を受信して、前記シーケンスの実行時間を測定しスピード確認結果データを生成する。前記生成されたスピード確認結果データから、前記アプリケーションで実行可能な性能を判定する。

(もっと読む)

メモリモジュールのコントローラ及びメモリモジュールのコントローラの制御方法

【課題】受信したクロック信号及びストローブ信号のタイミングを判断して判断結果を出力する機能を有するメモリモジュールのコントローラにおいて、通常動作時と同様の構成でのループバックテストを可能とすること。

【解決手段】ライトデータ制御回路21、ストローブ制御回路11、リードデータ制御回路24、リードストローブ制御回路12、ライトデータ遅延回路22及び遅延制御部23を有し、ライトデータ遅延回路22及び遅延制御回路23は、リードストローブ制御回路12からリードデータ制御回路24に入力されるストローブ信号が、リードデータ制御回路がライトデータ制御回路21から入力されたデータ信号を保持するタイミングとなるように、信号のタイミングを遅延させる。

(もっと読む)

メモリシステム

【課題】動作信頼性を向上させるメモリシステムを提供すること。

【解決手段】データを保持可能な不揮発性のメモリセルを備えた半導体メモリ3と、バックアップ電源2と第1外部電源(電源C)とが供給されるバックアップ制御回路6とを具備し、前記バックアップ制御回路6は、前記半導体メモリ3が前記メモリセルへのデータの書き込み中に前記第1外部電源が遮断された際に前記バックアップ電源2から与えられる電圧を前記半導体メモリ3に供給し、前記書き込みが終了した後前記バックアップ電源2から与えられる前記電圧の供給を停止する。

(もっと読む)

メモリシステム

【課題】不揮発性記憶部の信号線の負荷容量が増大した場合においても、不揮発性記憶部からデータを読み出して確実に出力することが可能なメモリシステムを提供することを目的とする。

【解決手段】NAND I/F116は、RE信号を帰還させた信号をプログラムブル遅延素子220で遅延させて第2のクロックCLK2として出力し、第2のクロックCLK2を使用して、NANDメモリ10から読み出したデータをラッチして出力する。

(もっと読む)

再生機器および再生機器の記憶媒体取り外し方法

【課題】再生機器よりユーザが外部記憶媒体の取り外しを行いたい場合には、いつでも、外部記憶媒体を取り外しできる再生機器および再生機器の記憶媒体取り外し方法を提供すること。

【解決手段】データを記憶する記憶媒体10が着脱可能に接続される再生機器1であって、記憶媒体10を取り外し可能な状態にする際に操作される操作部材4aと、操作部材4aが操作された場合に、記憶媒体10との間の通信を停止する停止手段と、停止手段によって通信が停止された場合に、記憶媒体10を取り外し可能な状態になったことを報知する報知手段2と、を備える再生機器1としている。

(もっと読む)

同期メモリの読出しデータ収集

単一の読出し動作でDQSイネーブル信号の最適なタイミングを決定するスナップショットデータトレーニングの方法が提供される。先ずグレイコードカウントのシーケンスをメモリに書き込み、次いで単一のバーストでそれを読み出すことで実現する。コントローラは、コマンドが発行された時点から一定間隔で読出しバーストをサンプリングし、周回遅延を決定する。簡単な真理値表の検索により、通常読出しに対する最適のDQSイネーブルのタイミングを決定する。通常の読出し動作中、イネーブルされたDQS信号の第1のポジティブエッジを使用して、コマンドが発行されるたびにイネーブルされたカウンタをサンプリングすることが好ましい。カウンタサンプルが変化した場合、これはタイミングの変動が生じたことを示すが、DQSイネーブル信号を調整して変動を補正し、DQSプリアンブルの中央に合わせた位置に保つことができる。  (もっと読む)

(もっと読む)

インタフェース回路及びメモリ制御装置

【課題】ループバックテスト時に、実スピード動作における遅延故障検出のテストを実現するメモリ制御装置の提供。

【解決手段】出力側回路に、ノーマルモード位相シフト量制御回路23とテストモード位相シフト量制御回路25と、これら2つの位相シフト量制御回路の出力を選択するセレクタ27と、可変遅延回路6を備え、入力回路側にノーマルモード位相シフト量制御回路24とテストモード位相シフト量制御回路26と、これら2つの位相シフト量制御回路の出力を選択するセレクタ28と、可変遅延回路15を備え、ループバックしてリードデータ取り込み回路19でラッチされたリードデータ21とライトデータ20との期待値照合を行う比較回路22と、入力データのサンプリングタイミングが1エッジ分遅れた場合の期待値照合を行う第2の比較回路100を備えている。

(もっと読む)

半導体集積回路

【課題】 回路規模増大を抑制しつつ、ソフトエラーによる回路誤動作を防止可能な半導体集積回路を提供する。

【解決手段】 論理回路1と、論理回路1から出力された書き込みデータDを入力し、書き込みデータDを反転した反転データ/Dを生成し、書き込みデータDと反転データ/Dを比較し互いに異なる場合に保持した書き込みデータOUTを出力する書き込み回路10とを備える。

(もっと読む)

メモリシステムおよびメモリシステムの動作方法

【課題】 不揮発性メモリから揮発性メモリに転送が開始されてから揮発性メモリ内のデータがアクセス可能になるまでの時間を短縮する。

【解決手段】 揮発性メモリSDRAMは、不揮発性メモリFLASH用のエラー訂正コードを記憶する揮発付加領域E2を有する。不揮発性メモリFLASHに記憶されたデータをエラー訂正することなく、エラー訂正コードとともに揮発性メモリSDRAMに転送することで、不揮発性メモリFLASHから揮発性メモリSDRAMへのデータの転送時間を短くできる。この結果、不揮発性メモリFLASHから揮発性メモリSDRAMに転送が開始されてからデータがアクセス可能になるまでの時間を短縮できる。

(もっと読む)

メモリ制御装置および情報処理装置

【課題】 メモリのデータ読み出し動作とメモリ制御装置のデータ受信タイミングが合わず、正常にデータの読み出しができなくなることを防止。

【解決手段】 基準クロックを所定時間遅延させた動作クロックの供給でデータの書き込み及び読み出しを行うメモリの制御装置で、基準クロックに同期して試験データをメモリに供給するデータ供給手段と、基準クロックを設定された遅延時間だけ遅延させた読出クロックを出力する可変遅延手段と、読出クロックが供給されると、試験データを読み出すための読出制御信号を出力し、メモリより出力された試験データを受信するデータ読出手段と、読み出された試験データ及び保持された試験データの一致不一致を判定するデータ判定手段と、データ判定手段が不一致と判定すると、他の遅延時間を設定する遅延時間設定手段と、他の遅延設定されると各手段を再起動するテスト制御手段とを有する。

(もっと読む)

記憶媒体接続処理装置

【課題】 着脱可能に接続される記憶媒体へのデータの書込み中、または記憶媒体からのデータの読出し中に、ユーザが記憶媒体を不用意に取り外してしまうことを抑制することができる記憶媒体接続処理装置を提供する。

【解決手段】 CPU6が、メモリカードアダプタ9に着脱可能に接続されるメモリカード13へのデータの書込み、またはメモリカード13からのデータの読出しを実行しているとき、LEDデバイス12に第1の表示情報を表示させ、USBデバイス11に着脱可能に接続される情報処理装置14が、メモリカードアダプタ9に着脱自在に接続されるメモリカード13へのデータの書込み、またはメモリカード13からのデータの読出しを実行しているとき、LEDデバイス12に第2の表示情報を表示させることによって、ユーザに注意を促し、メモリカード13が不用意に取り外されてしまうことを抑制することできる。

(もっと読む)

半導体集積回路およびハードマクロ回路

【課題】 メモリが内蔵されたLSIにおいて、メモリの入力への経路またはメモリの出力からの経路のディレイ故障を検出するディレイテストを実施できるようにする。

【解決手段】 スキャンFF1a〜1mと、セレクタ2a〜2eと、遅延調整回路3a〜3dと、組合せ回路10a〜10cと、メモリ11と、BIST12とを有する。セレクタ2a〜2dからスキャンFF1e〜1hへの経路上に、セレクタ2a〜2dからメモリ11の入力端子への信号遅延時間と、セレクタ2a〜2dからスキャンFF1e〜1hへの信号遅延時間とが同じになるように遅延調整回路3a〜3dを備える。スキャンFF1kからセレクタ2eへの経路上に、メモリデータ出力DOUTからセレクタ2eへの信号遅延時間と、スキャンFF1kの出力からセレクタ2eへの信号遅延時間とが同じになるように遅延調整回路3eを備える。

(もっと読む)

メモリアドレスマッピングテーブルを使用するポータブルデータ記憶デバイス

ポータブルデータ記憶デバイスは、USB制御装置2と、マスター制御ユニット7と、NANDフラッシュメモリデバイス9とを含む。マスター制御ユニット7は論理アドレスに書き込まれることになるデータと、論理アドレスからデータを読み出す命令を受け取る。マスター制御ユニット7はメモリアドレスマッピングテーブルを使用して、論理アドレスをメモリデバイス9中の物理アドレスに関係付け、論理アドレスに対応する物理アドレスにデータを書き込み、または物理アドレスからデータを読み出す。物理アドレス領域の異なるものが、異なる時間において論理アドレスに関係付けられるように、マッピングは間隔をあけて変更される。このことはデバイスの速度を増加させ、データが比較的頻繁に書き込まれる論理アドレスに永続的に関係付けられることによる物理アドレスの急速な劣化が起こらないことも意味する。 (もっと読む)

1 - 20 / 20

[ Back to top ]